# **TAMC641**

# **High Performance Virtex-5 AMC with FMC Slot**

Version 1.0

# **User Manual**

Issue 1.0.6 January 2012

#### **TAMC641-10R**

XC5VLX110T-1, 512 MB DDR2, 4MB QDR-II, Mid-Size front panel

#### **TAMC641-11R**

same as TAMC641-10R but Full-Size front panel

#### **TAMC641-12R**

XC5VLX155T-1, 512 MB DDR2, 4MB QDR-II, Mid-Size front panel

#### **TAMC641-13R**

same as TAMC641-12R but Full-Size front panel

#### **TAMC641-14R**

XC5VSX95T-1, 512 MB DDR2, 4MB QDR-II Mid-Size front panel

#### **TAMC641-15R**

same as TAMC641-14R but Full-Size front panel

#### **TAMC641-16R**

XC5VFX70T-1, 512 MB DDR2, 4MB QDR-II, Mid-Size front panel

#### **TAMC641-17R**

same as TAMC641-16R but Full-Size front panel

#### **TAMC641-18R**

XC5VFX100T-1, 512 MB DDR2, 4MB QDR-II, Mid-Size front panel

#### **TAMC641-19R**

same as TAMC641-18R but Full-Size front panel

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©2011-2012 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue                  | Description                                                                                                                                                                                                                                                                                                                                                                                                 | Date          |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0.0                  | preliminary Issue                                                                                                                                                                                                                                                                                                                                                                                           | March 2011    |

| 1.0.1<br>(preliminary) | <ul> <li>corrected connector names in figure 10-1</li> <li>update of Appendix B (FPGA constraints)</li> <li>added factory default settings of the Board Config. CPLD</li> <li>revised chapter "Module Current Requirements"</li> <li>revised Power Requirements in chapter "Technical Specification"</li> </ul>                                                                                             | May 2011      |

| 1.0.2                  | <ul> <li>removed preliminary status</li> <li>added storage temperature</li> <li>added typical power requirements (blank FPGA)</li> <li>added MTBF</li> <li>revised chapter "Debug Connector" (formally named as "Debug Adapter"</li> </ul>                                                                                                                                                                  | May 2011      |

| 1.0.3                  | - added TCLKA-D to AMC Electrical Interface in chapter "Technical Specification"                                                                                                                                                                                                                                                                                                                            | June 2011     |

| 1.0.4                  | - Revised chapters "SPI-Flash" and "FPGA Configuration". Added information and warning about the relationship between indirect SPI-programming with Xilinx Impact and the FPGA Mode Pins Corrected SPI Interface Pinning in Appendix B                                                                                                                                                                      | July 2011     |

| 1.0.5                  | Update to V1.0 Rev. B:  - Changed default FPGA configuration mode to "Master SelectMap"  - Changed DIP-Switch 3 from "USER_SWITCH_CPLD" to "FPGA Configuration Source selection"  - Table with worst case FPGA Configuration Times added  - Pin assignment for (post configuration) user SPI access changed  - Chapter "Design Help" moved to the end of the document, and chapter "Troubleshooting" added. | November 2011 |

| 1.0.6                  | Correction of the interchanged DIP-Switch SW1 and SW2 descriptions. This affects:  - Table 5-12 "configuration DIP-Switch SW1-SW2 Settings" in chapter 5.11 "JTAG"  - Table 6-1 "DIP Switch" in chapter 6.2 "DIP-Switch" Samtec Part Number of the FMC Connector corrected (chapter 9.4)                                                                                                                    | January 2012  |

# **Table of Contents**

| 1 | PRODUCT DESCRIPTION                     | 8  |

|---|-----------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                 | 10 |

| 3 | HANDLING AND OPERATION INSTRUCTION      | 12 |

|   | 3.1 ESD Protection                      | 12 |

|   | 3.2 Thermal Considerations              |    |

|   | 3.3 Mid-Size Option Usage Restrictions  | 12 |

|   | 3.4 I/O Signaling Voltages              | 12 |

|   | 3.5 Voltage Limits on FMCs              | 12 |

| 4 | IPMI SUPPORT                            | 13 |

|   | 4.1 Temperature and Voltage Sensors     | 13 |

|   | 4.1.1 Sensor Locations                  |    |

|   | 4.2 FRU Information                     |    |

|   | 4.2.1 Internal Use Area                 |    |

|   | 4.2.2 Board Info Area                   |    |

|   | 4.2.3 Product Info Area                 |    |

|   | 4.2.4.1 Module Current Requirements     |    |

|   | 4.2.4.2 AMC Point-to-Point Connectivity |    |

|   | 4.2.4.3 Clock Configuration             |    |

|   | 4.2.5 Modifying FRU Records             | 18 |

| 5 | FUNCTIONAL DESCRIPTION                  | 19 |

|   | 5.1 AMC Interface                       | 21 |

|   | 5.2 FMC Interface                       | 22 |

|   | 5.2.1 VADJ                              |    |

|   | 5.3 Memory Interfaces                   |    |

|   | 5.3.1 SPI-Flash                         |    |

|   | 5.3.2 QDR-II SRAM                       |    |

|   | 5.3 DDR2 SDRAW                          |    |

|   | 5.5 GPIO                                |    |

|   | 5.6 I <sup>2</sup> C                    |    |

|   | 5.7 UART                                |    |

|   | 5.8 Multi-Gigabit Transceiver (GTPs)    |    |

|   | 5.9 Configuration                       |    |

|   | 5.9.1 Board Configuration CPLD (BCC)    |    |

|   | 5.9.2 FPGA Configuration                |    |

|   | 5.9.3 Clock Configuration               |    |

|   | 5.10 Clocks                             |    |

|   | 5.10.1 GTP Reference Clock Generator    |    |

|   | 5.11 JTAG5.12 Thermal Management        |    |

| 6 | BOARD CONFIGURATION                     |    |

| J | 6.1 Overview                            |    |

|   | 6.2 DIP-Switch                          |    |

|   | 6.3 Battery                             |    |

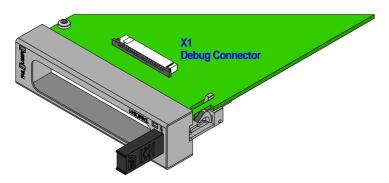

|   | 6.4 Debug Connector                     |    |

|   | 0.7 Doday Collicotol                    |    |

| 7  | INSTALLATION                                     | 40 |

|----|--------------------------------------------------|----|

|    | 7.1 Installation of a FMC Module                 | 40 |

|    | 7.1.1 Using FMCs with Mid-Size faceplates        | 40 |

|    | 7.1.2 Voltage Limits on FMC Modules              |    |

|    | 7.2 AMC Module Insertion & Hot-Swap              | 41 |

|    | 7.2.1 Insertion                                  |    |

|    | 7.2.2 Extraction                                 | 41 |

| 8  | INDICATORS                                       | 42 |

|    | 8.1 Front Panel LEDs                             | 42 |

|    | 8.2 On board LEDs                                | 42 |

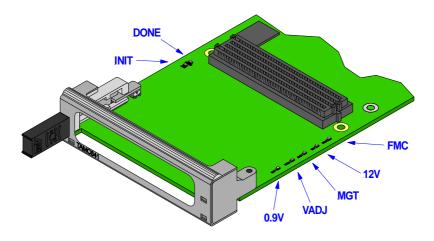

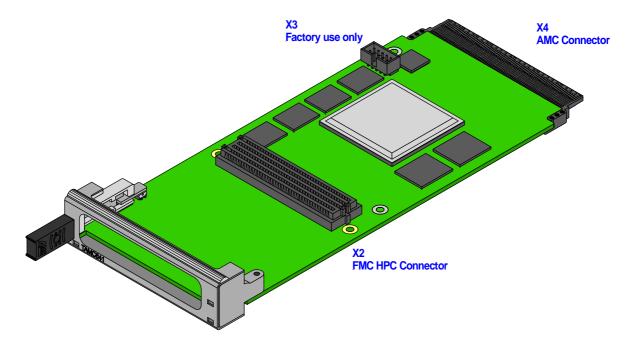

| 9  | I/O CONNECTORS                                   | 44 |

|    | 9.1 Overview                                     | 44 |

|    | 9.2 I/O Circuitry                                | 44 |

|    | 9.2.1 Differential Signaling                     | 44 |

|    | 9.3 AMC-Connector X4                             | 45 |

|    | 9.4 FMC HPC Connector X2                         | 47 |

|    | 9.5 Debug-Connector X1                           | 50 |

| 10 | DESIGN HELP                                      | 51 |

|    | 10.1 GTP Reference Clock Generator Configuration | 51 |

|    | 10.2 Example Design                              | 51 |

|    | 10.1 Troubleshooting                             | 52 |

|    | 10.1.1 Board does not power up                   | 52 |

|    | 10.1.2 DONE is always off                        |    |

|    | 10.1.3 INIT LED stays illuminated (red)          | 52 |

| 11 | APPENDIX A                                       | 53 |

| 12 | APPENDIX B                                       | 59 |

|    |                                                  |    |

# **List of Figures**

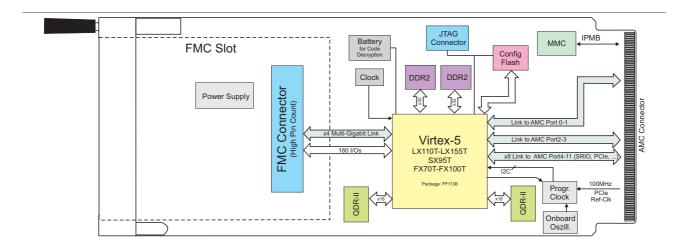

| FIGURE 1-1:  | BLOCK DIAGRAM                              | 9   |

|--------------|--------------------------------------------|-----|

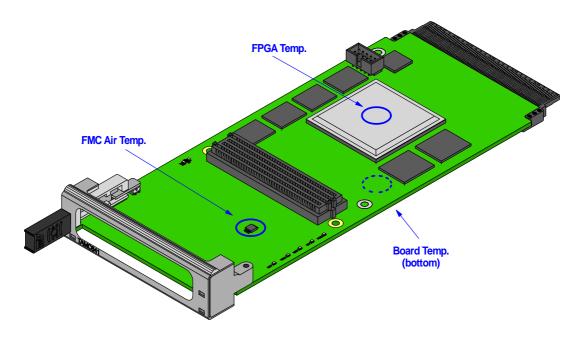

| FIGURE 4-1 : | TEMP. SENSOR LOCATIONS                     | .13 |

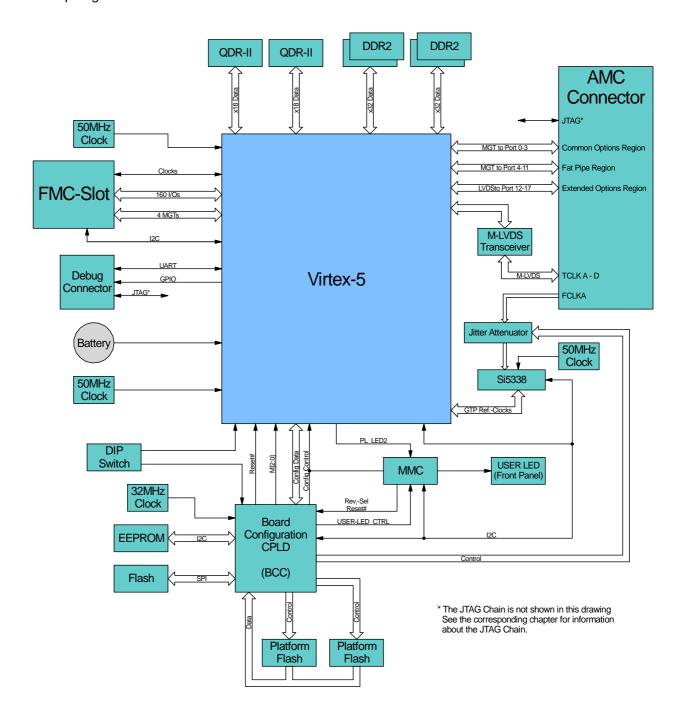

| FIGURE 5-1 : | TAMC641 FUNCTIONAL BLOCK DIAGRAM           | .19 |

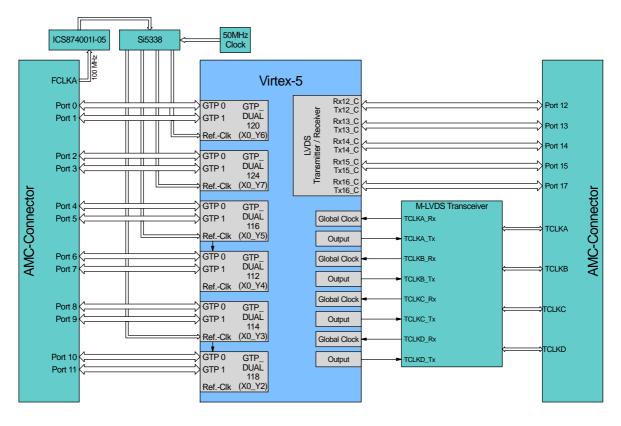

| FIGURE 5-2 : | AMC INTERFACE DIAGRAM                      | .21 |

| FIGURE 5-3 : | FMC INTERFACE TO VIRTEX-5 FPGA             | .22 |

| FIGURE 5-4 : | A FMC MODULE                               | .23 |

| FIGURE 5-5 : | QDR-II SRAM INTERFACES TO FPGA             | .24 |

| FIGURE 5-6 : | DDR2 SDRAM INTERFACES TO FPGA              | .25 |

| FIGURE 5-7 : | RESET STRUCTURE                            | .25 |

| FIGURE 5-8 : | I2C BUS STRUCTURE OVERVIEW                 | .27 |

| FIGURE 5-9:  | GTP BLOCK DIAGRAM                          | .28 |

| FIGURE 5-10: | BOARD CONFIGURATION CPLD BLOCK DIAGRAM     | .29 |

| FIGURE 5-11: | CLOCK CONFIGURATION                        | .33 |

| FIGURE 5-12: | FPGA CLOCK SOURCES                         | .34 |

| FIGURE 5-13: | JTAG-CHAIN SEGMENTATION                    | .37 |

| FIGURE 6-1 : | PRE-INSERTION BOARD CONFIGURATION OVERVIEW | .38 |

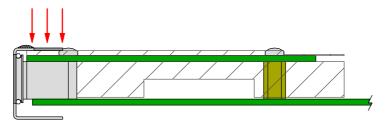

| FIGURE 7-1:  | USING FMCS WITH MID-SIZE FACEPLATES        | .40 |

|              | FRONT PANEL LED VIEW                       |     |

| FIGURE 8-2:  | ON BOARD LED VIEW                          | .42 |

| FIGURE 9-1:  | CONNECTOR POSITIONS - SIDE 1               | .44 |

| FIGURE 0-2.  | CONNECTOR POSITION - SIDE 2                | 11  |

# **List of Tables**

| TABLE 2-1: TECHNICAL SPECIFICATION                    | 11 |

|-------------------------------------------------------|----|

| TABLE 4-1: TEMPERATURE AND VOLTAGE SENSORS            | 13 |

| TABLE 4-2: FRU INFORMATION                            | 14 |

| TABLE 4-3: INTERNAL USE AREA                          | 14 |

| TABLE 4-4: BOARD INFO AREA                            | 15 |

| TABLE 4-5: PRODUCT INFO AREA                          | 15 |

| TABLE 4-6: MODULE CURRENT REQUIREMENT (W/O FMC)       | 16 |

| TABLE 4-7: AMC POINT-TO-POINT CONNECTIVITY            | 17 |

| TABLE 4-8: CLOCK CONFIGURATION                        | 17 |

| TABLE 5-1: TAMC641 FPGA FEATURE OVERVIEW              | 20 |

| TABLE 5-2: FPGA BANK USAGE                            | 21 |

| TABLE 5-3: FMC-SUPPLIES                               | 23 |

| TABLE 5-4: GENERAL PURPOSE I/O                        | 26 |

| TABLE 5-5: I2C BUS SIGNALS                            | 26 |

| TABLE 5-6: FPGA UART                                  | 27 |

| TABLE 5-7: WORST CASE FPGA CONFIGURATION TIMES        | 31 |

| TABLE 5-8: TCLK TRANSCEIVER CONFIGURATION             | 32 |

| TABLE 5-9: JITTER ATTENUATOR CONFIGURATION            | 32 |

| TABLE 5-10: AVAILABLE FPGA CLOCKS                     | 35 |

| TABLE 5-11: PROGRAMMABLE GTP REFERENCE CLOCK          | 36 |

| TABLE 5-12: CONFIGURATION DIP-SWITCH SW1-SW2 SETTINGS | 37 |

| TABLE 6-1: DIP-SWITCH                                 | 38 |

| TABLE 7-1: VOLTAGE LIMITS ON FMC MODULES              | 40 |

| TABLE 7-2: HOT-SWAP STATES                            | 41 |

| TABLE 8-1: FRONT PANEL LEDS                           | 42 |

| TABLE 8-2: BOARD-STATUS LEDS                          | 43 |

| TABLE 9-1: PIN ASSIGNMENT AMC CONNECTOR X4            | 46 |

| TABLE 9-2: PIN ASSIGNMENT FMC-CONNECTOR X2 ROW F-K    | 48 |

| TABLE 9-3: PIN ASSIGNMENT FMC-CONNECTOR X2 ROW A-E    | 49 |

| TABLE 9-4: PIN ASSIGNMENT DEBLIG CONNECTOR X1         | 50 |

# 1 **Product Description**

The TAMC641 is a standard single Mid-Size or Full-Size AMC module providing a user configurable Virtex-5 FPGA. The integrated PCIe Endpoint Block of the Virtex-5 can be used to build an x1, x4 or x8 PCIe link via AMC Port 4-11. The implementation of other protocols like SRIO or XAUI is also possible. AMC Ports 0 & 1, commonly used for Gigabit Ethernet, and AMC Ports 2 & 3 are also connected to the FPGA. The integrated Gigabit Ethernet MACs of the Virtex-5 allow fast and easy protocol implementation.

To allow direct board-to-board communication, AMC Ports 12-17 are connected to Virtex-5 I/Os, allowing AC-coupled LVDS communication with a port speed up to 1.0Gb/sec.

For flexible I/O solutions the TAMC641 provides a VITA 57.1 high pin count FMC Module slot, allowing active and passive signal conditioning. All FMC I/O lines are directly connected to the FPGA, which maintains the flexibility of the Select I/O technology of the Virtex-5 FPGA.

In addition, the FPGA is connected to the following external memories:

- two banks of DDR2 SDRAM (up to 128 M x 32 (512 MB) each)

- two banks of QDR-II SRAM (up to 4 M x 18 (8 MB) each)

Multiple clocks from the AMC-interface, the FMC and from on-board sources are supplied to the FPGA.

The FPGA is configured by a flash device, which is in-system programmable and able to store multiple code versions.

The TAMC641 supports encrypted FPGA bitstream usage. Encrypted FPGA bitstreams cannot be copied or reverse engineered, securing your intellectual property.

The IPMI Connectivity Records located inside the Module Management Controller (MMC) can be modified by the customer (e.g. via IPMI), to adapt to the different possible communication protocols (PCIe, SRIO, XAUI, ...).

User applications for the TAMC641 require the full ISE Foundation software, which must be purchased from Xilinx.

The Engineering Documentation TAMC641-ED includes all information needed for customer specific FPGA programming. The FPGA Development Kit TAMC641-FDK includes the engineering documentation, ucf-files with all necessary pin assignments and basic timing constraints, and a well documented VHDL example application. This example application is called TPLD003 (Tews Programmable Logic Design) and covers the main functionalities of the TAMC641 like DMA capable PCIe endpoint with interrupt support, register mapping, DDR2 and QDR-II memory access and basic I/O to the FMC slot. It comes as a Xilinx ISE project with source code and as a ready-to-download bitstream. It is the basis for fast and reliable customer application development, and can significantly reduce time to market.

Software support for the TPLD003 is available for all major operating systems.

In-circuit programming and debugging of the FPGA design (e.g. using Xilinx "ChipScope") is supported. The Program and Debug Box TA900 allows access to the module while it is inserted in a system. It provides access to the module's JTAG Chain, the UART of the on-board Module Management Controller (MMC) and to two user pins of the Virtex-5 FPGA. If a UART core is implemented in the FPGA, serial communication via the TA900 is possible.

The TA900 can be accessed by USB 2.0 and by a 14-pin JTAG Header (e.g. for connecting a Xilinx Platform Cable).

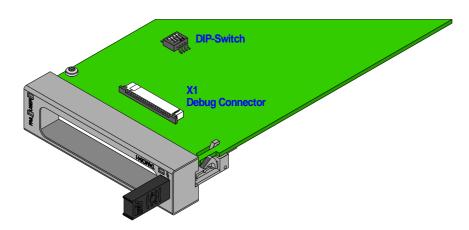

Figure 1-1: Block Diagram

# **Technical Specification**

| PICMG® AMC.0 R2.0 (Advanced Mezzanine Card Base Specification) Module Type: Single Mid-Size module or Single Full-Size module (see data sheet for order information)  Electrical Interface Virtex-5 GTPs connected to AMC port 0 - 11 Virtex-5 LVDS Transceivers connected to port 12-15 & 17 TCLKA-D connected to FPGA  IPMI  IPMI Version 1.5 Blue Hot-Swap LED Red Failure Indication LED (LED1) Green Board OK / User LED (LED2)  On Board Devices  PCIe Endpoint Virtex-5 integrated PCI Express Endpoint Block  User configurable FPGA Virtex-5 (Xillinx) XC5VLX110T, XC5VLX155T, XC5VSX95T, XC5VSX95T, XC5VFX70T or XC5VFX100T (see data sheet for order information)  Configuration Flash 2 x Xillinx XCF32P, 32 MBit each  SPI-Flash MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM 4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM 2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Connector FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks | AMC Interface                   |                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Virtex-5 LVDS Transceivers connected to port 12-15 & 17 TCLKA-D connected to FPGA  IPMI  IPMI Version  1.5  Front Panel LEDs  Blue Hot-Swap LED Red Failure Indication LED (LED1) Green Board OK / User LED (LED2)  On Board Devices  PCIe Endpoint  Virtex-5 integrated PCI Express Endpoint Block  User configurable FPGA  Virtex-5 (Xilinx) XC5VLX110T, XC5VLX155T, XC5VSX95T, XC5VFX70T or XC5VFX100T (see data sheet for order information)  Configuration Flash  PPI-Flash  MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM  4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                          | Mechanical Interface            | PICMG® AMC.0 R2.0 (Advanced Mezzanine Card Base Specification)  Module Type: Single Mid-Size module or Single Full-Size module |

| IPMI Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Electrical Interface            | Virtex-5 LVDS Transceivers connected to port 12-15 & 17                                                                        |

| Blue Hot-Swap LED Red Failure Indication LED (LED1) Green Board OK / User LED (LED2)  On Board Devices  PCIe Endpoint Virtex-5 integrated PCI Express Endpoint Block  User configurable FPGA Virtex-5 (Xilinx) XC5VLX110T, XC5VLX155T, XC5VSX95T, XC5VFX70T or XC5VFX100T (see data sheet for order information)  Configuration Flash 2 x Xilinx XCF32P, 32 MBit each  SPI-Flash MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM 4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM 2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator Si5338B (Silicon Labs)  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals 80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                      | IPMI                            |                                                                                                                                |

| Red Failure Indication LED (LED1) Green Board OK / User LED (LED2)  On Board Devices  PCIe Endpoint Virtex-5 integrated PCI Express Endpoint Block  User configurable FPGA Virtex-5 (Xilinx) XC5VLX110T, XC5VLX155T, XC5VSX95T, XC5VFX70T or XC5VFX100T (see data sheet for order information)  Configuration Flash 2 x Xilinx XCF32P, 32 MBit each  SPI-Flash MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM 4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM 2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals 80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                  | IPMI Version                    | 1.5                                                                                                                            |

| PCIe Endpoint  Virtex-5 integrated PCI Express Endpoint Block  Virtex-5 (Xilinx)  XC5VLX110T, XC5VLX155T,  XC5VSX95T,  XC5VFX70T or XC5VFX100T  (see data sheet for order information)  Configuration Flash  2 x Xilinx XCF32P, 32 MBit each  SPI-Flash  MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM  4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Front Panel LEDs                | Red Failure Indication LED (LED1)                                                                                              |

| User configurable FPGA  Virtex-5 (Xilinx)  XC5VLX110T, XC5VLX155T,  XC5VSX95T,  XC5VFX70T or XC5VFX100T  (see data sheet for order information)  Configuration Flash  2 x Xilinx XCF32P, 32 MBit each  SPI-Flash  MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM  4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | On Board Devices                |                                                                                                                                |

| XC5VLX110T, XC5VLX155T, XC5VSX95T, XC5VFX70T or XC5VFX100T (see data sheet for order information)  Configuration Flash 2 x Xilinx XCF32P, 32 MBit each  SPI-Flash MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM 4 x Micron MT47H64M16 (64M x 16)  QDR-II SRAM 2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals 80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PCIe Endpoint                   | Virtex-5 integrated PCI Express Endpoint Block                                                                                 |

| SPI-Flash  MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)  DDR2 SDRAM  4 x Micron MT47H64M16 (64M x 16)  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | User configurable FPGA          | XC5VLX110T, XC5VLX155T,<br>XC5VSX95T,<br>XC5VFX70T or XC5VFX100T                                                               |

| DDR2 SDRAM  4 x Micron MT47H64M16 (64M x 16)  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configuration Flash             | 2 x Xilinx XCF32P, 32 MBit each                                                                                                |

| QDR-II SRAM  2 x IDT 71P74804 (1M x 18)  Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SPI-Flash                       | MP25P64 (Micron) 64 Mbit (can be used for FPGA configuration)                                                                  |

| Programmable Clock Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DDR2 SDRAM                      | 4 x Micron MT47H64M16 (64M x 16)                                                                                               |

| Generator  I/O Interface  I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | QDR-II SRAM                     | 2 x IDT 71P74804 (1M x 18)                                                                                                     |

| I/O Connector  FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)  User Defined Signals  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Programmable Clock<br>Generator | Si5338B (Silicon Labs)                                                                                                         |

| User Defined Signals  Card (FMC) Standard)  80 differential or 160 single-ended I/O plus 4 differential Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I/O Interface                   |                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I/O Connector                   | FMC high pin count slot according to VITA 57.1 (FPGA Mezzanine Card (FMC) Standard)                                            |

| Multi-Gigabit-Interfaces 4 gigabit data plus 2 gigabit reference clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | User Defined Signals            | 80 differential or 160 single-ended I/O plus 4 differential Clocks                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Multi-Gigabit-Interfaces        | 4 gigabit data plus 2 gigabit reference clocks                                                                                 |

| Physical Data      |                                                                                                                                                                                                                |                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Power Requirements | Depends on FPGA design.                                                                                                                                                                                        |                                  |

|                    | 500 mA typical @ +12V DC (Payload Power, Blank FPGA)                                                                                                                                                           |                                  |

|                    | 40 mA typica                                                                                                                                                                                                   | ll @ +3.3V DC (Management Power) |

|                    | 4.7A as per Module Current Requirement Record (max.)                                                                                                                                                           |                                  |

|                    | Additional po                                                                                                                                                                                                  | wer is used by the FMC.          |

| Temperature Range  | Operating 0°C to +70°C                                                                                                                                                                                         |                                  |

|                    | Storage                                                                                                                                                                                                        | -40°C to +85°C                   |

| MTBF               | 304000 h                                                                                                                                                                                                       |                                  |

|                    | MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C.                                                                            |                                  |

|                    | The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                                  |

| Humidity           | 5 – 95 % non-condensing                                                                                                                                                                                        |                                  |

| Weight             | 190 g                                                                                                                                                                                                          |                                  |

Table 2-1: Technical Specification

# 3 Handling and Operation Instruction

#### 3.1 ESD Protection

The TAMC641 is sensitive to static electricity. Packing, unpacking and all other handling of the TAMC641 has to be done in an ESD/EOS protected Area.

#### 3.2 Thermal Considerations

Forced air cooling is recommended during operation. Without forced air cooling, damage to the device will occur.

# 3.3 Mid-Size Option Usage Restrictions

Please note that the Mid-Size module has restrictions to its usage because of a component height violation. It is within the responsibility of the user to carefully check if the Mid-Size module with its component height violation can be used in the system. Otherwise damage to the TAMC641 or the slot it is used in may occur!

Refer to the chapter "Using FMCs with Mid-Size faceplates" for details.

# 3.4 I/O Signaling Voltages

The FPGA I/O-Lines to the FMC Slot are directly connected to the FPGA I/O pins. The I/O voltage of these FPGA I/O pins is 3.3V maximum.

The FPGA I/O pins are NOT 5V tolerant.

# 3.5 Voltage Limits on FMCs

The AMC.0 specification limits the voltages on AMC modules. These limits also apply to mounted FMCs.

Refer to the chapter "Voltage Limits on FMC Modules" for details.

# 4 IPMI Support

The TAMC641 provides a Module Management Controller (MMC) that performs health monitoring, hot-swap functionality and Field Replaceable Unit (FRU) information storage. The MMC communicates via an Intelligent Platform Management Interface (IPMI) with its superordinated IPMI controller / shelf manager.

# 4.1 Temperature and Voltage Sensors

The MMC monitors on board sensors and reports sensor events to the superordinated IPMI controller / shelf manager.

| Sensor Number | Signal Type | Thresholds <sup>1</sup> | Signal Monitored       |

|---------------|-------------|-------------------------|------------------------|

| 0             | Event       | -                       | Hot-swap switch        |

| 1             | Temperature | lcr lnc unc ucr         | FPGA Temp.             |

| 2             | Temperature | Icr Inc unc ucr         | Board Temp.            |

| 3             | Temperature | lcr lnc unc ucr         | FMC Air Temp.          |

| 4             | Voltage     | lcr lnc unc ucr         | PWR                    |

| 5             | Voltage     | Icr Inc unc ucr         | +12V (FMC)             |

| 6             | Voltage     | lcr lnc unc ucr         | +5V                    |

| 7             | Voltage     | lcr lnc unc ucr         | V <sub>ADJ</sub> (FMC) |

Table 4-1: Temperature and Voltage Sensors

#### 4.1.1 Sensor Locations

Figure 4-1: Temp. Sensor Locations

<sup>&</sup>lt;sup>1</sup> unr: upper non-recoverable, ucr: upper critical, unc: upper non-critical lnc: lower non-critical, lcr: lower critical, lnr: lower non-recoverable

## 4.2 FRU Information

The MMC stores the module FRU information in a non-volatile EEPROM. Some of the records are writeable to allow adapting the TAMC641 to user FPGA designs. If records are modified, the user is responsible to set the affected checksums to correct values.

| Area                               | Size (in Bytes) | Writeable |

|------------------------------------|-----------------|-----------|

| Common Header                      | 8               | no        |

| Internal Use Area                  | 72              | yes       |

| Chassis Info Area                  | 0               | no        |

| Board Info Area                    | variable        | no        |

| Product Info Area                  | variable        | no        |

| Multi Record Area                  | variable        | see below |

| Module Current<br>Requirements     | variable        | yes       |

| AMC Point-to-Point<br>Connectivity | variable        | yes       |

| Clock Configuration                | variable        | yes       |

Table 4-2: FRU Information

#### 4.2.1 Internal Use Area

The TAMC641 uses the Internal Use Area to store default FMC-slot settings for the case that a module is present, but no valid FRU information is found. The value of "Fallback-Voltage for VADJ" determines what happens in this case. If the "Fallback-Voltage for VADJ" is set to 0x0000, the module won't turn on. Any other value sets VADJ to "Fallback-Voltage for VADJ" \* 10mV, as long this value is within the range defined by Minimum VADJ and Maximum VADJ. Example: 0x00FA = 250 \* 10mV = 2.5V.

| Product Information         | Value                                                             |

|-----------------------------|-------------------------------------------------------------------|

| Internal Use Format Version | 0x01                                                              |

| TEWS IUA Format-Version     | 0x01                                                              |

| Present FMC Slots           | 0x01 - FMC-slot #0                                                |

| Fallback-Voltage for VADJ   | 0x0000 – if no valid FMC-FRU is found, the TAMC641 won't turn on. |

| Minimum VADJ                | 0x0078 - 1200mV for TAMC641                                       |

| Maximum VADJ                | 0x014A - 3300mV for TAMC641                                       |

Table 4-3: Internal Use Area

The whole Internal Use Area is writeable, but if changes become necessary, only the Fallback-Voltage for VADJ should be altered.

## 4.2.2 Board Info Area

| Product Information    | Value                                                           |

|------------------------|-----------------------------------------------------------------|

| Version                | 0x01                                                            |

| Language Code          | 0x00 - English                                                  |

| Manufacturer date/time | determined at manufacturing                                     |

| Board manufacturer     | TEWS TECHNOLOGIES GmbH                                          |

| Board product name     | TAMC641                                                         |

| Board serial number    | determined at manufacturing (see board label)                   |

| Board part number      | TAMC641-xx(R)                                                   |

|                        | -xx = -10 / -11 / -12 / -13 / -14 / -15 / -16 / -17 / -18 / -19 |

Table 4-4: Board Info Area

#### 4.2.3 Product Info Area

| Product Information     | Value                                                                            |

|-------------------------|----------------------------------------------------------------------------------|

| Version                 | 0x01                                                                             |

| Language Code           | 0x00 - English                                                                   |

| Product manufacturer    | TEWS TECHNOLOGIES GmbH                                                           |

| Product name            | TAMC641                                                                          |

| Board part/model number | TAMC641-xx(R)<br>-xx = -10 / -11 / -12 / -13 / -14 / -15 / -16 / -17 / -18 / -19 |

| Product version         | V1.0 Rev. B (see board label)                                                    |

| Product serial number   | determined at manufacturing (see board label)                                    |

| Asset tag               | = Product serial Number                                                          |

Table 4-5: Product Info Area

#### 4.2.4 Multi Record Area

#### 4.2.4.1 Module Current Requirements

The "Current Draw" value holds the Payload Power (PWR) requirement of the module given as current requirement in units of 0.1A at 12V.

The AMC module announces the sum of "Current Draw" and FMC Current Requirement as current demand to the shelf manager. If the power budget for the AMC slot is smaller than this value, the shelf manager may not enable Payload power for the slot.

If required, the "Current Draw" value in the Module Current Requirements record may be modified to a value that falls within the given power budget. Make sure that the modified value still satisfies the AMC module power requirements for the actual FPGA content.

| Product Information | Value        |

|---------------------|--------------|

| Current Draw        | 0x2F (4.7 A) |

Table 4-6: Module Current Requirement (w/o FMC)

#### 4.2.4.2 AMC Point-to-Point Connectivity

The TAMC641's Virtex-5 FPGA allows implementing a wide range of interfaces (Serial RapidIO, PCI-Express, Gig.-Eth., SAS, SATA, XAUI, etc.). The MMC stores a Connectivity Record for each interface that is implemented by the TAMC641. By default, the MMC of the TAMC641 stores the following Connectivity Records:

- 2x GbE Links on AMC Ports 0-1

- 2 x SATA Links on AMC Port 2-3

- x1 2.5 Gbps PCI-Express Gen1 Link on AMC Port 4

- x4 2.5 Gbps PCI-Express Gen1 Link on AMC Port 4-7

- x8 2.5 Gbps PCI-Express Gen1 Link on AMC Port 4-11

| Channel | Port          | Link Type                 | Link Type Extension           | Link Grouping ID    | Asymmetric Match |  |

|---------|---------------|---------------------------|-------------------------------|---------------------|------------------|--|

| 0       | 0             | AMC.2 Ethernet            | 1000BASE-BX<br>Ethernet Link  | Single Channel Link | exact match      |  |

| 1       | 1             | AMC.2 Ethernet            | 1000BASE-BX<br>Ethernet Link  | Single Channel Link | exact match      |  |

| 2       | 2             | AMC.3 Storage             | Serial ATA                    | Single Channel Link | matches with 01  |  |

| 3       | 3             | AMC.3 Storage             | Serial ATA                    | Single Channel Link | matches with 01  |  |

| 4       | 4             | AMC.1 PCI                 | Gen 1 PCI Express,<br>non-SSC | Single Channel Link |                  |  |

| 4 4     |               | Express                   | Gen 1 PCI Express,<br>SSC     | Single Channel Link | matches with 10  |  |

| 5       | 4.7           | -7 AMC.1 PCI<br>Express   | Gen 1 PCI Express, non-SSC    | Single Channel Link | matches with 10  |  |

| 5       | 4-7           |                           | Gen 1 PCI Express,<br>SSC     | Single Channel Link |                  |  |

| 6       | 4.7           | AMC.1 PCI                 | Gen 1 PCI Express, non-SSC    | 0x1                 | motoboo with 10  |  |

| 0       | 6 4-7 Express |                           | Gen 1 PCI Express,<br>SSC     | OXI                 | matches with 10  |  |

| 7       | 0 11          | 8-11 AMC.1 PCI<br>Express | Gen 1 PCI Express,<br>non-SSC | 0x1                 | matches with 10  |  |

| 7       | 8-11          |                           | Gen 1 PCI Express,<br>SSC     | UXI                 |                  |  |

Table 4-7: AMC Point-to-Point Connectivity

#### 4.2.4.3 Clock Configuration

AMC FCLKA should be used as the PCI Express Reference Clock. TCLKA – D are all inputs by default, but can independently be changed to outputs.

| Clock ID | Clock Features                                                                                   | Clock Family | Clock<br>Accuracy    | Clock<br>Frequency |

|----------|--------------------------------------------------------------------------------------------------|--------------|----------------------|--------------------|

| FCLKA    | Clock Receiver,<br>connected through Jitter<br>Attenuator and<br>programmable Clock<br>Generator | PCI Express  | PCI Express<br>Gen 1 | 100 MHz nom        |

| TCLKA    | Clock Receiver                                                                                   | misc         | -                    | -                  |

| TCLKB    | Clock Receiver                                                                                   | misc         | -                    | -                  |

| TCLKC    | Clock Receiver                                                                                   | misc         | -                    | -                  |

| TCLKD    | Clock Receiver                                                                                   | misc         | -                    | -                  |

Table 4-8: Clock Configuration

# Modifying FRU Records 4.2.5 Some of the records are writeable to allow adapting the TAMC641 to user FPGA designs. If records are modified, the user is responsible to set the affected checksums to correct values.

# 5 Functional Description

This chapter gives a brief overview of the various module functions.

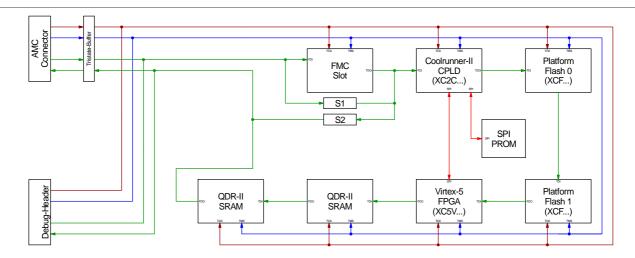

Figure 5-1: TAMC641 Functional Block Diagram

The FPGA is a Virtex-5 LX110T, LX155T, SX95T, FX70T or FX100T FPGA. Each FPGA provides four Gigabit Ethernet MACs, and one (for the LX and SX devices) or three (for the FX devices) Endpoint Blocks for PCI Express. In addition, the FX70T has one, and the FX100T two PowerPC® 440 Processor Blocks.

| Virtex-5 | Logic<br>Cells | DSP48A1<br>Slices | Block<br>RAM<br>(Kb) | CMTs | Ethernet<br>MACs | PCIe<br>Endpoints | GTP / GTX<br>Transceivers | Power<br>PCs |

|----------|----------------|-------------------|----------------------|------|------------------|-------------------|---------------------------|--------------|

| LX110T   | 110,592        | 64                | 5,328                | 6    | 4                | 1                 | 16 / -                    | -            |

| LX155T   | 155,648        | 128               | 7,632                | 6    | 4                | 1                 | 16 / -                    | -            |

| SX95T    | 94,208         | 640               | 8,784                | 6    | 4                | 1                 | 16 / -                    | ı            |

| FX70T    | 71,680         | 128               | 5,328                | 6    | 4                | 3                 | - / 16                    | 1            |

| FX100T   | 102,400        | 256               | 8,208                | 6    | 4                | 3                 | - / 16                    | 2            |

Table 5-1: TAMC641 FPGA Feature Overview

The FPGA is equipped with 18 I/O banks and 16 Multi-Gigabit Transceivers.

| I/O Bank   | V <sub>cco</sub> | $V_{REF}$        | Signals             | Remarks             |

|------------|------------------|------------------|---------------------|---------------------|

| 0          | 2.5V             | -                | Configuration       | no user I/Os        |

| 1          | VCC_B            | VREF_B_M2C       | FMC HB[17:21]       |                     |

| 2          | 2.5V             | -                | AMC Tx12 -15        | + Configuration     |

| 3          | VADJ             | VREF_A_M2C       | FMC LA[17:23]       | + 50MHz Clock       |

| 4          | 2.5V             | -                | AMC TCLK<br>FMC CLK | + AMC Tx 17         |

| 5          | 1.8V             | 0.9V             | QDR-II Bank 1       |                     |

| 6          | 1.8V             | 0.9V             | DDR2 Bank 0         |                     |

| 11         | VADJ             | VREF_A_M2C       | FMC LA[17:33]       |                     |

| 12         | 1.8V             | 0.9V             | QDR-II Bank 0       |                     |

| 13         | VADJ             | VREF_A_M2C       | FMC LA[00:16]       |                     |

| 15         | VADJ             | VREF_A_M2C       | FMC HA[00:16]       |                     |

| 17         | 1.8V             | 0.9V             | DDR2 Bank 1         |                     |

| 18         | 1.8V             | 0.9V             | DDR2 Bank 0         | + AMC Rx 12-15 & 17 |

| 19         | VCC_B            | VREF_B_M2C       | FMC HB[00:16]       |                     |

| 20         | 1.8V             | ı                | QDR-II Bank 0       |                     |

| 21         | 1.8V             | 0.9V             | DDR2 Bank 1         | + GPIO              |

| 22         | 1.8V             | 0.9V             | DDR2 Bank 0         | + GPIO              |

| 23         | 1.8V             | ı                | QDR-II Bank 1       |                     |

| 25         | 1.8V             | 0.9V             | DDR2 Bank 1         |                     |

| GTP Bank   |                  | Description      | on                  | Remarks             |

| 112 (X0Y4) | AMC Backpla      | ne, Port 6 & 7   |                     |                     |

| 114 (X0Y3) | AMC Backpla      | ne, Port 8 & 9   |                     |                     |

| 116 (X0Y5) | AMC Backpla      | ne, Port 4 & 5   |                     |                     |

| 118 (X0Y2) | AMC Backpla      | ne, Port 10 & 11 |                     |                     |

| 120 (X0Y6) | AMC Backpla      |                  |                     |                     |

| 122 (X0Y1) | FMC, DP 0 &      | 1                |                     |                     |

| 124 (X0Y7) | AMC Backplane, Port 2 & 3 |  |

|------------|---------------------------|--|

| 126 (X0Y0) | FMC, DP 2 & 3             |  |

Table 5-2: FPGA Bank Usage

All FMC I/O lines are directly connected to the FPGA-pins. Refer to the Xilinx UG190: *Virtex-5 FPGA User Guide* for SelectIO interface signal standards, slew rate control and current drive strength capabilities.

The board supports FPGA configuration via JTAG, from a Platform Flash or a SPI-Flash.

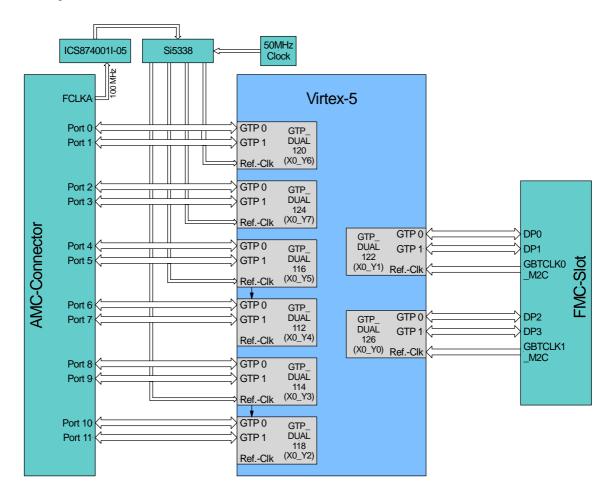

## **5.1 AMC Interface**

AMC Ports 0 – 11 are connected to Virtex-5 GTP transceivers. Ports 12-17 are connected to Virtex-5 LVDS Receivers / Transmitters. All Ports provide on board AC-coupling on the Rx and Tx lines.

FCLKA, commonly used as PCI-Express reference clock, is feed into a powerful clock distribution that allows using this clock on any FPGA GTP transceiver needed.

TCLKA – TCLKD are accessible by the Virtex-5 FPGA via M-LVDS transceivers that allow their use as inputs or outputs. All TCLKx inputs are lead on FPGA global clock buffers.

Figure 5-2: AMC Interface Diagram

# 5.2 FMC Interface

Instead of a front I/O Connector, the TAMC641 offers a FPGA Mezzanine Card (FMC) module slot. This allows a wide range of connectors to be used with the TAMC641 and customer specific I/O solutions can be easily applied.

The FMC module can adapt the TAMC641 to various I/O standards, either mechanical (connector) or electrical.

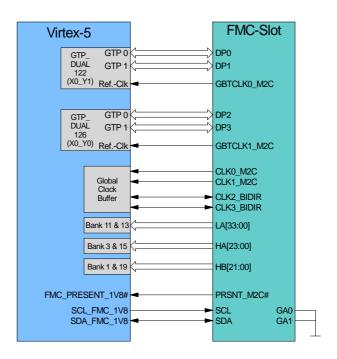

The TAMC641 implements the High Pin Count (HPC) option of the VITA 57.1 specification. It offers almost the full set of connectivity options for the High Pin Count option:

- 160 single-ended or 80 differential user defined signals

- · 4 differential clocks

- 4 GTP links

- · 2 GTP reference clock

The geographic address pins GA[0:1] are wired to a default of "00". The FMC's present signal (FMC\_PRESENT\_1V8#) and the FMC I<sup>2</sup>C bus are also connected to the FPGA.

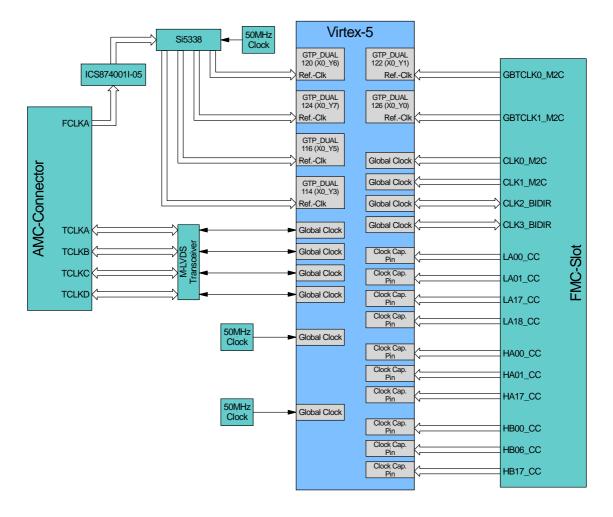

Figure 5-3: FMC Interface to Virtex-5 FPGA

Refer to chapter "X2 FMC HPC Connector" for the FMC HPC Connector pin assignment.

The TAMC641 supports the maximum current for each FMC supply, as defined for a High Pin Count module slot.

| Supply Voltage | Range                    | Max Amps |  |  |

|----------------|--------------------------|----------|--|--|

| VADJ           | 1.2V <sup>2</sup> - 3.3V | 4 A      |  |  |

| VIO_B_M2C      | 1.2V <sup>3</sup> - VADJ | 1.15 A   |  |  |

| VREF_A_M2C     | 0V - VADJ                | 1 mA     |  |  |

| VREF_B_M2C     | 0V - VIO_B_M2C           | 1 mA     |  |  |

| 3.3VAUX        | 3.3V                     | 20 mA    |  |  |

| 3.3V           | 3.3V                     | 3 A      |  |  |

| 12V            | 12V                      | 1 A      |  |  |

Table 5-3: FMC-Supplies

The FMC standard is described in: VITA 57.1, available at <a href="www.vita.com/fmc">www.vita.com/fmc</a>.

Figure 5-4: A FMC Module

#### 5.2.1 VADJ

If a FMC is present, the TAMC641 MMC reads the FRU information from the FMC's I<sup>2</sup>C-EEPROM to determine how VADJ has to be adjusted. It uses the value in the "Nominal Voltage" field of the "DC Load" record for VADJ.

If a FMC is present, but no valid FRU information is found (because the FMC EEPROM is empty or does not exist), the TAMC641 MMC uses its "Fallback-Voltage for VADJ" setting that is stored in the Internal Use Area of the TAMC641 FRU information. To avoid damage to a plugged FMC, the "Fallback-Voltage for VADJ" is set to "0x0000" by default, which means that the module will not be turned on by the MMC.

If no FMC is present, the TAMC641 is turned on, with a VADJ set to 1.8V.

$<sup>^2</sup>$  Vita 57.1 defines this voltage as 0 -3.3V. On the TAMC641, this is limited to 1.2 – 3.3V, because the FPGA I/O buffer will not work with voltages below 1.2V.

<sup>&</sup>lt;sup>3</sup> Vita 57.1 defines this voltage as 0 -VADJ. On the TAMC641, this is limited to 1.2 –VADJ, because the FPGA I/O buffer will not work with voltages below 1.2V. If HB[21:00] are not used on the FMC, this voltage can be left unconnected.

# **5.3 Memory Interfaces**

The TAMC641 is equipped with two banks of 256 Mbytes, 32 bit wide DDR2 SDRAM, two banks of 2 Mbytes, 18 bit wide QDR-II SRAM and one 64-Mbit non-volatile SPI-Flash.

#### 5.3.1 SPI-Flash

The TAMC641 provides a Numonyx M25P64 64-Mbit serial Flash memory, which can be used as FPGA configuration source. After configuration, it is accessible from the FPGA, so it also can be used for code or user data storage.

Before accessing the SPI-Flash (e.g. using Xilinx Impact), the FPGA Mode Pins must be set to "Master SPI" (factory default for V1.0 Rev. B).

If the FPGA Mode Pins are set to a slave configuration Mode (factory default of V1.0 Rev. A), damage to the device will occur during SPI programming via Impact.

See chapter "Board Configuration CPLD" for more details.

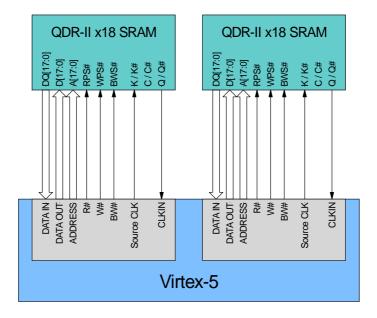

#### 5.3.2 QDR-II SRAM

The TAMC641 provides a total of 4 MByte (36 MBit) QDR-II SRAM per default (larger memories are possible).

The FPGA has access to two QDR-II SRAM devices with 2 Mbit depth at 18 bit data bus width each. Both QDR-II SRAMs have fully independent interfaces to the FPGA (see figure below).

The TAMC641 uses Burst of 4 QDR-II SRAM to lower address-bus switching speed and simultaneously achieve read and write accesses to independent addresses of the SRAM without any wait cycles.

The maximum RAM clock frequency depends on FPGA speed and available routing resources.

Figure 5-5: QDR-II SRAM Interfaces to FPGA

#### 5.3.3 DDR2 SDRAM

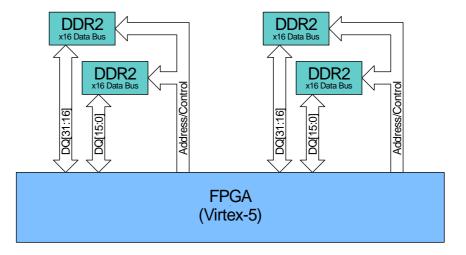

The TAMC641 provides four MT47H64M16 DDR2 memory components with a total of 512 MByte DDR2 SDRAM at 32 Bit data bus width.

Both DDR2 SDRAM banks have fully independent interfaces to the FPGA.

Figure 5-6: DDR2 SDRAM Interfaces to FPGA

For details regarding the DDR2 SDRAM interface, please refer to the DDR2 SDRAM datasheet and the Xilinx UG086: Xilinx Memory Interface Generator (MIG) User Guide.

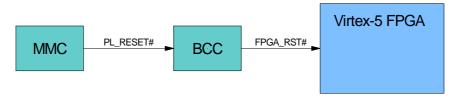

#### 5.4 Reset

The MMC generates the reset signal to the TAMC641 payload devices. It is connected to the Board Configuration CPLD (BCC) that vice versa generates the reset signal for the FPGA.

Figure 5-7: Reset Structure

# **5.5 GPIO**

The TAMC641 has some general purpose I/O connected to the FPGA and the CPLD.

| Signal                | Bank   | V <sub>cco</sub> | Pin  | Description                                                                                                                                                                                    |

|-----------------------|--------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER_SWITCH_CPLD      | 1      | 2.5V             | 49   | Select FPGA configuration source:                                                                                                                                                              |

|                       |        |                  |      | ON = 0x0 (SPI)                                                                                                                                                                                 |

|                       |        |                  |      | OFF = 0x1 (Platform Flash)                                                                                                                                                                     |

| USER_SWITCH_FPGA      | 21     | 1.8V             | Y24  | ON = 0x0, OFF = 0x1                                                                                                                                                                            |

| GPIO_FPGA             | 21     | 1.8V             | AA24 | Push-Button (not installed on board, accessible via debug-connector)                                                                                                                           |

| PL_LED2_CTRL          | 1      | 2.5V             | AA1  | Connected to MMC, pulled to MP, use as open-                                                                                                                                                   |

| (CPLD)                | (CPLD) |                  |      | collector.                                                                                                                                                                                     |

|                       |        |                  |      | When high, USER_LED is edge sensitive. When low, USER_LED is level sensitive                                                                                                                   |

| PL_LED2_1V8<br>(FPGA) | 22     | 1.8V             | AA2  | Connected to MMC, pulled to MP, use as open-collector.                                                                                                                                         |

|                       |        |                  |      | Controls the AMC "USER" front panel LED2.                                                                                                                                                      |

|                       |        |                  |      | When edge sensitive, a rising or falling edge of USER_LED triggers the MMC to turn off the USER LED in the front panel for app. 100ms. When level sensitive it directly controls the USER LED. |

Table 5-4: General Purpose I/O

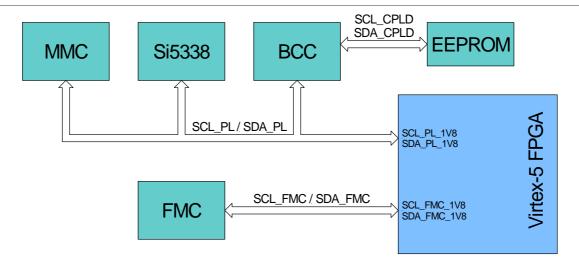

# 5.6 I<sup>2</sup>C

The TAMC641 provides two user accessible I<sup>2</sup>C busses for communication between FPGA, FMC, Board Configuration CPLD (BCC), MMC and Si5338.

| Signal      | Description                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------|

| SCL_PL      | I <sup>2</sup> C between FPGA, MMC, BCC and Si5338 (I <sup>2</sup> C communication with the MMC is for future |

| SDA_PL      | use.)                                                                                                         |

| SCL_FMC_1V8 | I <sup>2</sup> C between FMC and FPGA The I <sup>2</sup> C to the FMC allows accessing the I <sup>2</sup> C-  |

| SDA_FMC_1V8 | EEPROM on the FMC. This I <sup>2</sup> C-bus is shared with the MMC.                                          |

| SCL_CPLD    | I <sup>2</sup> C between BCC and EEPROM Only used by the BBC for clock configuration                          |

| SDA_CPLD    | data loading. User accessible after successful FPGA configuration.                                            |

Table 5-5: I2C Bus Signals

Figure 5-8: I2C Bus Structure Overview

The MMC has a slave I<sup>2</sup>C interface, while the BCC has a master only I<sup>2</sup>C interface. The BCC dedicated I<sup>2</sup>C interface is linked to SDA\_PL/SCL\_PL after successful FPGA configuration. Hence, the EEPROM can also be accessed by the FPGA.

#### **5.7 UART**

Two pins of the FPGA are routed to the Debug Connector for use as debug interface (UART). This is not a real RS-232 interface. A RS-232 transceiver or USB-UART that can work with 1.8V I/O voltage should connect with these signals. TEWS TA900 provides such an interface.

| Signal  | V <sub>cco</sub> | Description                    |

|---------|------------------|--------------------------------|

| Rx_FPGA | 1.8V             | Accessible via debug-connector |

| Tx_FPGA | 1.8V             |                                |

Table 5-6: FPGA UART

# 5.8 Multi-Gigabit Transceiver (GTPs)

The TAMC641 provides 16 GTPs (also referred to as Multi Gigabit Transceivers (MGTs), or RocketIOs):

- 12 GTPs are wired to AMC ports 0 -11 (common options and fat pipe region). FPGA hardware resources (e.g. PCI Express Endpoint Blocks or Gigabit Ethernet MACs) can be used with the GTPs connected to these lanes.

- 4 GTPs are wired to the FMC HPC connector (DP0 DP3). FPGA hardware resources like the Gigabit Ethernet MACs can be used with the GTPs connected to these lanes.

Figure 5-9: GTP Block Diagram

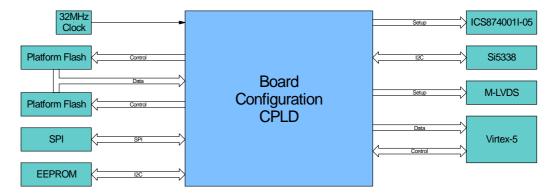

# 5.9 Configuration

The user configurable parts of the TAMC641 are the Virtex-5 FPGA, a Board Configuration CPLD (BCC), two Xilinx Platform Flashes, a SPI-Flash and the Clock Generator device (necessary for the GTP Reference-Clock generation).

The FPGA can be configured using either of the following sources:

- Platform Flash (depending on FPGA-Size, storing multiple code revisions can be possible)

- SPI-Flash

- JTAG

The configuration method is defined by the BCC (refer next chapter). Reprogramming the BCC allows (among others) adjusting different configuration methods. Alternatively, JTAG configuration is always available. On delivery, the FPGA configuration devices are blank whereas the BCC is programmed with an initial configuration.

A green on board "DONE"-LED is lit when the FPGA is configured. If the FPGA is not configured, the red front panel out-of-service status LED remains lit.

The BCC is configured via JTAG, and handles the basic board setup.

# 5.9.1 Board Configuration CPLD (BCC)

The Board Configuration CPLD (BCC) is configured via JTAG, and handles the basic board setup. This setup includes

- FCLKA jitter attenuator setup

- Configuration of the GTP Reference-Clock generation (Si5338) via I<sup>2</sup>C.

- FPGA configuration source selection (performed by controlling the FPGA mode pins circuit) and starting FPGA configuration

- TCLK[A-D] M-LVDS transceiver setup

Two Platform Flashes are available. These can be cascaded to store the configuration data for the largest FPGAs. With a smaller FPGA, it is possible to store two or more different code versions, depending on FPGA or Code size.

An I<sup>2</sup>C EEPROM is connected to the BCC. This is used to store the GTP Reference Clock configuration data. After configuration, its I<sup>2</sup>C bus is linked to the payload I<sup>2</sup>C bus to allow the FPGA accessing the EEPROM content.

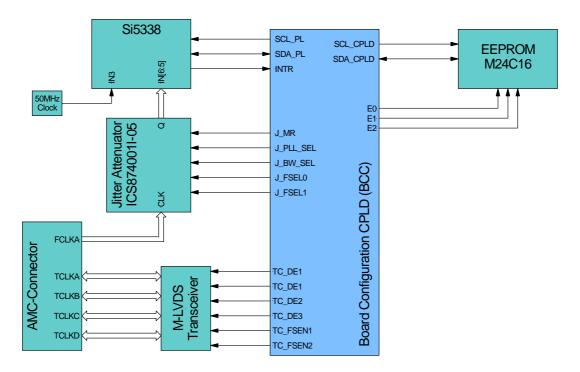

Figure 5-10: Board Configuration CPLD Block Diagram

The factory default programming of the BCC causes the following:

- MGTREFCLK\_116 (GTP-Dual Tile X0Y5) driven by FCLKA (100 MHz)

- MGTREFCLK\_114 (GTP-Dual Tile X0Y3) driven by locally generated 156.25 MHz clock

- MGTREFCLK\_120 (GTP-Dual Tile X0Y6) driven by locally generated 125 MHz clock

- MGTREFCLK\_124 (GTP-Dual Tile X0Y7) driven by locally generated 75 MHz clock

- TCLK [A-D] are configured as Type 1 Inputs

- PL\_LED2 is level sensitive

- FPGA Configuration Mode is "Master SelectMap" (fastest configuration method) or "Master SPI"

- o Configuration Source in "Master SelectMap" are the two cascaded Platform Flashes

The common power-up sequence is the following:

- 1. BCC holds PROGRAM and INIT low (delaying FPGA configuration)

- 2. BCC performs necessary Si5338 setup via I<sup>2</sup>C for GTP-Ref Clock generation.

- 3. After successful Si5338 configuration (GTP-Ref. Clocks are valid), PROGRAM followed by INIT are released to start FPGA configuration.

Configuration Source can be switched between Platform Flash and SPI-Flash by DIP-Switch 3. See chapter "Board Configuration" for more details.

After configuration, the SPI-Flash is accessible by the FPGA logic via the following pins:

| FPGA Signal              | FPGA Pin | Mapping  |

|--------------------------|----------|----------|

| IO_L4P_FCS_B_2           | AE14     | SPI CS_n |

| CCLK_0                   | N15      | SPI CLK  |

| IO_L4N_VREF_FOE_B_MOSI_2 | AF14     | SPI MOSI |

| D_IN_0                   | P15      | SPI MISO |

See also Xilinx XAPP1020 "Post-Configuration Access to SPI Flash" for more details.

# 5.9.2 FPGA Configuration