# **TAMC651**

## Spartan-6 FPGA AMC for MTCA.4 Rear-I/O

Version 1.0

## **User Manual**

Issue 1.0.2 April 2015

#### **TAMC651-10R**

XC6SLX45T-2 FPGA, 128 MB DDR3, Mid-Size front panel

#### **TAMC651-11R**

Same as TAMC651-10R but Full-Size front panel

#### **TAMC651-12R**

XC6SLX100T-2 FPGA, 128 MB DDR3, Mid-Size front panel

#### **TAMC651-13R**

Same as TAMC651-12R but Full-Size front panel

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©2015 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                                                                                                                                                                                                                                                                     | Date           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.0.0 | Initial Issue                                                                                                                                                                                                                                                                                                                                   | September 2011 |

| 1.0.1 | <ul> <li>(1) Added Power Requirements to Technical Specification Table</li> <li>(2) Added MTBF to Technical Specification Table</li> <li>(3) Some additions in Clock Signal Planning chapter</li> <li>(4) Added Note regarding µRTM EEPROM Write Protect implementation</li> <li>(5) Generic FPGA User Constraint File (UCF) updated</li> </ul> | December 2011  |

| 1.0.2 | - Added DDR3 SDRAM Alternative Part - Modified Tables in Board-I/O / Zone 3 Interface / Pin Assignment                                                                                                                                                                                                                                          | April 2015     |

## **Table of Contents**

| 1 | PRODUC                      | CT DESCRIPTION                                                | 9              |

|---|-----------------------------|---------------------------------------------------------------|----------------|

| 2 | TECHNIC                     | CAL SPECIFICATION                                             | 10             |

| 3 | HANDLIN                     | NG AND OPERATING INSTRUCTIONS                                 | 12             |

|   | 3.1 ESD                     | Protection                                                    | 12             |

|   |                             | mal Considerations                                            |                |

|   |                             | Signaling Voltages                                            |                |

| _ |                             |                                                               |                |

| 4 |                             | PPORT                                                         |                |

|   |                             | perature and Voltage Sensors                                  |                |

|   |                             | Sensor Locations                                              |                |

|   |                             | Information                                                   |                |

|   |                             | Board Info Area                                               |                |

|   |                             | Product Info Area                                             |                |

|   | 4.2.3<br>4.2.3.1            | Multi Record Area                                             |                |

|   | 4.2.3.1                     | AMC Point-to-Point Connectivity                               |                |

|   | 4.2.3.3                     | Clock Configuration                                           |                |

|   | 4.2.3.4                     | Zone 3 Interface Compatibility                                |                |

|   | 4.2.4                       | Modifying FRU Records                                         |                |

| 5 | LOCALIZ                     | 2C MANAGEMENT BUS                                             | 19             |

| J |                             |                                                               |                |

|   |                             | view                                                          |                |

|   |                             | 3us Switch                                                    |                |

|   |                             | Femperature Sensors                                           |                |

|   |                             | /O Extender                                                   |                |

| 6 | FUNCTIO                     | NAL DESCRIPTION                                               | 22             |

|   |                             | Interface                                                     |                |

|   |                             | Overview                                                      |                |

|   | 6.1.1.1                     | Point-to-Point Links                                          |                |

|   | 6.1.1.2                     | Multi-Point Links                                             |                |

|   |                             | PCI-Express Interface                                         |                |

|   |                             | king Scheme                                                   |                |

|   |                             | On-board Oscillators                                          |                |

|   |                             | AMC Backplane Clocks                                          |                |

|   |                             | PCI Express Clock Jitter Attenuator                           |                |

|   |                             | Programmable Clock Generator                                  |                |

|   |                             | Clock Crosspoint-Switch                                       |                |

|   |                             | GTP Reference Clocks                                          |                |

|   |                             | Programmable FPGA                                             |                |

|   |                             | Xilinx Documentation                                          |                |

|   |                             | FPGA Device Overview                                          |                |

|   |                             | FPGA Power Supplies and I/O Bank OverviewFPGA Pin Assignment  |                |

|   |                             | FPGA I/O Signal Description                                   |                |

|   |                             |                                                               |                |

|   |                             | Global Clock Pin Assignment                                   |                |

|   |                             | Global Clock Pin Assignment                                   |                |

|   |                             | Global Clock Pin Assignment                                   | 49             |

|   | 6.3.7<br>6.3.7.1<br>6.3.7.2 | Clock Signal PlanningGlobal Clock BufferRegional Clock Buffer | 49<br>49<br>52 |

|   | 6.3.7<br>6.3.7.1<br>6.3.7.2 | Clock Signal Planning Global Clock Buffer                     | 49<br>49<br>52 |

| 6.3.9                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         | •                                                                                                                                                                                                                                                                            |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         | ,                                                                                                                                                                                                                                                                            |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         | · ·                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 7.2.1                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 7.2.2                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 7.3 FP                  | GA Configuration Memory Programming                                                                                                                                                                                                                                          | 62                                                                                                                                                         |

| BOARD                   | ) INSTALLATION                                                                                                                                                                                                                                                               | 64                                                                                                                                                         |

| 8.1 AM                  | IC Module Installation                                                                                                                                                                                                                                                       | 64                                                                                                                                                         |

| 8.1.1                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| -                       |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| •                       |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| -                       |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         | •                                                                                                                                                                                                                                                                            |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| -                       |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.3.2                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.4 Hea                 | ader                                                                                                                                                                                                                                                                         | 69                                                                                                                                                         |

| 9.4.1                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         | •                                                                                                                                                                                                                                                                            |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.7.2                   |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.8 Zor                 |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.8.1                   | Zone 3 Mechanical Keying                                                                                                                                                                                                                                                     | 75                                                                                                                                                         |

| 9.8.2                   | Connector Type                                                                                                                                                                                                                                                               | 76                                                                                                                                                         |

|                         |                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 9.8.3                   | Pin Assignment                                                                                                                                                                                                                                                               |                                                                                                                                                            |

| 9.8.3<br>9.8.4<br>9.8.5 | Pin Assignment Signal Description Quiescence Actions                                                                                                                                                                                                                         | 78                                                                                                                                                         |

|                         | 6.3.10 6.3.11 6.4 DD 6.5 SF 6.6 Se 6.7 Zo 6.8 JT 6.9 De BOARD 7.1 OV 7.2 DIF 7.2.1 7.2.2 7.3 FP BOARD 8.1 AN 8.1.1 8.1.2 8.2 µR 8.2.1 8.2.2 BOARD 9.1 OV 9.2 LE 9.2.1 9.2.2 9.3 DIF 9.3.1 9.3.2 9.4 He 9.4.1 9.4.2 9.5 De 9.6 AN 9.6.1 9.6.2 9.7 SF 9.7.1 9.7.2 9.8 Zo 9.8.1 | 6.3.10 FPGA Configuration 6.3.11 Thermal Management. 6.4 DDR3 Memory Interface 6.5 SFP Interface 6.6 Serial SPI Flash 6.7 Zone 3 (µRTM) Interface 6.8 JTAG |

| 10 REQUIREMENTS FOR COMPATIBLE µRTM DESIGNS    | 80 |

|------------------------------------------------|----|

| 10.1 Management Functions                      | 80 |

| 10.1.1 General Notes                           |    |

| 10.1.2 Present Detection                       |    |

| 10.1.3 Power Good Detection                    | 8′ |

| 10.1.4 JTAG Signals                            | 8′ |

| 10.1.5 I2C Management Bus                      | 8′ |

| 10.1.5.1 EEPROM                                |    |

| 10.1.5.2 Temperature Sensor                    |    |

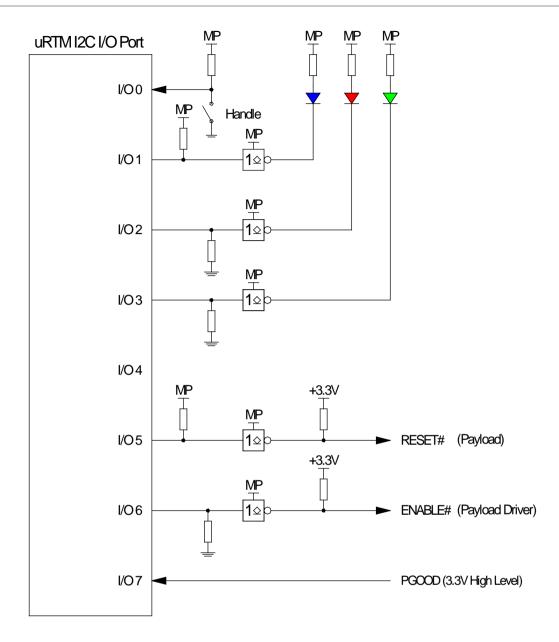

| 10.1.5.3 I2C I/O Extender                      | 82 |

| 10.1.6 µRTM FRU Information Requirements       | 84 |

| 10.1.6.1 Common Header                         |    |

| 10.1.6.2 Zone 3 Interface Compatibility Record |    |

| 10.1.6.3 Sensor Data Records (SDR)             |    |

| 10.2 User Signals                              | 87 |

| 10.2.1 General I/O Signals                     | 87 |

| 10.2.1.1 Attaching digital interfaces          | 87 |

| 10.2.1.2 Clock and Data Signal Planning        |    |

| 10.2.2 GTP Transceiver Signals                 |    |

| 11 APPENDIX A (GENERIC USER CONSTRAINT FILE)   | 91 |

# **List of Figures**

| FIGURE 1-1: TAMC651 BLOCK DIAGRAM                                      |    |

|------------------------------------------------------------------------|----|

| FIGURE 4-1: SENSOR LOCATIONS                                           |    |

| FIGURE 5-1: AMC LOCAL I2C MANAGEMENT BUS                               |    |

| FIGURE 6-1 : M-LVDS TRANSCEIVER FOR AMC PORTS 12 & 13                  |    |

| FIGURE 6-2: MAIN CLOCKING SCHEME                                       |    |

| FIGURE 6-3: FPGA BLOCK DIAGRAM                                         |    |

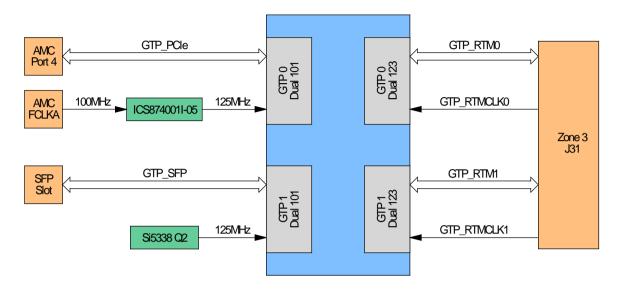

| FIGURE 6-4: SPARTAN-6 GTP TRANSCEIVER                                  | 54 |

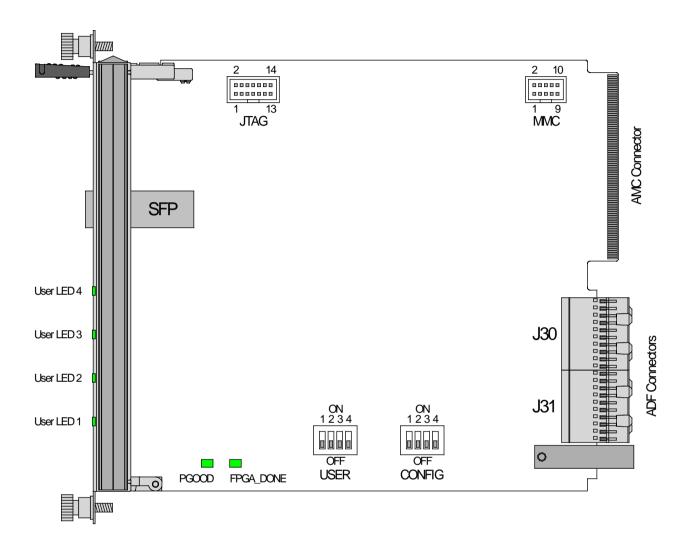

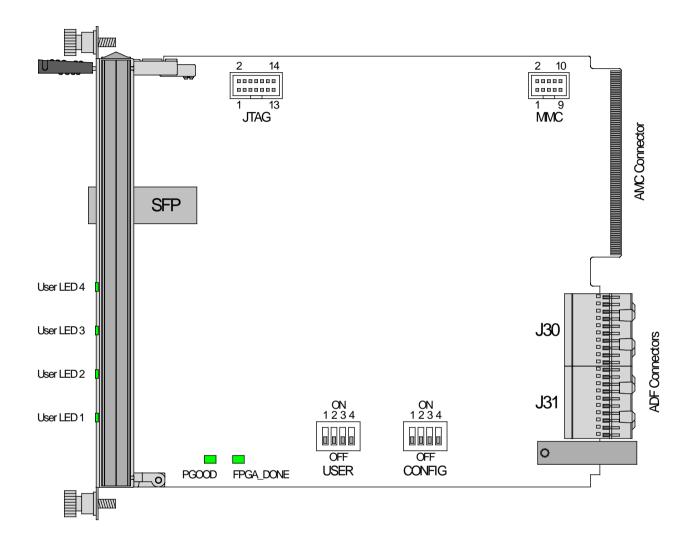

| FIGURE 7-1: BOARD OVERVIEW                                             | 61 |

| FIGURE 9-1: BOARD I/O OVERVIEW                                         | 66 |

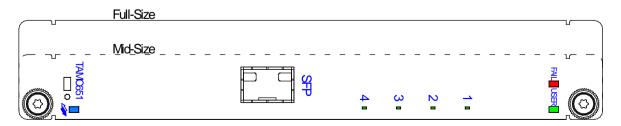

| FIGURE 9-2: FRONT PANEL VIEW                                           | 66 |

| FIGURE 10-1: EXAMPLE I2C I/O EXTENDER INTERFACE ON µRTM                | 84 |

| List of Tables                                                         |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                                     | 11 |

| TABLE 4-1: TEMPERATURE AND VOLTAGE SENSORS                             | 13 |

| TABLE 4-2: FRU INFORMATION                                             | 15 |

| TABLE 4-3: BOARD INFO AREA                                             | 15 |

| TABLE 4-4: PRODUCT INFO AREA                                           | 16 |

| TABLE 4-5: MODULE CURRENT REQUIREMENTS                                 | 17 |

| TABLE 4-6: AMC POINT-TO-POINT CONNECTIVITY                             | 17 |

| TABLE 4-7: CLOCK CONFIGURATION                                         | 17 |

| TABLE 4-8: ZONE 3 INTERFACE COMPATIBILITY                              | 18 |

| TABLE 5-1: LOCAL I2C MANAGEMENT BUS DEVICE OVERVIEW                    | 19 |

| TABLE 5-2: AMC I2C I/O EXTENDER PORT ASSIGNMENT                        | 20 |

| TABLE 6-1: AMC INTERFACE OVERVIEW                                      | 22 |

| TABLE 6-2: M-LVDS INTERFACE DATA TRANSFER SIGNALS (AMC PORTS 12 & 13)  | 24 |

| TABLE 6-3: M-LVDS INTERFACE DEVICE CONTROL SIGNALS (AMC PORTS 12 & 13) | 25 |

| TABLE 6-4: M-LVDS INTERFACE SIGNAL DESCRIPTION                         | 25 |

| TABLE 6-5: AMC BACKPLANE CLOCKS                                        | 26 |

| TABLE 6-6: PROGRAMMABLE CLOCK GENERATOR INPUTS                         | 27 |

| TABLE 6-7: PROGRAMMABLE CLOCK GENERATOR OUTPUTS                        | 27 |

| TABLE 6-8: PROGRAMMABLE CLOCK GENERATOR CONTROL & STATUS PINS          | 28 |

| TABLE 6-9: CLOCK CROSSPOINT-SWITCH PORT CLOCK MAPPING                  | 28 |

| TABLE 6-10: CLOCK CROSSPOINT-SWITCH CONTROL PIN MAPPING                |    |

| TABLE 6-11: SPARTAN-6 LX45T LX100T COMPARISON                          | 31 |

| TABLE 6-12: FPGA I/O BANK OVERVIEW                                     | 31 |

| TABLE 6-13: FPGA PIN / SIGNAL ASSIGNMENT                               |    |

| TABLE 6-14: FPGA I/O SIGNAL DESCRIPTION                                |    |

| TABLE 6-15: FPGA GLOBAL CLOCK PIN ASSIGNMENT                           |    |

| TABLE 6-16: FPGA BANKS 0 & 1 BUFGMUX RESOURCES                         | 50 |

| TABLE 6-17: FPGA BANKS 2 & 3 BUFGMUX RESOURCES              | 51 |

|-------------------------------------------------------------|----|

| TABLE 6-18: FPGA BANK 0 CLOCK REGION BUFFER RESOURCES       | 53 |

| TABLE 6-19: SPARTAN GTP TRANSCEIVER                         | 54 |

| TABLE 6-20: FPGA BANK 3 MCB INTERFACE (DDR3)                | 56 |

| TABLE 6-21: FPGA CONFIGURATION RATE AND TIME                | 57 |

| TABLE 6-22: SPI SERIAL FLASH PIN MAPPING                    | 59 |

| TABLE 7-1: USER DIP-SWITCH                                  | 62 |

| TABLE 7-2: CONFIGURATION DIP-SWITCH                         | 62 |

| TABLE 8-1: HOT-SWAP STATES                                  | 64 |

| TABLE 9-1: FRONT PANEL LEDS (AMC.0)                         | 67 |

| TABLE 9-2: FRONT PANEL USER LEDS                            | 67 |

| TABLE 9-3: ON-BOARD STATUS LEDS                             | 68 |

| TABLE 9-4: USER DIP-SWITCH                                  | 68 |

| TABLE 9-5: CONFIGURATION DIP-SWITCH                         | 68 |

| TABLE 9-6: MMC HEADER                                       | 69 |

| TABLE 9-7: JTAG HEADER                                      | 70 |

| TABLE 9-8: DEBUG CONNECTOR                                  | 71 |

| TABLE 9-9: AMC CONNECTOR PIN ASSIGNMENT                     | 74 |

| TABLE 9-10: SFP CONNECTOR PIN ASSIGNMENT                    |    |

| TABLE 9-11: ZONE 3 MECHANICAL KEYING                        | 75 |

| TABLE 9-12: J30 CONNECTOR PIN ASSIGNMENT                    | 76 |

| TABLE 9-13: J31 CONNECTOR PIN ASSIGNMENT                    | 77 |

| TABLE 9-14: ZONE 3 INTERFACE SIGNAL DESCRIPTION             | 78 |

| TABLE 10-1: µRTM MANAGEMENT SIGNALS AT THE ZONE 3 INTERFACE | 80 |

| TABLE 10-2: SUPPORTED µRTM MANAGEMENT SIGNALS VIA I2C       |    |

| TABLE 10-3: SUPPORTED µRTM I2C DEVICES                      |    |

| TABLE 10-4: µRTM I2C I/O EXTENDER PORT ASSIGNMENT           |    |

| TABLE 10-5: µRTM FRU COMMON HEADER                          |    |

| TABLE 10-6: ZONE 3 INTERFACE COMPATIBILITY RECORD           |    |

| TABLE 10-7: PRE-CONFIGURED µRTM TEMPERATURE SENSOR          | 86 |

| TABLE 10-8: SPARTAN-6 LVCMOS25 & LVTTL DC CHARACTERISTICS   |    |

| TABLE 10-9: ZONE 3 INTERFACE USER SIGNALS                   | 89 |

| TABLE 10-10: SIMPLIFIED URTH SIGNAL MAPPING RECOMMENDATION  | ar |

## 1 Product Description

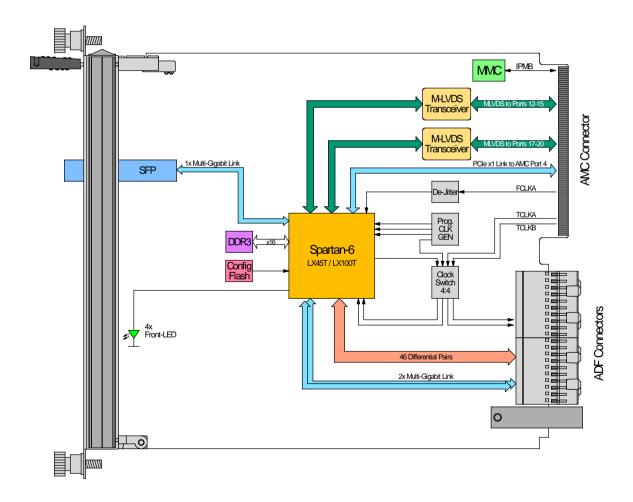

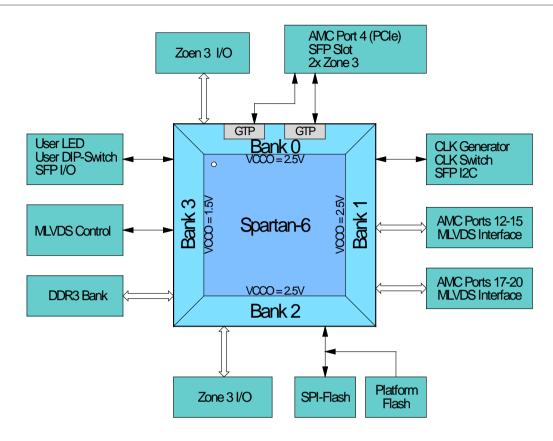

The TAMC651 is a double Mid-Size AMC providing a user programmable FPGA and a Zone 3 interface for µRTM Rear-I/O according to MTCA.4.

The user programmable FPGA is a Xilinx Spartan-6 LX45T/LX100T device. Both a Xilinx Platform-Flash and a serial SPI Flash are available as FPGA configuration memory.

128 MB of 16 bit wide DDR3 memory is provided, utilizing a Spartan-6 integrated Memory-Controller-Block.

AMC port 4 is used for a PCI Express x1 link that utilizes the Spartan-6 integrated PCI Express Endpoint Block.

AMC ports 12-15 (point-to-point) and AMC ports 17-20 (multi-point) are connected to FPGA I/O pins via on-board M-LVDS transceivers.

One of the Spartan-6 GTP transceivers utilizes a SFP interface available at the front plate.

The TAMC651 provides a multi-output programmable clock generator and a 4 In / 4 Out clock crosspoint-switch.

46 differential pair FPGA I/Os and two of the Spartan-6 GTP transceivers are connected to the Zone 3 interface (μRTM).

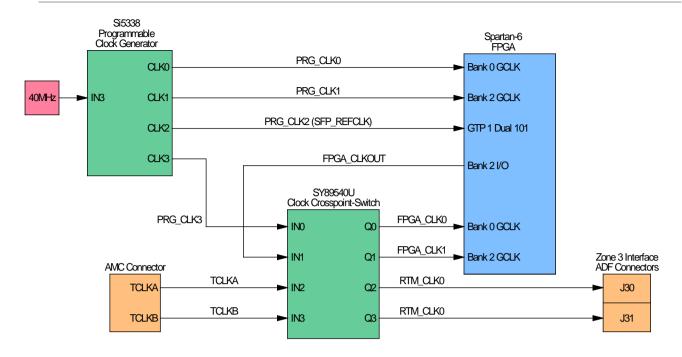

Figure 1-1: TAMC651 Block Diagram

# 2 Technical Specification

| , ,                                                                                                              |                                                                                                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| , ,                                                                                                              |                                                                                                                                                    |  |  |

| Precision Timing)  Module Type: TAMC651-10R/-12R: Double Mid-size Mo                                             | PICMG® MTCA.4 (MicroTCA Enhancements for Rear-I/O and                                                                                              |  |  |

| Port 4 PICMG® AMC.1 R1.0 PCIe single (x1) port (AMC.1 Type 1 compliant)                                          |                                                                                                                                                    |  |  |

| Ports 12-15  MLVDS Transceiver Point-to-Point (controlled by FPGA I/O)  Electrical Interface                     |                                                                                                                                                    |  |  |

| Ports 17-20  MLVDS Transceiver Multi-Point (controlled by FPGA I/O)                                              |                                                                                                                                                    |  |  |

| TCLKA, TCLKB  Connected to Clock Crosspoint-Sw Inputs                                                            | tch                                                                                                                                                |  |  |

| IPMI Support                                                                                                     |                                                                                                                                                    |  |  |

| IPMI Version 1.5                                                                                                 | sion 1.5                                                                                                                                           |  |  |

| AMC.0 Front Panel LEDs  Blue Hot-Swap LED  Red Failure Indication LED (LED1)  Green User LED (LED2)              | Red Failure Indication LED (LED1)                                                                                                                  |  |  |

| Main On-Board Devices                                                                                            |                                                                                                                                                    |  |  |

| MMC Atmel ATmega1281-16MU                                                                                        | Atmel ATmega1281-16MU                                                                                                                              |  |  |

| PCIe Endpoint Spartan-6 FPGA PCI Express Endpoint Block                                                          |                                                                                                                                                    |  |  |

| User Programmable FPGA  TAMC651-10R/-11R: Xilinx XC6SLX45T-2FGG484I TAMC651-12R/-13R: Xilinx XC6SLX100T-2FGG484I |                                                                                                                                                    |  |  |

| FPGA Configuration Flash Xilinx XCF32PFSG48C                                                                     |                                                                                                                                                    |  |  |

| SPI Serial Flash Numonyx M25P64-VME6                                                                             |                                                                                                                                                    |  |  |

| PCle Jitter Attenuator IDT ICS874001I-05                                                                         |                                                                                                                                                    |  |  |

| Programmable Clock Generator Silicon Labs Si5338B-A-GM                                                           | Silicon Labs Si5338B-A-GM                                                                                                                          |  |  |

| LVDS Crosspoint-Switch Micrel SY89540UMY                                                                         | Micrel SY89540UMY                                                                                                                                  |  |  |

| M-LVDS Transceiver National DS91M040TSQ                                                                          |                                                                                                                                                    |  |  |

|                                                                                                                  | 16-bit wide 128 Mbyte DDR3 Memory, connected to Spartan-6 FPGA Memory Controller Block (MT41J64M16LA-187E-IT, MT41K64M16TW-107-IT:J or compatible) |  |  |

| DDR3 Memory FPGA Memory Controller Block (MT41J64M16LA-187E-IT, MT41K64M16TW-107-IT:J o                          | r                                                                                                                                                  |  |  |

| DDR3 Memory FPGA Memory Controller Block (MT41J64M16LA-187E-IT, MT41K64M16TW-107-IT:J o                          | r                                                                                                                                                  |  |  |

|                             | 4x general purpose LED (controlled by FPGA I/O)                                                                                                                                                                                                                                                                                                             |                  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| SFP Port                    | SFP Connector                                                                                                                                                                                                                                                                                                                                               | Molex 74441-001  |  |

| SFF FOIL                    | SFP Cage                                                                                                                                                                                                                                                                                                                                                    | Molex 74754-0103 |  |

|                             | 46x LVDS differential pairs (connected to FPGA I/O)                                                                                                                                                                                                                                                                                                         |                  |  |

| Zone 3 Interface I/O        | 2x LVDS differential Reference Clock (coming from Crosspoint-Switch)                                                                                                                                                                                                                                                                                        |                  |  |

|                             | 2x Spartan-6 FGPA GTP transceiver ports                                                                                                                                                                                                                                                                                                                     |                  |  |

|                             | FPGA I/O Bank Supply 2.5V                                                                                                                                                                                                                                                                                                                                   |                  |  |

| Zone 3 Interface Connectors | 2x ERNI Ermet ZD ADF                                                                                                                                                                                                                                                                                                                                        | 30-pair 973028   |  |

| Zone 3 Interface Key        | Tyco 5223986-1                                                                                                                                                                                                                                                                                                                                              |                  |  |

| Zone 3 interrace Key        | N = 1 (LVDS)                                                                                                                                                                                                                                                                                                                                                |                  |  |

| JTAG Header                 | Molex 87832-1420                                                                                                                                                                                                                                                                                                                                            |                  |  |

| MMC Header                  | Molex 87832-1020                                                                                                                                                                                                                                                                                                                                            |                  |  |

| Physical Data               | Physical Data                                                                                                                                                                                                                                                                                                                                               |                  |  |

|                             | Management Power: 52mA peak @ +3.3V DC                                                                                                                                                                                                                                                                                                                      |                  |  |

| Power Requirements          | Payload Power: Depends on FPGA application 0.64A @ +12V DC with TPLD004 example running in idle (TAMC651-10R)                                                                                                                                                                                                                                               |                  |  |

|                             | max. Current Draw as per Module Current Requirements record: 4.5A                                                                                                                                                                                                                                                                                           |                  |  |

| Tomporeture Bange           | Operating                                                                                                                                                                                                                                                                                                                                                   | -40°C to +85°C   |  |

| Temperature Range           | Storage                                                                                                                                                                                                                                                                                                                                                     | -40°C to +85°C   |  |

| MTBF                        | 283739 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                  |  |

| Humidity                    | 5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                     |                  |  |

| Weight                      | 212 g                                                                                                                                                                                                                                                                                                                                                       |                  |  |

|                             |                                                                                                                                                                                                                                                                                                                                                             |                  |  |

Table 2-1: Technical Specification

## 3 Handling and Operating Instructions

## 3.1 ESD Protection

The AMC module is sensitive to static electricity. Packing, unpacking and all other module handling has to be done in an ESD/EOS protected Area.

## 3.2 Thermal Considerations

Forced air cooling is recommended during operation. Without forced air cooling, damage to the device can occur.

## 3.3 I/O Signaling Voltages

The Zone 3 I/O-Lines are directly connected to FPGA I/O pins. The I/O voltage of these FPGA I/O pins is 3.95V maximum.

The FPGA I/O pins are NOT 5V tolerant.

## 4 IPMI Support

The AMC module provides a Module Management Controller (MMC) that performs health monitoring, hot-swap functionality and stores the Field Replaceable Unit (FRU) information. The MMC communicates via an Intelligent Platform Management Interface (IPMI).

## 4.1 Temperature and Voltage Sensors

The MMC monitors on-board sensors and signals sensor events to the superordinated IPMI controller / shelf manager. Available sensors are listed in the table below.

| Sensor Number | Signal Type | Thresholds                 | Signal Monitored |

|---------------|-------------|----------------------------|------------------|

| 0             | Event       | -                          | Hot-swap switch  |

| 1             | Temperature | Inr lcr Inc unc ucr<br>unr | Board Temp.      |

| 2             | Temperature | Inr lcr Inc unc ucr<br>unr | Board Temp.      |

| 3             | Voltage     | Inr lcr Inc unc ucr<br>unr | +12V (PWR)       |

| 4             | Voltage     | Inr lcr Inc unc ucr<br>unr | +5V              |

| 5             | reserved    | reserved                   | reserved         |

| 6             | Voltage     | Inr Icr Inc unc ucr<br>unr | +1.8V            |

| 7             | Event       | -                          | RTM Hot-Swap     |

| 8             | Temperature | Inr Icr Inc unc ucr<br>unr | RTM Temp.        |

unr: upper non-recoverable, ucr: upper critical, unc: upper non-critical Inr: lower non-recoverable, lcr: lower critical, Inc: lower non-critical

Table 4-1: Temperature and Voltage Sensors

The following on-board power supplies are monitored by the MMC via a digital power good signal: +1.2V, 1.5V, 2.5V, 3.3V.

## 4.1.1 Sensor Locations

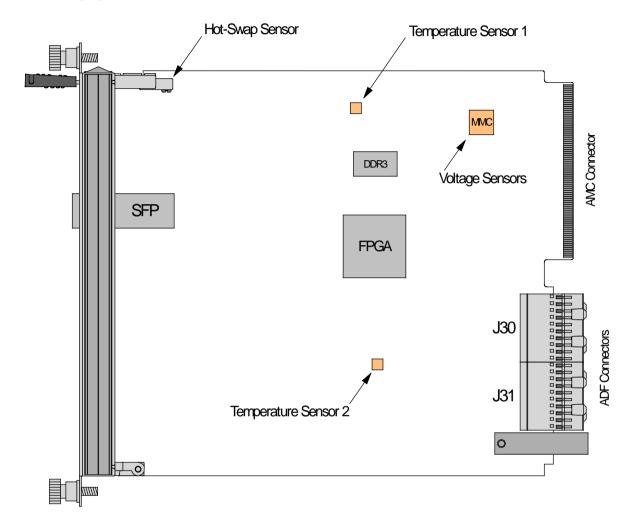

The following figure shows the location of the TAMC651 physical sensors.

Figure 4-1: Sensor Locations

## 4.2 FRU Information

The MMC stores the module FRU information in a non-volatile EEPROM. Some of the records are writeable. If records are modified, the user is responsible for setting the proper checksums. The actual FRU information data is indicated below.

| Area                              | Size (in Bytes) | Writeable |

|-----------------------------------|-----------------|-----------|

| Common Header                     | 8               | no        |

| Chassis Info Area                 | 0               | no        |

| Board Info Area                   | variable        | no        |

| Product Info Area                 | variable        | no        |

| Multi Record Area                 |                 |           |

| Module Current<br>Requirements    | variable        | yes       |

| AMC Point-to-Point Connectivity   | variable        | yes       |

| Clock Configuration               | variable        | yes       |

| Zone 3 Interface<br>Compatibility | variable        | yes       |

Table 4-2: FRU Information

### 4.2.1 Board Info Area

| Product Information    | Value                                         |

|------------------------|-----------------------------------------------|

| Version                | 1                                             |

| Language Code          | 0x00 - English                                |

| Manufacturer date/time | determined at manufacturing                   |

| Board manufacturer     | TEWS TECHNOLOGIES GmbH                        |

| Board product name     | TAMC651                                       |

| Board serial number    | determined at manufacturing (see board label) |

| Board part number      | TAMC651-xxR<br>-xx = -10 / -11 / -12 / -13    |

Table 4-3: Board Info Area

## 4.2.2 Product Info Area

| Product Information     | Value                                         |

|-------------------------|-----------------------------------------------|

| Version                 | 1                                             |

| Language Code           | 0x00 - English                                |

| Product manufacturer    | TEWS TECHNOLOGIES GmbH                        |

| Product name            | TAMC651                                       |

| Board part/model number | TAMC651-xxR<br>-xx = -10 / -11 / -12 / -13    |

| Product version         | V1.0 Rev. C (see board label)                 |

| Product serial number   | determined at manufacturing (see board label) |

| Asset tag               | = Product serial Number                       |

Table 4-4: Product Info Area

#### 4.2.3 Multi Record Area

#### 4.2.3.1 Module Current Requirements

The "Current Draw" value holds the Payload Power (PWR) requirement of the module (including the optional µRTM) given as current requirement in units of 0.1A at 12V.

The AMC module announces the value of "Current Draw" as current demand to the shelf manager. If the allocated power budget for the actual AMC slot is smaller than this value, the shelf manager may not enable Payload power for this slot. If required, the "Current Draw" value in the Module Current Requirements record may be modified to a value that falls within the given power budget. Make sure that the modified value still satisfies the AMC module power requirements for both the AMC module (with the actual FPGA implementation) and the mounted µRTM.

| Product Information | Value        |

|---------------------|--------------|

| Current Draw        | 0x2D (4.5 A) |

Table 4-5: Module Current Requirements

### 4.2.3.2 AMC Point-to-Point Connectivity

The AMC module provides the following AMC Point-to-Point Connectivity Record Data.

| Channel | Port                                      | Link Type | Link Type Extension        | Link<br>Grouping ID    | Asymmetric<br>Match         |

|---------|-------------------------------------------|-----------|----------------------------|------------------------|-----------------------------|

| 0       | 0 4 AMC.1 Post Express AMC.1 Post Express |           | Gen 1 PCI Express, non-SSC | Single<br>Channel Link | PCI Express<br>Primary Port |

| 0       |                                           |           | Gen 1 PCI Express,<br>SSC  | Single<br>Channel Link | PCI Express<br>Primary Port |

Table 4-6: AMC Point-to-Point Connectivity

Since the protocol and channel configuration for the MLVDS transceiver interface on AMC ports 12-15 and 17-20 is user application dependent, there are no pre-configured channel or link descriptors stored for AMC ports 12-15 and 17-20.

#### 4.2.3.3 Clock Configuration

AMC FCLKA is used as the PCI Express Reference Clock. TCLKA and TCLKB are connected to inputs of the on-board clock crosspoint-switch.

| Clock ID | Clock Features                                  | Clock Family | Clock Accuracy       | Clock<br>Frequency |

|----------|-------------------------------------------------|--------------|----------------------|--------------------|

| FCLKA    | Clock Receiver, connected through PLL           | PCI Express  | PCI Express<br>Gen 1 | 100 MHz nom.       |

| TCLKA    | Clock Receiver,<br>Not connected through<br>PLL |              | unspecified          |                    |

| TCLKB    | Clock Receiver,<br>Not connected through<br>PLL |              | unspecified          |                    |

Table 4-7: Clock Configuration

### 4.2.3.4 Zone 3 Interface Compatibility

The Zone 3 Interface Compatibility data of AMC and  $\mu RTM$  must match for the  $\mu RTM$  to be considered as compatible.

| Parameter             |                                     | Setting                                                   |

|-----------------------|-------------------------------------|-----------------------------------------------------------|

| Type of Interface Ide | entifier                            | OEM                                                       |

| Interface Identifier  | Manufacturer ID (IANA)              | TEWS Technologies GmbH Private Enterprise Number 0x0071E3 |

|                       | OEM defined<br>Interface Designator | 0x828B0000<br>(0x8 = TAMC, 0x28B = 651)                   |

Table 4-8: Zone 3 Interface Compatibility

## 4.2.4 Modifying FRU Records

Some of the records are writeable to allow adaption to certain systems. If records are modified, the user is responsible for setting the proper checksums.

## 5 Local I2C Management Bus

This chapter describes the TAMC651 local I2C management bus controlled by the TAMC651 MMC.

The chapter is merely intended for the MMC firmware designer (not for the user).

### 5.1 Overview

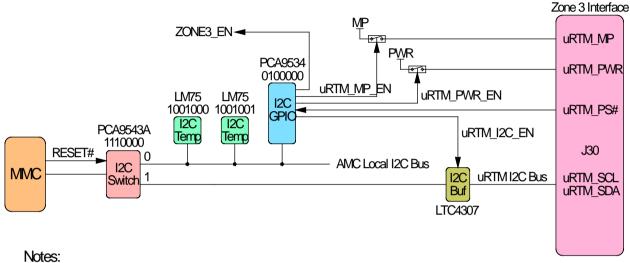

The figure below shows the MMC controlled local I2C management bus of the TAMC651.

I2C Addresses 1110000 and 1110001 are reserved by the TAMC651. These I2C Addresses must not be used by the uRTM.

Figure 5-1: AMC Local I2C Management Bus

The following I2C devices are addressable by the TMAC651 MMC.

| I2C Address    | I2C Device                         |

|----------------|------------------------------------|

| 70h (1110000b) | PCA9543A I2C Bus Switch            |

| 48h (1001000b) | First LM75 I2C Temperature Sensor  |

| 49h (1001001b) | Second LM75 I2C Temperature Sensor |

| 20h (0100000b) | PCA9535 8-bit GPIO Extender        |

Table 5-1: Local I2C Management Bus Device Overview

## 5.2 I2C Bus Switch

The TAMC651 provides a PCA9543A I2C bus switch to decouple the AMC local I2C management bus from the  $\mu$ RTM I2C management bus.

The TAMC651 MMC local I2C management bus directly connects to the upstream port of the PCA9543A I2C bus switch. The AMC local I2C management bus is located on downstream port 0 and the  $\mu$ RTM I2C management bus is located on downstream port 1 of the PCA9543A I2C bus switch (decoupled by an additional I2C bus buffer as per MTCA.4).

## 5.3 I2C Temperature Sensors

The TAMC651 provides two LM75 temperature sensors on local I2C management bus 0.

I2C addresses are 48h and 49h.

Please see the LM75 device documentation for details.

## 5.4 I2C I/O Extender

The TAMC651 provides an 8-bit PCA9534 GPIO extender on local I2C management bus 0.

The following MMC controlled  $\mu RTM$  related management signals/functions are implemented on the AMC module's PCA9534.

| I/O Port | I/O<br>Direction | Signal       | Description                                                                                                  |

|----------|------------------|--------------|--------------------------------------------------------------------------------------------------------------|

| 7        | I                | RTM_I2C_RDY  | μRTM I2C buffer ready status<br>Ready goes high when the buffer is<br>enabled and connection is established. |

| 6        | I                | RTM_PWR_ERR# | μRTM PWR load switch status Active low. Indicating under voltage.                                            |

| 5        | I                | RTM_MP_ERR#  | μRTM MP load switch failure status Active low. Indicating over current, under voltage or over temperature.   |

| 4        | 0                | ZONE3_EN     | Zone 3 Interface Enable 0 = Zone 3 Interface Disable 1 = Zone 3 Interface Enable                             |

| 3        | 0                | RTM_I2C_EN   | μRTM I2C Bus Buffer Enable 0 = Disable μRTM I2C Bus 1 = Enable μRTM I2C Bus                                  |

| 2        | 0                | RTM_PWR_EN   | μRTM Payload Power Enable<br>0 = Disable μRTM PWR<br>1 = Enable μRTM PWR                                     |

| 1        | 0                | RTM_MP_EN    | μRTM Management Power Enable 0 = Disable μRTM MP 1 = Enable μRTM MP                                          |

| 0        | I                | RTM_PS#      | $\mu$ RTM Present Detection $0 = \mu$ RTM is present $1 = \mu$ RTM is not present                            |

Table 5-2: AMC I2C I/O Extender Port Assignment

The µRTM present detect signal (RTM\_PS#) is directly connected to the RTM\_PS# pin on the Zone 3 interface.

After detecting a  $\mu RTM$ , the MMC firmware may enable the  $\mu RTM$  management power by setting RTM\_MP\_EN.

The µRTM payload power should only be enabled after a successful Zone 3 Interface Compatibility check.

The Zone 3 interface enable signal integrates the  $\mu$ RTM JTAG chain into the TAMC651 JTAG chain. The signal also connects to an FPGA I/O pin. The FPGA application may use this signal to enable/disable drivers for the Zone 3 interface.

#### Simplified example sequence:

- Wait for µRTM present detection

- Enable µRTM management power

- Check µRTM management power load switch status

- Enable µRTM I2C bus buffer

- Check μRTM I2C bus buffer status

- Read µRTM FRU data

- · Check Zone 3 Interface compatibility

- Monitor μRTM Hot-Swap handle (via μRTM I2C bus)

- Control μRTM Front LEDs (via μRTM I2C bus)

- If Zone 3 interface is compatible and  $\mu RTM$  hot-swap handle is closed enable  $\mu RTM$  payload power

- Check µRTM payload power load switch status

- Control µRTM Front LEDs (via µRTM I2C bus)

- Continue monitoring the μRTM hot-swap handle (via μRTM I2C bus) and μRTM present status

## **6 Functional Description**

This chapter gives a brief overview of the various AMC module functions.

## 6.1 AMC Interface

#### 6.1.1 Overview

| AMC-Connector | Backplane                                              | TAMC651                                                                                                         |

|---------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Port 4        | PCIe / SRIO                                            | PCle x1 Link Connected to Spartan-6 FPGA PCle Endpoint Block                                                    |

| Port 12-15    | Point-2-Point links                                    | Connected to FPGA I/O via M-LVDS transceivers                                                                   |

| Port 17-20    | Multi-Point bus for<br>Triggers, Clocks,<br>Interlocks | Connected to FPGA I/O via M-LVDS transceivers                                                                   |

| TCLKA         | TCLKA+/-                                               | Connected to on-board Clock Cross-<br>Point-Switch input                                                        |

| TCLKB         | TCLKB+/-                                               | Connected to on-board Clock Cross-<br>Point-Switch input                                                        |

| FCLKA         | FCLKA+/-                                               | PCIe Reference Clock Connected to FPGA GTP transceiver via an on-board PCI Express Jitter Attenuator            |

| JTAG          | TCK, TMS, TDI, TDO                                     | One Option for controlling the TAMC651 JTAG Chain                                                               |

| I2C           | SCL_L, SDA_L                                           | Connected to MMC                                                                                                |

| Management    | PS0#, PS1#, GA[0:2],<br>ENABLE#                        | Used for module management                                                                                      |

| Power Supply  | MP, PWR, GND                                           | Used as power supplies The MMC also controls on-board load switches to gate MP and PWR to the Zone 3 interface. |

Table 6-1: AMC Interface Overview

#### 6.1.1.1 Point-to-Point Links

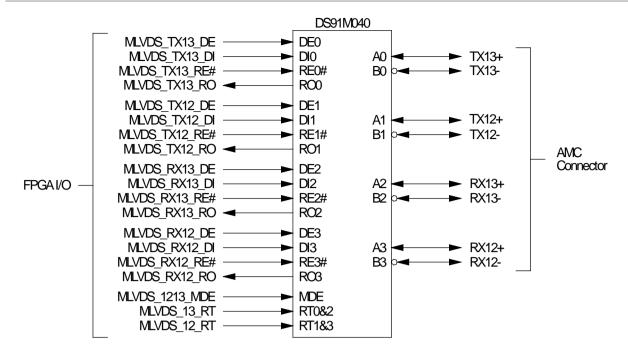

AMC backplane ports 12-15 are connected to DS91M040 M-LVDS transceivers. There is one bi-directional M-LVDS transceiver line for each port RX pair and one bi-directional M-LVDS transceiver line for each port TX pair.

The digital LVTTL/LVCMOS communication interface of the M-LVDS transceivers is connected to FPGA I/O pins.

The TAMC651 provides a 100R termination resistor for each of the 8 M-LVDS differential RX and TX pairs of AMC ports 12-15.

#### 6.1.1.2 Multi-Point Links

AMC backplane ports 17-20 are connected to DS91M040 M-LVDS transceivers. There is one bi-directional M-LVDS transceiver line for each port RX pair and one bi-directional M-LVDS transceiver line for each port TX pair.

The digital LVTTL/LVCMOS communication interface of the M-LVDS transceivers is connected to FPGA I/O pins.

The receive data signals are mapped to global clock FPGA pins.

The TAMC651 does not provide any termination resistors on the 8 M-LVDS differential RX and TX pairs of AMC ports 17-20.

### **6.1.2 PCI-Express Interface**

AMC port 4 is connected to one of the FPGA GTP transceivers supporting the Spartan-6 integrated PCIe Endpoint-Block.

The user programmable FPGA application implements the PCI Express x1 interface and also defines the addressable resources like registers, etc.

AMC FLCKA is used as the reference clock for the FPGA PCIe GTP transceiver. A Configuration DIP-Switch provides an option for multiplying FCLKA by 5:4 (default) or by 1. With the 100 MHz FCLKA for PCIe, the PCIe GTP transceiver reference clock is 125 MHz by default.

#### 6.1.3 M-LVDS Transceiver Interface

The TAMC651 provides M-LVDS transceivers at AMC ports 12-15 (point-to-point) and AMC ports 17-20 (multi-drop).

Four National Semiconductor DS91M040 Quad M-LVDS transceivers are used on the TAMC651. Two for AMC ports 12-15 (point-to-point) and two for the AMC ports 17-20 (multi-point). Each DS91M040 device provides four M-LVDS transceivers (covering two AMC ports with TX and RX), two receiver type selection inputs and a general chip enable input.

The TAMC651 provides a 100 Ohm termination resistor for the M-LVDS lines on AMC ports 12-15 (point-to-point). The TAMC651 does not provide any termination resistor on the M-LVDS lines on AMC ports 17-20 (multi-point).

The line interface of the M-LVDS transceivers is directly connected to the appropriate pins on the AMC connector (no AC coupling). The digital communication signals of the M-LVDS transceivers are connected to FPGA I/O pins. The receive data signals for AMC ports 17-20 are connected to global clock FPGA pins.

The following figure shows one of the four M-LVDS transceivers, the one used for AMC ports 12 & 13 (termination resistors not shown). The M-LVDS interface for AMC ports 14 & 15, 17 & 18, 19 & 20 is build accordingly.

Figure 6-1: M-LVDS Transceiver for AMC Ports 12 & 13

The following tables show the signal/pin assignments for AMC ports 12 and 13.

| AMC  | DS91M040 |      |     | FPGA           |            |     |

|------|----------|------|-----|----------------|------------|-----|

| Port | Pin      | Bank | Pin | Signal         | I/O Std.   | Dir |

|      | RE0#     |      | M21 | MLVDS_RX12_RE# |            | Out |

| DV42 | RO0      |      | P21 | MLVDS_RX12_RO  |            | In  |

| RX12 | DI0      |      | U22 | MLVDS_RX12_DI  |            | Out |

|      | DE0      |      | M22 | MLVDS_RX12_DE  |            | Out |

|      | RE1#     |      | N15 | MLVDS_TX12_RE# |            | Out |

| TX12 | RO1      |      | P18 | MLVDS_TX12_RO  |            | ln  |

| 1812 | DI1      | _    | W22 | MLVDS_TX12_DI  |            | Out |

|      | DE1      |      | N16 | MLVDS_TX12_DE  | LVCMOS25   | Out |

|      | RE2#     | 1    | M17 | MLVDS_RX13_RE# | LVCIVIOS25 | Out |

| RX13 | RO2      |      | P19 | MLVDS_RX13_RO  |            | In  |

| KAIS | DI2      |      | V22 | MLVDS_RX13_DI  |            | Out |

|      | DE2      |      | M18 | MLVDS_RX13_DE  |            | Out |

|      | RE3#     |      | N20 | MLVDS_TX13_RE# |            | Out |

| TX13 | RO3      |      | P17 | MLVDS_TX13_RO  |            | ln  |

| 1713 | DI3      |      | Y22 | MLVDS_TX13_DI  |            | Out |

|      | DE3      |      | M16 | MLVDS_TX13_DE  |            | Out |

Table 6-2: M-LVDS Interface Data Transfer Signals (AMC Ports 12 & 13)

| DS91M040 | FPGA |     |                 |          |     |

|----------|------|-----|-----------------|----------|-----|

| Pin      | Bank | Pin | Signal          | I/O Std. | Dir |

| MDE      |      | J7  | MLVDS_12_13_MDE |          | Out |

| RT1&3    | 3    | H4  | MLVDS_12_RT     | LVCMOS15 | Out |

| RT0&2    |      | G4  | MLVDS_13_RT     |          | Out |

Table 6-3: M-LVDS Interface Device Control Signals (AMC Ports 12 & 13)

| Signal          | Description                                                   |

|-----------------|---------------------------------------------------------------|

| MLVDS_xx_yy_MDE | Master Device Enable 0: M-LVDS Transceiver disabled (default) |

|                 | 1: M-LVDS Transceiver enabled                                 |

|                 | Receiver Type                                                 |

| MLVDS_xx_RT     | 0: Type 1 Receiver Inputs                                     |

| WILVDS_XX_KT    | 1: Type 2 Receiver Inputs                                     |

|                 | See DS91M040 documentation.                                   |

|                 | Receiver Enable                                               |

| MLVDS_xx_RE#    | 0: Receiver enabled                                           |

|                 | 1: Receiver disabled                                          |

| MLVDS_xx_RO     | Receiver Output (Data to FPGA input)                          |

| MLVDS_xx_DI     | Driver Input (Data from FPGA output)                          |

|                 | Driver Enable                                                 |

| MLVDS_xx_DE     | 0: Driver disabled (default)                                  |

|                 | 1: Driver enabled                                             |

Table 6-4: M-LVDS Interface Signal Description

Please see the "User Programmable FPGA" chapter for all FPGA pin/signal assignments of the M-LVDS interface.

## 6.2 Clocking Scheme

The figure below shows the main TAMC651 clocking scheme.

More details are available in the appropriate device sub-chapters.

Figure 6-2: Main Clocking Scheme

### 6.2.1 On-board Oscillators

The TAMC651 provides two fix on-board oscillators.

A 40 MHz oscillator is used as the clock source for the Si5338 programmable clock generator.

A 62.5 MHz oscillator is connected to the FPGA GCLK0/USER\_CCLK pin.

## 6.2.2 AMC Backplane Clocks

The following table shows the TAMC651 relevant AMC backplane clock signals.

| AMC-<br>Connector | Backplane                          | TAMC651                                                                                                                                                                                                                            |

|-------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 17-20        | Triggers,<br>Clocks,<br>Interlocks | Bidirectional differential signals. Connected to the line interface of on-board M-LVDS Transceivers.  The digital interface receives signals of the M-LVDS transceivers are connected to clock capable pins of the Spartan-6 FPGA. |

| TCLKA             |                                    | TCLKA (connected to on-board clock crosspoint-switch input.                                                                                                                                                                        |