### The Embedded I/O Company

# **TIP102**

# Motion Controller with Incremental Encoder Interface

Version 1.1

### **User Manual**

Issue 1.1.9 November 2008

www.tews.com

mond Parkway, Phone: +1 (775) 850 5830 NV 89521, USA Fax: +1 (775) 201 0347 e-mail: usasales@tews.com

#### TIP102-1x

One axis motion controller incremental encoder interface

#### TIP102-2x

Two axes motion controller incremental encoder interface

#### TIP102-TM-10

Transition Module for TIP102-1x Isolated 24V digital I/O

#### TIP102-TM-11

Transition Module for TIP102-1x Isolated 24V digital I/O, encoder

#### TIP102-TM-12

Transition Module for TIP102-1x Isolated 24V digital I/O, encoder, analog out

#### TIP102-TM-13

Transition Module for TIP102-1x Isolated 24V digital I/O, encoder, analog in & out

#### TIP102-TM-20

Transition Module for TIP102-2x Isolated 24V digital I/O

#### TIP102-TM-21

Transition Module for TIP102-2x Isolated 24V digital I/O, encoder

#### TIP102-TM-22

Transition Module for TIP102-2x Isolated 24V digital I/O, encoder, analog out

#### TIP102-TM-23

Transition Module for TIP102-2x Isolated 24V digital I/O, encoder, analog in & out

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©1994-2008 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                           | Date           |

|-------|---------------------------------------------------------------------------------------|----------------|

| 1.0   | First Issue                                                                           | April 1994     |

| 1.1   | Extended                                                                              | December 1994  |

| 1.2   | Technical Specification                                                               | April 1996     |

| 1.3   | General Revision                                                                      | October 2003   |

| 1.4   | Add ID PROM contents for version 1.1                                                  | September 2004 |

| 1.5   | Additional note for ADC conversion                                                    | October 2004   |

| 1.6   | More detailed description of the various I/O signals                                  | October 2005   |

| 1.7   | New address TEWS LLC                                                                  | September 2006 |

| 1.8   | Signal Polarity Clarification in Pin Assignment Tables                                | February 2007  |

| 1.1.9 | Complete revision during redesign process Documentation versioning scheme has changed | November 2008  |

# **Table of Contents**

| 1 | LIV                                | ODUCT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ······ /  |

|---|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2 | TEC                                | CHNICAL SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8         |

|   | 2.1                                | TIP102-xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8         |

|   | 2.2                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

| 3 | ID F                               | PROM CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10        |

| 4 |                                    | ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| • | 4.1                                | I/O Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

|   | 4.1                                | Input and Status Register (INPSR)                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|   | 4.3                                | Output Control Register (OUTCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

|   | 4.4                                | Counter Data Register (CNTDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   |                                    | 4.4.1 Reading Counter Data                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|   |                                    | 4.4.2 Writing Counter Data                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|   | 4.5                                | Counter Control and Status Register (CNTCS)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15        |

|   |                                    | 4.5.1 Master Control Register (MCR)                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|   |                                    | 4.5.2 Input Control Register (ICR)                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |

|   |                                    | 4.5.3 Output Control Register (OCR)                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|   |                                    | 4.5.4 Quadrature Register (QR)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

|   | 4.6                                | DAC Data Register (DACDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|   | 4.7                                | ADC Control and Status Register (ADCCS)                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |

|   | 4.8                                | ADC Data Register (ADCDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|   | 4.9                                | Configuration Control Register (CONCR)                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |

|   | 4.10                               | Interrupt Vector Register (INTVEC)                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21        |

| 5 | FUN                                | NCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22        |

| _ |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

|   | 5.1                                | Quadrature modes of the LS7166                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |

|   | 5.1                                | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>22</b> |

|   | 5.1                                | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   |                                    | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 5.1<br>5.2                         | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   |                                    | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   |                                    | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 5.2                                | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 6 | 5.2                                | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 5.2<br>PR(                         | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 5.2<br>PR(                         | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|   | 5.2<br>PR(<br>6.1                  | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 6 | 5.2<br>PR(<br>6.1                  | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 6 | 5.2<br>PR(<br>6.1                  | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 6 | 5.2<br>PR0<br>6.1<br>JUN<br>7.1    | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

| 6 | 5.2<br>PR0<br>6.1<br>JUN<br>7.1    | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

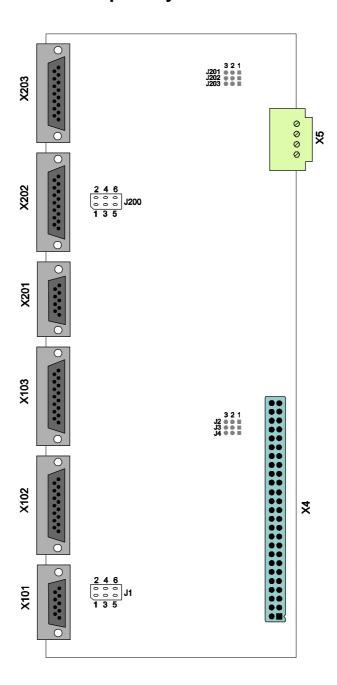

| 6 | 5.2<br>PR(6.1<br>JUN<br>7.1<br>7.2 | 5.1.1 Mode x1 5.1.2 Mode x2 5.1.3 Mode x4  Reference Logic  5.2.1 Reference Mode - without reference switch 5.2.2 Reference Mode - with reference switch 5.2.3 External Trigger Input  OGRAMMING HINTS  LS7166 Counter 6.1.1 Initialization 6.1.2 Reading actual counter data value  MPER CONFIGURATIONS  TIP102-xx IP Module  TIP102-TM-xx Transition Module  7.2.1 Trigger I/O Jumper Configuration 7.2.2 Encoder Input Jumper Configuration 7.2.3 TIP102-TM-xx Jumper Layout | 22        |

| 6 | 5.2<br>PR(6.1<br>JUN<br>7.1<br>7.2 | 5.1.1 Mode x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22        |

| 6 | 5.2<br>PR(6.1<br>JUN<br>7.1<br>7.2 | 5.1.1 Mode x1 5.1.2 Mode x2 5.1.3 Mode x4  Reference Logic  5.2.1 Reference Mode - without reference switch 5.2.2 Reference Mode - with reference switch 5.2.3 External Trigger Input  OGRAMMING HINTS  LS7166 Counter 6.1.1 Initialization 6.1.2 Reading actual counter data value  MPER CONFIGURATIONS  TIP102-xx IP Module  TIP102-TM-xx Transition Module  7.2.1 Trigger I/O Jumper Configuration 7.2.2 Encoder Input Jumper Configuration 7.2.3 TIP102-TM-xx Jumper Layout | 22        |

| 8.2 | Transition Module I/O Connectors (TIP102-TM-xx) |                                                  |    |

|-----|-------------------------------------------------|--------------------------------------------------|----|

|     | 8.2.1                                           | X101/X201 - DB9 female - Servo Amplifier Signals | 30 |

|     |                                                 | X102/X202 - DB15 male - Power and I/O Signals    |    |

|     |                                                 | X103/X203 - DR15 female - Encoder Signals        | 33 |

# **Table of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                                               | 7  |

|-------------------------------------------------------------------------|----|

| FIGURE 2-1: TECHNICAL SPECIFICATION TIP102-XX                           | 8  |

| FIGURE 2-2: TECHNICAL SPECIFICATION TIP102-TM-XX                        | 9  |

| FIGURE 3-2: TIP102 V1.1 - ID PROM CONTENTS                              | 10 |

| FIGURE 4-1: REGISTER SET TIP102-1X                                      | 11 |

| FIGURE 4-2: REGISTER SET TIP102-2X                                      | 11 |

| FIGURE 4-3: INPUT AND STATUS REGISTER (INPSR)                           | 13 |

| FIGURE 4-4: OUTPUT CONTROL REGISTER (OUTCR)                             | 14 |

| FIGURE 4-5: COUNTER MASTER CONTROL REGISTER (MCR)                       | 15 |

| FIGURE 4-6: COUNTER INPUT CONTROL REGISTER (ICR)                        | 16 |

| FIGURE 4-7: COUNTER OUTPUT CONTROL REGISTER (OCCR)                      | 17 |

| FIGURE 4-8: QUADRATURE REGISTER (QR)                                    | 17 |

| FIGURE 4-9: OUTPUT STATUS REGISTER (OSR)                                | 18 |

| FIGURE 4-10: DAC DATA REGISTER (DACDA)                                  | 18 |

| FIGURE 4-11: ADC CONTROL AND STATUS REGISTER (ADCCS)                    | 19 |

| FIGURE 4-12: ADC DATA REGISTER (ADCDA)                                  | 19 |

| FIGURE 4-13: CONFIGURATION CONTROL REGISTER (CONCR)                     | 20 |

| FIGURE 4-14: INTERRUPT VECTOR REGISTER (INTVEC)                         | 21 |

| FIGURE 5-1: LS7166 - QUADRATURE MODE X1                                 | 22 |

| FIGURE 5-2: LS7166 - QUADRATURE MODE X2                                 | 22 |

| FIGURE 5-3: LS7166 - QUADRATURE MODE X4                                 | 22 |

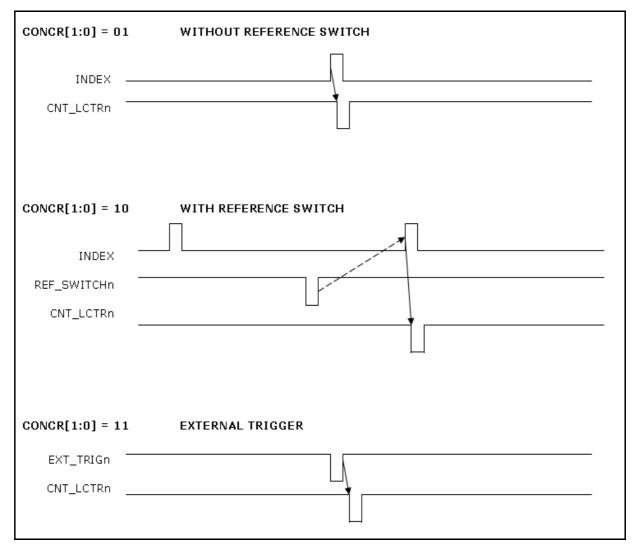

| FIGURE 5-4: REFERENCE MODES OF THE TIP102                               | 24 |

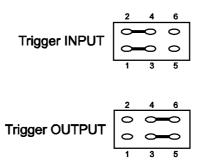

| FIGURE 7-1: JUMPER J1 (J200) CONFIGURATION FOR TRIGGER INPUT AND OUTPUT | 27 |

| FIGURE 7-2: JUMPER J1 (J200) CONFIGURATION FOR TRIGGER OUTPUT           | 28 |

| FIGURE 8-1: 50 PIN IP I/O CONNECTOR TIP102-XX                           | 29 |

| FIGURE 8-2: X101/X201 - DB9 FEMALE - SERVO AMPLIFIER SIGNALS            | 30 |

| FIGURE 8-3: X102/X202 - DB15 MALE - POWER AND I/O SIGNALS               | 32 |

| FIGURE 8-4: X103/X203 - DB15 FEMALE - ENCODER SIGNALS                   | 33 |

# 1 Product Description

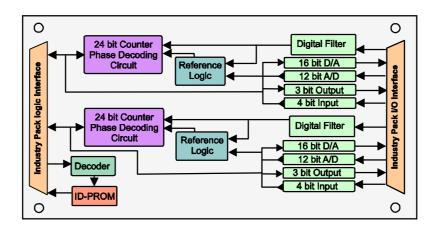

The TIP102 family is IndustryPack® compatible modules with complete one or two axes high precision motion control interfaces, using incremental encoder with RS422 or TTL signal level for position feedback. The transition module TIP102-TM-xx is required for the signal conditioning and optional galvanically isolation of the various input and output signals.

The position feedback is provided by an incremental encoder interface and a 24 bit up/down counter. The level of the encoder signals can be TTL or RS422. Optionally, the encoder signals can be isolated on the transition module by high speed optocouplers. The encoder signals pass a digital filter for noise suppression before they are fed into the counter and the reference logic. The counter is programmable for single, double and quadruples analysis of the encoder two phase signals.

Calibration of the position feedback to an absolute reference point is done by an adjustable reference logic. This logic incorporates several modes of operation and hardware configurations (Reference Switches, Encoder Index Pulse, External Triggers) for the generation of the reference condition. During normal operation, the automatic recalibration of the measurement system is practicable with the "auto reference" mode, whenever the system passes the reference location.

Two isolated 24V DC digital inputs have limit switch functionality. Each of these inputs drives a floating optocoupler output as hardware feedback. These outputs can be used to disable the power on the motor power amplifier, dependent on the actual direction. One additional isolated 24V digital input is for free use by the software, for example as emergency stop input. A floating optical output can be controlled by software, for example as enable signal for the motor power amplifier.

A 16 bit digital to analog converter (DAC) produces a +/-10V controller output signal which can be used as speed or torque source for the power amplifier of the motor drive system. A galvanically isolation of this signal with the help of an isolation amplifier will be supplied as a transition module option.

A 12 bit analog to digital converter (ADC) with a configurable input voltage range is also available.

Figure 1-1: Block Diagram

# 2 Technical Specification

### 2.1 TIP102-xx

| Interface                | Single Size IndustryPack® Logic Interface compliant to ANSI/VITA 4-1995                                         |  |  |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| ID ROM Data              | Format I                                                                                                        |  |  |

| I/O Space                | Used without wait states                                                                                        |  |  |

| Memory Space             | Not used                                                                                                        |  |  |

| Interrupts               | Interrupt 1 (IP signal INTREQ0#) for axis 1 Interrupt 2 (IP signal INTREQ1#) for axis 2                         |  |  |

| DMA                      | Not supported                                                                                                   |  |  |

| Clock Rate               | 8 MHz                                                                                                           |  |  |

| Module Type              | Type I                                                                                                          |  |  |

| Number of Axes           | TIP102-1x: 1 axis<br>TIP102-2x: 2 axes                                                                          |  |  |

| Encoder Interface        | Incremental encoder interface with 24 bit up/down counter                                                       |  |  |

| Input Count Frequency    | Up to 2 MHz                                                                                                     |  |  |

| Analog Input             | 1 ADC per axis, 12 bit, 10µs, input voltage +/-10V                                                              |  |  |

| Analog Input Overvoltage | Protection up to 25Vpp                                                                                          |  |  |

| Analog Output            | 1 DAC per axis, 16 bit, output voltage +/-10V                                                                   |  |  |

| Analog Output Current    | +/-5mA                                                                                                          |  |  |

| Digital Inputs           | 5 inputs per axis TTL level                                                                                     |  |  |

| Digital Outputs          | 2 outputs per axis TTL level                                                                                    |  |  |

| External Trigger         | TTL input and TTL output                                                                                        |  |  |

| Interface Connector      | 50-conductor flat cable                                                                                         |  |  |

| Power Requirements       | 25mA @ +5V DC<br>50mA @ +12V DC<br>45mA @ -12V DC                                                               |  |  |

| Temperature Range        | Operating -40° C to +85 °C<br>Storage -45°C to +125°C                                                           |  |  |

| MTBF                     | TIP102-1x: 698000 h<br>TIP102-2x: 561000 h                                                                      |  |  |

| Humidity                 | 5 – 95 % non-condensing                                                                                         |  |  |

| Weight                   | 28 g                                                                                                            |  |  |

| Transition Module        | TIP102-TM-xx is required, provides signal conditioning and optional isolation of digital and analog I/O signals |  |  |

Figure 2-1: Technical Specification TIP102-xx

# 2.2 Transition Module TIP102-TM-xx

| Board Data                                                      |                                                                                                                                                                                               |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Size                                                            | 1 VME slot (6U)                                                                                                                                                                               |  |  |

| Number of Axes                                                  | 1 axis for TIP102-1x                                                                                                                                                                          |  |  |

|                                                                 | 2 axes for TIP102-2x                                                                                                                                                                          |  |  |

| Encoder Interface                                               | Signal level TTL or RS422 optional galvanically isolated                                                                                                                                      |  |  |

| Analog Input                                                    | 1 input per axis, input voltage +/-10V optional isolated (ADC on TIP102)                                                                                                                      |  |  |

| Analog Input Overvoltage                                        | Overvoltage protection up to 100Vpp with galvanic isolation                                                                                                                                   |  |  |

|                                                                 | up to 12Vpp without galvanic isolation                                                                                                                                                        |  |  |

| Analog Output                                                   | 1 output per axis, overvoltage +/-10V optional isolated (DAC device is located on TIP102)                                                                                                     |  |  |

| Analog Output Current                                           | +/-20mA with galvanically isolation<br>+/-50mA without galvanically isolation                                                                                                                 |  |  |

| Digital Inputs per Axis (isolated)                              | General purpose input 24V DC Reference switch input 24V DC Limit switch 1 control input 24V DC Limit switch 2 control input 24V DC Encoder error input TTL (low active)                       |  |  |

| Digital Outputs per Axis (isolated)                             | Enable output 24V DC (+ "in position" LED indication)                                                                                                                                         |  |  |

| Digital Outputs directly driven from Inputs per Axis (isolated) | Limit_Switch_1 Output 24V DC Limit_Switch_2 Output 24V DC                                                                                                                                     |  |  |

| External Trigger                                                | 1 isolated TTL I/O per axis (jumper selectable input or output)                                                                                                                               |  |  |

| 24V Output Load                                                 | Max. 1000 ohm                                                                                                                                                                                 |  |  |

|                                                                 | Physical data                                                                                                                                                                                 |  |  |

| Power Requirements                                              | TIP102-TM-1x: 100mA typical @ +5V DC (without load), <60mA typical @ ±12V DC (without load) TIP102-TM-2x: 180mA typical @ +5V DC (without load), <90mA typical @ ±12V DC (without load)       |  |  |

| Temperature Range                                               | Operating 0° C to +70 °C<br>Storage -45°C to +125°C                                                                                                                                           |  |  |

| MTBF                                                            | TIP102-TM-10: 1271000 h, TIP102-TM-11: 759000 h TIP102-TM-12: 1091000 h, TIP102-TM-13: 644000 h TIP102-TM-20: 867000 h, TIP102-TM-21: 488000 h TIP102-TM-22: 785000 h, TIP102-TM-23: 436000 h |  |  |

| Humidity                                                        | 5 – 95 % non-condensing                                                                                                                                                                       |  |  |

| Weight                                                          | TIP102-TM-1x: min. 150g<br>TIP102-TM-2x: max. 250g                                                                                                                                            |  |  |

Figure 2-2: Technical Specification TIP102-TM-xx

# 3 ID PROM Contents

| Address | Function              | Contents               |

|---------|-----------------------|------------------------|

| 0x01    | ASCII 'I'             | 0x49                   |

| 0x03    | ASCII 'P'             | 0x50                   |

| 0x05    | ASCII 'A'             | 0x41                   |

| 0x07    | ASCII 'C'             | 0x43                   |

| 0x09    | Manufacturer ID       | 0xB3                   |

| 0x0B    | Model Number          | TIP102-1x: <b>0x0A</b> |

|         |                       | TIP102-2x: <b>0x0B</b> |

| 0x0D    | Revision              | 0x11                   |

| 0x0F    | Reserved              | 00x0                   |

| 0x11    | Driver-ID Low - Byte  | 00x0                   |

| 0x13    | Driver-ID High - Byte | 0x00                   |

| 0x15    | Number of bytes used  | 0x0C                   |

| 0x17    | CRC                   | TIP102-1x: <b>0x9E</b> |

|         |                       | TIP102-2x: <b>0xFF</b> |

Figure 3-1: TIP102 V1.1 - ID PROM Contents

# 4 IP Addressing

# 4.1 I/O Addressing

The complete register set of the TIP102 is accessible in the I/O space of the IP Module.

| Address | Symbol | Description                       | Size (Bit) | Access |

|---------|--------|-----------------------------------|------------|--------|

| 0x01    | INPSR1 | Input / Status Register           | 8          | R/C    |

| 0x03    | OUTCR1 | Output Control Register           | 8          | R/W    |

| 0x05    | CNTDA1 | Counter Data Register             | 8          | R/W    |

| 0x07    | CNTCS1 | Counter Control / Status Register | 8          | R/W    |

| 0x08    | DACDA1 | DAC Data Register                 | 16         | W      |

| 0x0B    | ADCCS1 | ADC Control / Status Register     | 8          | R/W    |

| 0x0C    | ADCDA1 | ADC Data Register                 | 16         | R      |

| 0x0F    | CONCR1 | Configuration Control Register    | 8          | R/W    |

| 0x3F    | INTVEC | Interrupt Vector Register         | 8          | R/W    |

Figure 4-1: Register Set TIP102-1x

On the TIP102-2x two axes motion controller, the second axis can be accessed through a second set of Control and Status Registers. Only the INTVEC Interrupt Vector Register is shared between both axes.

| Address | Symbol | Description                       | Size (Bit) | Access |

|---------|--------|-----------------------------------|------------|--------|

| 0x21    | INPSR2 | Input / Status Register           | 8          | R/C    |

| 0x23    | OUTCR2 | Output Control Register           | 8          | R/W    |

| 0x25    | CNTDA2 | Counter Data Register             | 8          | R/W    |

| 0x27    | CNTCS2 | Counter Control / Status Register | 8          | R/W    |

| 0x28    | DACDA2 | DAC Data Register                 | 16         | W      |

| 0x2B    | ADCCS2 | ADC Control / Status Register     | 8          | R/W    |

| 0x2C    | ADCDA2 | ADC Data Register                 | 16         | R      |

| 0x2F    | CONCR2 | Configuration Control Register    | 8          | R/W    |

Figure 4-2: Register Set TIP102-2x

# 4.2 Input and Status Register (INPSR)

The Input and Status Register INPSR1 (INPSR2) holds the actual status of all digital input lines as well as the status of the internal control logic (including interrupt generation, reference logic and digital filter).

| Bit | Symbol    | Description                                                                                                                                                                                               | Access | Reset<br>Value |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 7   | Interrupt | Interrupt Status                                                                                                                                                                                          | R/C    | 0              |

|     | Status    | 1 = corresponding axis has generated an interrupt request.                                                                                                                                                |        |                |

|     |           | Interrupts have to be enabled in the corresponding CONCR register first.                                                                                                                                  |        |                |

|     |           | Bit must be reset under software control by writing '1' to it.                                                                                                                                            |        |                |

|     |           | Bit is automatically cleared with the IP_RESET signal.                                                                                                                                                    |        |                |

| 6   | Refer.    | Reference Logic Status                                                                                                                                                                                    | R/C    | 0              |

|     | Done      | 1 = the TIP102 reference function, which was started with a specific command in the corresponding CONCR register, has completed successfully.                                                             |        |                |

|     |           | Bit must be reset under software control by a random write cycle to the corresponding CONCR.                                                                                                              |        |                |

|     |           | Bit is automatically cleared with the IP_RESET signal.                                                                                                                                                    |        |                |

| 5   | Encoder   | Latched Encoder Error Status                                                                                                                                                                              | R/C    | 0              |

|     | Error     | 1 = error in the timing of the encoder phase signals has been recognized or the encoder itself has reported an error.                                                                                     |        |                |

|     |           | The source of this flag is the error detection logic within the digital filter for the encoder phase signals or the input of the encoder signal ENC_ERROR.                                                |        |                |

|     |           | Bit must be reset under software control by writing '1' to it.  Bit is automatically cleared with the IP_RESET signal.                                                                                    |        |                |

| 4   | General   | General Purpose Input                                                                                                                                                                                     | R      |                |

|     | Input     | 1 = input is active                                                                                                                                                                                       |        |                |

|     |           | 0 = input is not active                                                                                                                                                                                   |        |                |

|     |           | This status bit corresponds to the General-Purpose input (Pin 5) on the X102/202 connector of the TIP102-TM transition module.                                                                            |        |                |

| 3   | Trigger   | External Trigger Input                                                                                                                                                                                    | R      |                |

|     | Input     | 1 = trigger input is active                                                                                                                                                                               |        |                |

|     |           | 0 = trigger input is not active                                                                                                                                                                           |        |                |

|     |           | This bit reflects the state of the external Trigger output switch (Pins 6 & 14) on the X102/202 connector of the TIP102-TM transition module.  The bidirectional Trigger I/O signal must be configured as |        |                |

| Bit | Symbol        | Description                                                                                                                                                                                                                                    | Access | Reset<br>Value |

|-----|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

|     |               | input when this bit is going to be used.  The transition module TIP102-TM-xx has one set of isolated trigger I/O signals, which are jumper configurable as trigger input or trigger output (see chapter "Trigger I/O Jumper Configuration").   |        |                |

| 2   | Ref<br>Switch | Reference Input (could also be used as another general purpose input)  1 = input is active  0 = input is not active  This status bit corresponds to the Reference input (Pin 12) on the X102/202 connector of the TIP102-TM transition module. | R      |                |

| 1   | High<br>Limit | High Limit Switch Control Input  1 = switch is activated  0 = switch is not activated  This status bit corresponds to the Limit_Switch_2_Control input (Pin 4) on the X102/202 connector of the TIP102-TM transition module.                   | R      |                |

| 0   | Low<br>Limit  | Low Limit Switch Control Input  1 = switch is activated  0 = switch is not activated  This status bit corresponds to the Limit_Switch_1_Control input (Pin 11) on the X102/202 connector of the TIP102-TM transition module.                   | R      |                |

Figure 4-3: Input and Status Register (INPSR)

### 4.3 Output Control Register (OUTCR)

The Output Control Register OUTCR1 (OUTCR2) controls the status of digital output signals.

| Bit | Symbol | Description                                                                                                                                                                                                                                                                           | Access | Reset<br>Value |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 7:2 |        | Not used                                                                                                                                                                                                                                                                              | R      | 0              |

| 1   |        | Status LED Bit controls the status of a LED located on the transition module. It can be read and written by software. This bit is automatically cleared with the IP_RESET signal.                                                                                                     | R/W    | 0              |

| 0   |        | Servo Amplifier Enable Bit controls the status of a floating optocoupler output which is normally connected to the enable input of the servo amplifier of the motor drive system. It can be read and written by software. This bit is automatically cleared with the IP_RESET signal. | R/W    | 0              |

Figure 4-4: Output Control Register (OUTCR)

### 4.4 Counter Data Register (CNTDA)

The Counter Data Register CNTDA1 (CNTDA2) is the data I/O port to the LS7166 counter chip. It is used to the read counter position or to write a preset value. Because the LS7166 is a 24 bit counter, and the Data Register is only 8 bit wide, each data transfer needs three read or write cycles in sequence.

### 4.4.1 Reading Counter Data

The 24 bit data value of the counter can only be accessed through a 24 bit Output Latch (OL) internal the LS7166. The data is latched into the OL under software control by setting bit 1 in the counter MCR register to '1' (see chapter "Master Control Register") or by an external hardware signal (see chapter "External Trigger Input"). After that the data can be read through the CNTDA1 (CNTDA2) in three cycles in sequence. The transfer is least significant byte first, most significant byte last.

The access to the three data bytes within the Output Latch (OL) is controlled by an internal address pointer, which is automatically incremented with each read cycle. This pointer should be reset directly prior the three read cycles by setting bit 0 in the counter MCR register (see chapter "Master Control Register").

### 4.4.2 Writing Counter Data

The 24 bit counter can be loaded from a 24 bit Preset Register (PR) internal the LS7166. The preset data has to be written to the PR through the CNTDA1 (CNTDA2) in three cycles in sequence. The transfer is least significant byte first, most significant byte last. The data is then transferred to the counter under software control by setting bit 3 in the counter MCR register to '1' (see chapter "Master Control Register"), by the reference logic (see chapter "Reference Logic") or by an external hardware signal (see chapter "External Trigger Input").

The access to the three data byte within the Preload Register (PR) is controlled by an internal address pointer, which is automatically incremented with each read cycle. This pointer should be reset directly prior the three read cycles by setting bit 0 in the counter MCR register (see chapter "Master Control Register").

### 4.5 Counter Control and Status Register (CNTCS)

The Counter Control and Status Register of the TIP102 is an interface to the internal Control and Status Registers of the LS7166 Counter. These registers have a special addressing mode. They use the two most significant bits (Bit 7:6) of the data bus to decide which register receives the data.

For a better understanding of these internal registers they are presented in the following section.

### 4.5.1 Master Control Register (MCR)

A write to the Counter Control and Status Register CNTCS1 (CNTCS2) with bit 6 = '0' and bit 7 = '0' will be a write to the Master Control Register of the LS7166 counter chip.

| Bit | Symbol                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                       | Access |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7   |                                                                                                                                                                                                                                              | Write '0'                                                                                                                                                                                                                         | W      |

| 6   |                                                                                                                                                                                                                                              | Write '0'                                                                                                                                                                                                                         | W      |

| 5   |                                                                                                                                                                                                                                              | Master Reset  1 = perform a master reset on the LS7166 counter chip and put it into initial state                                                                                                                                 |        |

| 4   |                                                                                                                                                                                                                                              | Reset COMPT 1 = clear the compare toggle flag COMPT                                                                                                                                                                               | W      |

| 3   |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                   | W      |

| 2   | Reset of CNTR, BWT, CYT, Set SIGN Register  1 = set the counter (CNTR) data value to zero, clear the borrow- and carry-toggle flag and set the sign bit.                                                                                     |                                                                                                                                                                                                                                   | W      |

| 1   | Transfer CNTR to OL  1 = latch the current 24 bit value of the counter (CNTR) into the OL register of the LS7166 counter chip for subsequent read-out. This bit can be combined with bit 0 to reset the OL address pointer at the same time. |                                                                                                                                                                                                                                   | W      |

| 0   |                                                                                                                                                                                                                                              | Reset PR/OL address pointer  1 = reset the internal PR/OL address pointer of the LS7166 counter chip, which is used during reads and writes to the CNTDA1/CNTDA2 register to access the three bytes forming the 24 bit data word. | W      |

Figure 4-5: Counter Master Control Register (MCR)

### 4.5.2 Input Control Register (ICR)

A write to the Counter Control and Status Register CNTCS1 (CNTCS2) with bit 6 = '1' and bit 7 = '0' will be a write to the Input Control Register of the LS7166 counter chip.

| Bit | Symbol | Description                                                                                                                                                                                                                            |   |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 7   |        | Write '0'                                                                                                                                                                                                                              | W |

| 6   |        | Write '1'                                                                                                                                                                                                                              |   |

| 5   |        | Configuration LCTR/LLTC pin of the LS7166  1 = event will latch the actual counter data value into the OL register.  0 = event (reference or external trigger) will load the counter with the contents of the PR register.             |   |

|     |        | On the TIP102 this pin is controlled by the reference and external trigger logic (see chapter "Functional Description").                                                                                                               |   |

| 4   |        | Configuration ABGT/RCTR                                                                                                                                                                                                                | W |

|     |        | Bit must always be set to '0' for the operation of the TIP102-xx.                                                                                                                                                                      |   |

| 3   |        | A/B Input Enable  1 = enable A and B counter inputs  0 = disable all counting functions                                                                                                                                                | W |

|     |        | For standard motion controller application of the TIP102 the counter should be always enabled.                                                                                                                                         |   |

| 2   |        | Decrement Counter once 1 = decrement the counter data value by one                                                                                                                                                                     | W |

| 1   |        | Increment Counter once 1 = increment the counter data value by one                                                                                                                                                                     | W |

| 0   |        | A/B Input Mode  1 = define A as count input and B as count direction input with B='0' for up and B='1' for down  0 = define A as up count input and B as down count input  In a standard motion controller application the TIP102 will | W |

|     |        | operate with an incremental encoder and the counter chip LS7166 programmed to quadrature mode by configuring the QR register (see chapter "Quadrature Register"). In this case the A/B input mode bit has no function.                 |   |

Figure 4-6: Counter Input Control Register (ICR)

## 4.5.3 Output Control Register (OCR)

A write to the Counter Control and Status Register CNTCS1 (CNTCS2) with bit 6 = '0' and bit 7 = '1' will be a write to the Output Control Register of the LS7166 counter chip.

For the standard motion controller application of the TIP102 the bits 1 to 3 of this register must always be programmed as '0'.

| Bit | Symbol                                                                      | Description                                                                                                                                                                                                                                                     | Access |

|-----|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7   |                                                                             | Write '1'                                                                                                                                                                                                                                                       | W      |

| 6   |                                                                             | Write '0'                                                                                                                                                                                                                                                       | W      |

| 5:4 |                                                                             | Input Trigger mode On TIP102 the output pin 16 of the LS7166 counter chip can be used for interrupt and output trigger impulse generation.  00 = CY# signal (carry) 01 = CYT signal (carry toggle flip flop) 10 = CY signal (carry) 11 = COMP# signal (compare) |        |

| 3:1 |                                                                             | Normal count mode                                                                                                                                                                                                                                               |        |

| 0   | Binary / BCD mode  1 = BCD mode  0 = binary mode, should be the normal case |                                                                                                                                                                                                                                                                 | W      |

Figure 4-7: Counter Output Control Register (OCCR)

### 4.5.4 Quadrature Register (QR)

A write to the Counter Control and Status Register CNTCS1 (CNTCS2) with bit 6 = '1' and bit 7 = '1' will be a write to the Quadrature Register of the LS7166 counter chip.

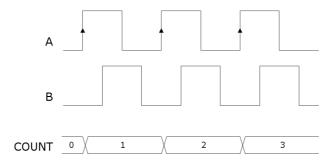

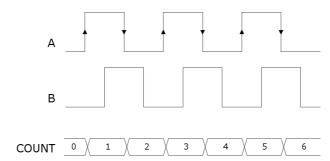

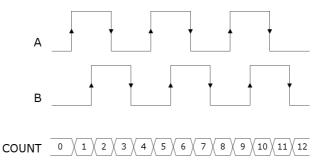

Because the TIP102 was designed to decode quadrature signals of encoders, one of the modes x1, x2 or x4 must be selected for standard operation of the module. Bit 2 to 5 are don't cares.

| Bit | Symbol | Description                                                                                                                                                               | Access |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 7   |        | Write '1'                                                                                                                                                                 | W      |

| 6   |        | Write '1'                                                                                                                                                                 |        |

| 5:2 |        | Don't care bits                                                                                                                                                           |        |

| 1:0 |        | Quadrature mode of the corresponding LS7166  00 = disable quadrature mode  01 = enable x1 quadrature mode  10 = enable x2 quadrature mode  11 = enable x4 quadrature mode | W      |

Figure 4-8: Quadrature Register (QR)

### 4.5.5 Output Status Register (OSR)

A read of the Counter Control and Status Register CNTCS1 (CNTCS2) will be a read of the Output Status Register of the LS7166 counter chip.

| Bit | Symbol                                                    | Description                                                                                             | Access |

|-----|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------|

| 7:5 |                                                           | Not used                                                                                                | -      |

| 4   |                                                           | UP / DOWN - Count direction indicator in quadrature mode.  0 = when counting down  1 = when counting up |        |

| 3   | Sign Bit 0 = when CNTR underflows 1 = when CNTR overflows |                                                                                                         | R      |

| 2   |                                                           | Compare Toggle Flip-Flop: Toggles every time CNTR equals PR.                                            |        |

| 1   |                                                           | Carry Toggle Flip-Flop: Toggles every time CNTR overflows.                                              | R      |

| 0   |                                                           | Borrow Toggle Flip-Flop: Toggles every time CNTR underflows.                                            |        |

Figure 4-9: Output Status Register (OSR)

## 4.6 DAC Data Register (DACDA)

The DAC Data Register DACDA1 (DACDA2) is the write only data register for the ±10V controller output signal of the TIP102. The 2's complement value written into this register is converted to the corresponding output voltage with a range of ±10V.

| Bit  | Symbol | Description                                                                                         |  |

|------|--------|-----------------------------------------------------------------------------------------------------|--|

| 15   | Sign   | 16 bit DAC data in 2's complement.                                                                  |  |

| 14:0 | Data   | Only 16 bit access is supported for this register. A read to this register will return random data. |  |

Figure 4-10: DAC Data Register (DACDA)

### 4.7 ADC Control and Status Register (ADCCS)

The ADC Control and Status Register ADCCS1 (ADCCS2) controls the function of the 12 bit ADC.

A data conversion is started by a write cycle to the ADCCS1 (ADCCS2). However the data value of this write is a don't care.

As long as the ADC is busy converting the bit 0 of the ADCCS1 (ADCCS2) will read as '1'.

| Bit | Symbol      | Description                            |     |

|-----|-------------|----------------------------------------|-----|

| 7:1 |             | These unused bits will be read as '0'. |     |

| 0   | ADC<br>Busy | ADC Busy 1 = ADC is busy               | R/W |

Figure 4-11: ADC Control and Status Register (ADCCS)

The unused bits 1 to 7 will always be read as '0' when reading the ADC Control and Status Register ADCCS1 (ADCCS2).

After power up the ADC is in a random state and requires two dummy conversions before operating correctly. This is based on the chip design of the ADC. All drivers from TEWS TECHNOLOGIES already include these two dummy conversions.

### 4.8 ADC Data Register (ADCDA)

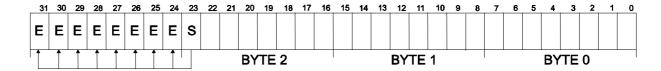

The ADC Data Register ADCDA1 (ADCDA2) holds the conversion result of the 12 bit ADC. It is left shifted by the hardware so the software reads a 16 bit 2's complement value.

| Bit  | Symbol | Description                                                 | Access |

|------|--------|-------------------------------------------------------------|--------|

| 15   | Sign   | 12 bit ADC Data in 2's complement, shifted to register bits | R      |

| 14:4 | Data   | 15:4.                                                       |        |

|      |        | Only 16 bit access is supported for this register.          |        |

| 3:0  |        | These unused bits will be read as '0'.                      |        |

Figure 4-12: ADC Data Register (ADCDA)

# 4.9 Configuration Control Register (CONCR)

The Configuration Control Register CONCR1 (CONCR2) controls the operation mode of the reference logic, the encoder configuration and interrupt generation.

Writing to this register will clear the reference done flag (bit 6) in the Input and Status Register INPSR1 (INPSR2).

The unused bits 5 to 7 will be read as '0' when reading the Configuration Control Register CONCR1 (CONCR2).

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Access | Reset<br>Value |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 7:5 |        | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -      | 0              |