# **TMPE863**

# 3 Channel High Speed Sync/Async Serial Interface

Version 1.0

### **User Manual**

Issue 1.0.0 January 2022

e-mail: info@tews.com www.tews.com

#### TMPE863-10R

3 Channel High Speed Sync/Async Serial Interface

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©2022 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description   | Date         |

|-------|---------------|--------------|

| 1.0.0 | Initial Issue | January 2022 |

# **Table of Contents**

| 1 | PR                                      | ODUC             | T DESCRIPTION                                                                                                                        | 9        |

|---|-----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2 | TE                                      | CHNIC            | AL SPECIFICATION                                                                                                                     | 10       |

| 3 | DN                                      | IA COI           | NTROLLER                                                                                                                             | 11       |

|   |                                         |                  | Transmit Descriptor Lists                                                                                                            |          |

|   | • • • • • • • • • • • • • • • • • • • • | 3.1.1            | Transmit Descriptor                                                                                                                  |          |

|   | 3.2                                     |                  | Receive Descriptor Lists                                                                                                             |          |

|   |                                         | 3.2.1            | Receive Descriptor                                                                                                                   |          |

|   |                                         | 3.2.2            | Receive Data Section Status Byte (HDLC Mode)                                                                                         |          |

|   |                                         | 3.2.3            | Receive Data Section Status Byte (ASYNC Modes)                                                                                       |          |

|   | 3.3                                     |                  | Interrupt Vector Queues                                                                                                              |          |

|   |                                         | 3.3.1            | Interrupt Vector Description                                                                                                         |          |

| 4 |                                         |                  | COMMUNICATION CONTROLLER                                                                                                             |          |

|   | 4.1                                     | Protoc           | ol Modes                                                                                                                             | 22       |

|   |                                         | 4.1.1            | HDLC Mode                                                                                                                            |          |

|   |                                         | 4.1.2            | ASYNC Mode                                                                                                                           |          |

|   |                                         |                  | Sources                                                                                                                              |          |

|   |                                         |                  | Rate Generation                                                                                                                      |          |

|   | 4.4                                     | Data E           | ncoding                                                                                                                              |          |

|   |                                         | 4.4.1            | NRZ and NRZI Encoding                                                                                                                |          |

|   |                                         | 4.4.2            | FM0 and FM1 Encoding                                                                                                                 |          |

|   | 4 5                                     | 4.4.3            | Manchester Encoding                                                                                                                  |          |

| _ |                                         |                  |                                                                                                                                      |          |

| 5 |                                         |                  | S MAP                                                                                                                                |          |

|   |                                         |                  | entifier                                                                                                                             |          |

| _ |                                         |                  | se Address Register                                                                                                                  |          |

| 6 |                                         |                  | R DESCRIPTION                                                                                                                        | _        |

|   |                                         |                  | mory Space Registers Overview                                                                                                        |          |

|   |                                         |                  | Registers Overview                                                                                                                   |          |

|   |                                         |                  | egisters Overview                                                                                                                    |          |

|   | 6.4                                     |                  | Registers                                                                                                                            |          |

|   |                                         | 6.4.1            | GCMDR – Global Command Register                                                                                                      |          |

|   |                                         | 6.4.2            | GSTAR – Global Status Register                                                                                                       |          |

|   |                                         | 6.4.3            | GMODE – Global Mode Register                                                                                                         |          |

|   |                                         | 6.4.4<br>6.4.5   | IQLENR0 – Interrupt Queue Length Register 0                                                                                          | 39<br>30 |

|   |                                         | 6.4.6            | IQSCCIRXBAR – Interrupt Queue SCCi Receiver Base Address Register                                                                    |          |

|   |                                         | 6.4.7            | IQSCCiTXBAR – Interrupt Queue SCCi Transmitter Base Address Register                                                                 |          |

|   |                                         | 6.4.8            | FIFOCR4 – FIFO Control Register 4                                                                                                    |          |

|   |                                         | 6.4.9            | IQCFGBAR – Interrupt Queue Configuration Base Address Register                                                                       | 41       |

|   |                                         | 6.4.10           | FIFOCR1 – FIFO Control Register 1                                                                                                    |          |

|   |                                         | 6.4.11           | CHICFG – Channel i Configuration Register                                                                                            |          |

|   |                                         | 6.4.12           | CHIBRDA - Channel i First/Base Receive Descriptor Address Register                                                                   |          |

|   |                                         | 6.4.13<br>6.4.14 | CHiBTDA – Channel i First/Base Transmit Descriptor Address Register  CHiCRDA – Channel i Current Receive Descriptor Address Register |          |

|   |                                         | 6.4.15           | CHICRDA – Channel i Current Transmit Descriptor Address Register                                                                     |          |

|   |                                         | 6.4.16           | CHiLRDA – Channel i Last Receive Descriptor Address Register                                                                         |          |

|   |                                         | 6.4.17           | CHiLTDA – Channel i Last Transmit Descriptor Address Register                                                                        |          |

|   |                                         | 6.4.18           | VR – Version Register                                                                                                                | 46       |

|   |                          | 6.4.1                               | ISPR – In-System-Programming Register                                      |                |

|---|--------------------------|-------------------------------------|----------------------------------------------------------------------------|----------------|

|   | 6.5                      | 6.4.2<br>SCC CI                     | GCTLR – Global Control Registerhannel Specific Registers                   |                |

|   | 0.0                      | 6.5.1                               | CMDR – Command Register (0x0100, 0x0180, 0x0200)                           |                |

|   |                          | 6.5.2                               | STAR – Status Register (0x0104, 0x0184, 0x0204)                            |                |

|   |                          | 6.5.3                               | CCR0 – Channel Configuration Register 0 (0x0108, 0x0188, 0x0208)           |                |

|   |                          | 6.5.4                               | CCR1 – Channel Configuration Register 1 (0x010C, 0x018C, 0x020C)           |                |

|   |                          | 6.5.5                               | CCR2 – Channel Configuration Register 2 (0x0110, 0x0190, 0x0210)           |                |

|   |                          | 6.5.6                               | BRR – Baud Rate Register (0x012C, 0x01AC, 0x022C)                          |                |

|   |                          | 6.5.7                               | TCR – Termination Character Register (0x0148, 0x01C8, 0x0248)              | 56             |

|   |                          | 6.5.8                               | IMR – Interrupt Mask Register (0x0154, 0x01D4, 0x0254)                     |                |

|   |                          | 6.5.9                               | ISR – Interrupt Status Register (0x0158, 0x01D8, 0x0258)                   |                |

|   |                          | 6.5.10                              | ACR – Additional Configuration Register (0x015C, 0x01DC, 0x025C)           | 60             |

| 7 | CC                       | NFIGU                               | IRATION HINTS                                                              | 62             |

|   | 7.1                      | Endian                              | Mode                                                                       | 62             |

|   |                          |                                     |                                                                            |                |

|   | 1 .Z                     | Config                              | uration EEPROM                                                             | 62             |

|   |                          | •                                   | uration EEPROMntial Line Wiring & Termination                              |                |

|   | 7.3                      | Differe                             | ntial Line Wiring & Termination                                            | 63             |

| _ | 7.3<br>7.4               | Differer<br>Transm                  | ntial Line Wiring & Termination<br>nit & Receive Clock Polarity            | 63<br>63       |

| 8 | 7.3<br>7.4               | Differer<br>Transm                  | ntial Line Wiring & Termination                                            | 63<br>63       |

| 8 | 7.3<br>7.4<br>I/O        | Differer<br>Transm                  | ntial Line Wiring & Termination<br>nit & Receive Clock Polarity            | 63<br>63       |

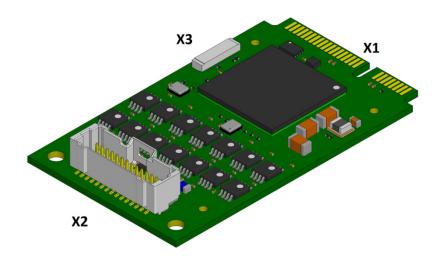

| 8 | 7.3<br>7.4<br>I/O<br>8.1 | Different Transm CONN Overvie       | ntial Line Wiring & Termination<br>nit & Receive Clock Polarity<br>IECTORS | 63<br>63<br>65 |

| 8 | 7.3<br>7.4<br>I/O<br>8.1 | Different Transm CONN Overvie Board | ntial Line Wiring & Termination                                            | 63<br>65<br>65 |

| 8 | 7.3<br>7.4<br>I/O<br>8.1 | Different Transm CONN Overvie       | ntial Line Wiring & Termination<br>nit & Receive Clock Polarity<br>IECTORS | 63656566       |

# **List of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                         | 9  |

|---------------------------------------------------|----|

| FIGURE 3-1: FPGA ON-CHIP BLOCK DIAGRAM            | 11 |

| FIGURE 4-1: HDLC ADDRESS MODE 0                   | 23 |

| FIGURE 4-2: CLOCK SOURCES                         | 26 |

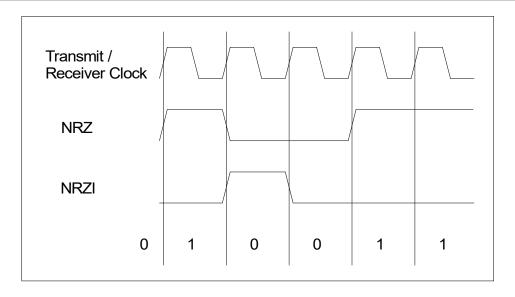

| FIGURE 4-3: NRZ AND NRZI DATA ENCODING            | 28 |

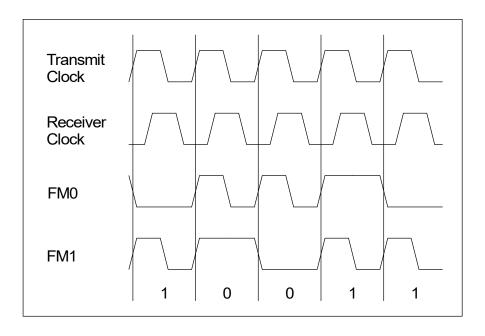

| FIGURE 4-4: FM0 AND FM1 DATA ENCODING             | 28 |

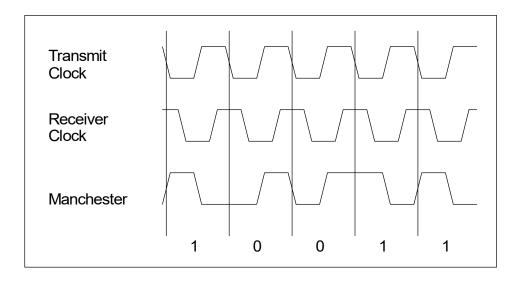

| FIGURE 4-5: MANCHESTER DATA ENCODING (ON TMPE863) | 29 |

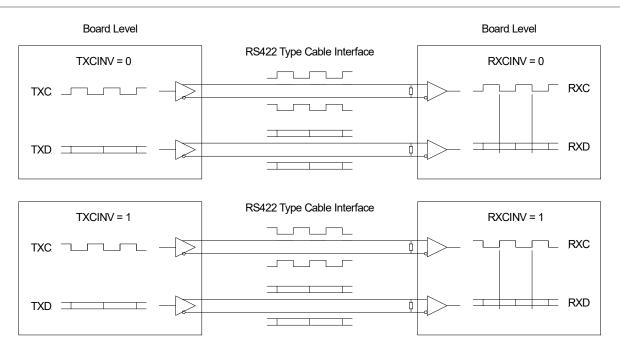

| FIGURE 7-1: TRANSMIT & RECEIVE CLOCK POLARITY     | 64 |

| FIGURE 8-1: I/O CONNECTOR OVERVIEW                | 65 |

# **List of Tables**

| TABLE 2-1: TECHNICAL SPECIFICATION                     | 10 |

|--------------------------------------------------------|----|

| TABLE 3-1: TRANSMIT DESCRIPTOR (IN SHARED/HOST MEMORY) | 13 |

| TABLE 3-2: RECEIVE DESCRIPTOR (IN SHARED/HOST MEMORY)  | 15 |

| TABLE 3-3: INTERRUPT QUEUES AND VECTORS                | 18 |

| TABLE 3-4: CONFIGURATION INTERRUPT VECTOR              | 19 |

| TABLE 3-5 : DMA INTERRUPT VECTOR                       |    |

| TABLE 3-6: DMAC INTERRUPT VECTOR SOURCE-IDS            | 19 |

| TABLE 3-7: SCC INTERRUPT VECTOR                        | 21 |

| TABLE 3-8: SCC INTERRUPT VECTOR SOURCE-IDS             | 21 |

| TABLE 4-1: PROTOCOL MODES                              | 22 |

| TABLE 5-1: PCI IDENTIFIER                              | 30 |

| TABLE 5-2: PCI BASE ADDRESS REGISTERS                  | 30 |

| TABLE 6-1: LOCAL REGISTER SPACE                        | 31 |

| TABLE 6-2: GLOBAL REGISTERS                            | 33 |

| TABLE 6-3: SCC REGISTERS                               | 34 |

| TABLE 6-4: GLOBAL COMMAND REGISTER                     | 36 |

| TABLE 6-5: GLOBAL STATUS REGISTER                      | 38 |

| TABLE 6-6: GLOBAL MODE REGISTER                        | 38 |

| TABLE 6-7: INTERRUPT QUEUE LENGTH REGISTER 0           | 39 |

| TABLE 6-8: INTERRUPT QUEUE LENGTH REGISTER 1           | 39 |

| TABLE 6-9: IQSCCIRXBAR REGISTER                        | 40 |

| TABLE 6-10: IQSCCITXBAR REGISTER                       | 40 |

| TABLE 6-11: FIFO CONTROL REGISTER 4                    | 41 |

| TABLE 6-12: IQCFGBAR REGISTER                          | 41 |

| TABLE 6-13: FIFO CONTROL REGISTER 1                    | 42 |

| TABLE 6-14: CHICFG REGISTER                            | 44 |

| TABLE 6-15: CHIBRDA REGISTER                           | 45 |

| TABLE 6-16: CHIBTDA REGISTER                           | 45 |

| TABLE 6-17: CHIFRDA REGISTER                           | 45 |

| TABLE 6-18: CHIFTDA REGISTER                           | 45 |

| TABLE 6-19: CHILRDA REGISTER                           | 46 |

| TABLE 6-20: CHILTDA REGISTER                           | 46 |

| TABLE 6-21: VERSION REGISTER                           | 46 |

| TABLE 6-22: ISPR REGISTER                              | 47 |

| TABLE 6-23: GLOBAL CONTROL REGISTER                    | 48 |

| TABLE 6-24: COMMAND REGISTER                           | 49 |

| TABLE 6-25: STATUS REGISTER                            | 50 |

| TABLE 6-26: CHANNEL CONFIGURATION REGISTER 0           | 51 |

| TABLE 6-27: CHANNEL CONFIGURATION REGISTER 1           | 53 |

| TABLE 6-28: CHANNEL CONFIGURATION REGISTER 2           | 55 |

| TABLE 6-29: BAUD RATE REGISTER                         | 56 |

|                                                        |    |

| TABLE 6-30: TERMINATION CHARACTER REGISTER    | 56 |

|-----------------------------------------------|----|

| TABLE 6-31: INTERRUPT MASK REGISTER           | 57 |

| TABLE 6-32: INTERRUPT STATUS REGISTER         | 59 |

| TABLE 6-33: ADDITIONAL CONFIGURATION REGISTER | 61 |

| TABLE 7-1: CONFIGURATION EEPROM MAP           | 63 |

| TABLE 8-1: SYSTEM CONNECTOR                   | 66 |

| TABLE 8-2: SYSTEM CONNECTOR PIN ASSIGNMENT    | 66 |

| TABLE 8-3: I/O CONNECTOR                      | 67 |

| TABLE 8-4: I/O CONNECTOR PIN ASSIGNMENT       | 67 |

| TABLE 8-5 : JTAG CONNECTOR                    | 68 |

# 1 Product Description

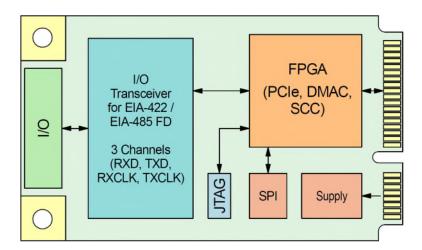

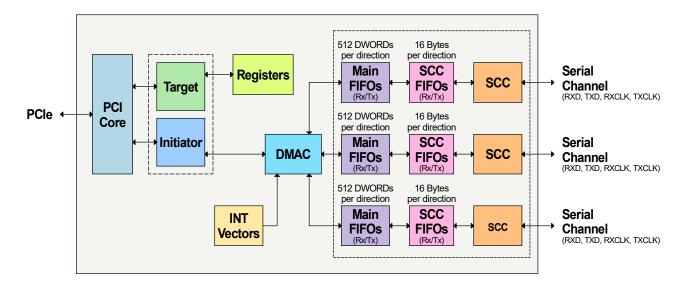

The TMPE863 is a standard full PCI Express Mini Card, providing three high speed serial data communication channels.

The serial communication controller is implemented in FPGA logic along with the bus master capable PCIe interface, guaranteeing long term availability and having the option to implement additional functions in the future.

Data transfer to and from host memory is handled via TMPE863 initiated DMA cycles for minimum host/CPU intervention.

Each channel has a receive and transmit FIFO of 512 long words (32 bit) per channel for high data throughput.

Several serial communication protocols are supported for each channel, such as asynchronous (with oversampling), isochronous, synchronous and HDLC mode.

Available signal encodings for synchronous data communication are NRZ, NRZI, FM0, FM1 and Manchester.

On-Board clock generation provides a 14.7456 MHz clock for standard asynchronous baud rates, 10 MHz for the 10 Mbit/s synchronous data rate and 24 MHz for other baud or data rates.

Each channel provides various interrupt sources with support for MSI and legacy interrupts (INTA).

The Differential I/O lines for EIA-422, EIA-485 (Full-Duplex) are terminated with 120  $\Omega$  on-board. Receive Data (RxD +/-), Transmit Data (TxD +/-), Receive Clock (RxC +/-), Transmit Clock (TxC +/-) are available.

The I/O signals are accessible through a 30 pin Pico-Clasp latching connector.

The TMPE863 provides a basic heatsink to facilitate thermal management. The heatsink can be used to install additional cooling solutions like passive or active heatsinks or to provide a thermal connection to an enclosure.

Figure 1-1: Block Diagram

# 2 Technical Specification

| PCI Express Mini Card conforming to   PCI Express Mini Card conforming to   PCI Express Mini Card Electromech. Specification, Revision 2.0   Card Type: Full-Mini Card (50.95 mm x 30 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DMO latarfa a           |                                                           |                                                           |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| Mechanical Interface   PCI Express Mini Card Electromech. Specification, Revision 2.0 Card Type; Full-Mini Card (50.95 mm x 30 mm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PMC Interface           | 1                                                         |                                                           |  |  |  |  |

| Card Type: Full-Mini Card (50.95 mm x 30 mm)  PCI Express xx 1 Link conforming to PCI Express Sase Specification, Revision 2.1 (Xilinx) The TMPE863 does not support the USB interface  Main On Board Devices  FPGA Xilinx Artix FPGA SPI Flash 128 Mbit SPI-Flash  I/O Interface  Number of Channels 3  Signals per Channel RXD±, TXD±, RXCLK±, TXCLK± (plus common GND)  Digital I/O Interface 12 differential EIA-422 / EIA-485 I/O lines  Digital I/O Transceiver 65HVD75D (or compatible)  Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte) Main Receive-FIFO per channel: up to 16 Byte SCC Receive-FIFO per channel: 16 Byte  SCC Receive-FIFO per channel: 16 Byte  SCC Receive-FIFO per channel: 16 Byte  Synchronous: 2 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes)  Asynchronous: 2 Mbit/s  I/O Connector 30 pos. Pico-Clasp latching connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range Operating Storage -40°C to +85°C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2 Environment: Gg 20°C. The MTBF calculation is based on component FIT rates provided by the component supplies. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |                                                           | · · · · · · · · · · · · · · · · · · ·                     |  |  |  |  |

| PCI Express x1 Link conforming to PCI Express Base Specification, Revision 2.1 (Xilinx) The TMPE863 does not support the USB interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mechanical Interface    |                                                           |                                                           |  |  |  |  |

| ### PCI Express Base Specification, Revision 2.1 (Xilinx) The TMPE863 does not support the USB interface  ### Main On Board Devices    FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         | 7.                                                        | Card Type: Full-Mini Card (50.95 mm x 30 mm)              |  |  |  |  |

| Main On Board Devices FPGA Xilinx Artix FPGA SPI Flash 128 Mbit SPI-Flash I/O Interface Number of Channels 3 Signals per Channel RXD±, TXD±, RXCLK±, TXCLK± (plus common GND) Digital I/O Interface 12 differential EIA-422 / EIA-485 I/O lines Digital I/O Transceiver 65HVD75D (or compatible)  FIFOs 65HVD75D (or compatible) Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte) Main Receive-FIFO per channel: 16 Byte SCC Receive-FIFO per channel: 16 Byte SCC Receive-FIFO per channel: 16 Byte SCC Receive-FIFO per channel: 2 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s I/O Connector 30 pos. Pico-Clasp latching connector Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC) Temperature Range 7.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2 Environment: \$G_8 20^{\circ}C The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                                           | •                                                         |  |  |  |  |

| Main On Board Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Electrical Interface    |                                                           | ·                                                         |  |  |  |  |

| SPI Flash   128 Mbit SPI-Flash   128 Mbit SPI-Flash   1/0 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         | The TMPE86                                                | 33 does not support the USB interface                     |  |  |  |  |

| SPI Flash   128 Mbit SPI-Flash   1/0 Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Main On Board Devices   | 1                                                         |                                                           |  |  |  |  |

| I/O Interface   Number of Channels   3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FPGA                    | Xilinx Artix F                                            | PGA                                                       |  |  |  |  |

| Number of Channels       3         Signals per Channel       RXD±, TXD±, RXCLK±, TXCLK± (plus common GND)         Digital I/O Interface       12 differential EIA-422 / EIA-485 I/O lines         Digital I/O Transceiver       65HVD75D (or compatible)         Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte)         Main Receive-FIFO per channel: 512 DWORD (2 Kbyte)         SCC Transmit-FIFO per channel: up to 16 Byte         SCC Receive-FIFO per channel: 16 Byte         Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes)         Asynchronous: 2 Mbit/s         I/O Connector       30 pos. Pico-Clasp latching connector         Physical Data       +1.5V Supply: 200mA         +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)         Temperature Range       Operating Storage -40°C to +85 °C -40°C to +125°C         1.200.000 h MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.         Humidity       5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPI Flash               | 128 Mbit SPI-Flash                                        |                                                           |  |  |  |  |

| Signals per Channel   RXD±, TXD±, RXCLK±, TXCLK± (plus common GND)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I/O Interface           |                                                           |                                                           |  |  |  |  |

| Digital I/O Interface       12 differential EIA-422 / EIA-485 I/O lines         Digital I/O Transceiver       65HVD75D (or compatible)         Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte)         Main Receive-FIFO per channel: 512 DWORD (2 Kbyte)         SCC Transmit-FIFO per channel: up to 16 Byte         SCC Receive-FIFO per channel: 16 Byte         Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes)         Asynchronous: 2 Mbit/s         I/O Connector       30 pos. Pico-Clasp latching connector         Physical Data       +1.5V Supply: 200mA         +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)         Temperature Range       Operating Storage -40°C to +85 °C -40°C to +125°C         1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.         Humidity       5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Number of Channels      | 3                                                         |                                                           |  |  |  |  |

| Digital I/O Transceiver  65HVD75D (or compatible)  Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte)  Main Receive-FIFO per channel: 512 DWORD (2 Kbyte)  SCC Transmit-FIFO per channel: up to 16 Byte  SCC Receive-FIFO per channel: 16 Byte  Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes)  Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  Power Requirements  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C.  The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Signals per Channel     | RXD±, TXD±, RXCLK±, TXCLK± (plus common GND)              |                                                           |  |  |  |  |

| Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte) Main Receive-FIFO per channel: 512 DWORD (2 Kbyte) SCC Transmit-FIFO per channel: up to 16 Byte SCC Receive-FIFO per channel: 16 Byte Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Operating -40°C to +85 °C Storage -40°C to +125°C  1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 - 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Digital I/O Interface   | 12 differential EIA-422 / EIA-485 I/O lines               |                                                           |  |  |  |  |

| Main Receive-FIFO per channel: 512 DWORD (2 Kbyte) SCC Transmit-FIFO per channel: up to 16 Byte SCC Receive-FIFO per channel: 16 Byte  Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Digital I/O Transceiver | 65HVD75D (                                                | or compatible)                                            |  |  |  |  |

| SCC Transmit-FIFO per channel: up to 16 Byte SCC Receive-FIFO per channel: 16 Byte  Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85°C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 - 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         | Main Transmit-FIFO per channel: up to 512 DWORD (2 Kbyte) |                                                           |  |  |  |  |

| SCC Transmit-FIFO per channel: up to 16 Byte SCC Receive-FIFO per channel: 16 Byte SCC Receive-FIFO per channel: 16 Byte Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 - 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FIFO                    | , , , , , , , , , , , , , , , , , , , ,                   |                                                           |  |  |  |  |

| Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes) Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Operating Storage  Operating Storage  1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>8</sub> 20°C.  The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  Synchronous: 10 Mbit/s (Non-DPLL Modes), 2 Mbit/s (DPLL Modes | FIFOS                   | SCC Transm                                                | SCC Transmit-FIFO per channel: up to 16 Byte              |  |  |  |  |

| Maximum Data Rate       Modes)<br>Asynchronous: 2 Mbit/s         I/O Connector       30 pos. Pico-Clasp latching connector         Physical Data       +1.5V Supply: 200mA<br>+3.3VAUX Supply:<br>425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)         Temperature Range       Operating<br>Storage       -40°C to +85 °C<br>-40°C to +125°C         MTBF       1.200.000 h<br>MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: GB 20°C.<br>The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.         Humidity       5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | SCC Receive-FIFO per channel: 16 Byte                     |                                                           |  |  |  |  |

| Asynchronous: 2 Mbit/s  I/O Connector  Physical Data  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |                                                           |                                                           |  |  |  |  |

| I/O Connector         Physical Data       +1.5V Supply: 200mA         Power Requirements       +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)         Temperature Range       Operating Storage       -40°C to +85 °C -40°C to +125°C         MTBF       1.200.000 h MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.         Humidity       5 - 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maximum Data Rate       | ,                                                         |                                                           |  |  |  |  |

| Power Requirements  +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating -40°C to +85 °C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1/0 0                   |                                                           |                                                           |  |  |  |  |

| +1.5V Supply: 200mA +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | 30 pos. Pico-                                             | -Clasp latching connector                                 |  |  |  |  |

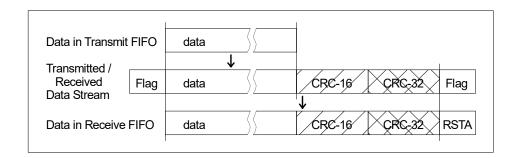

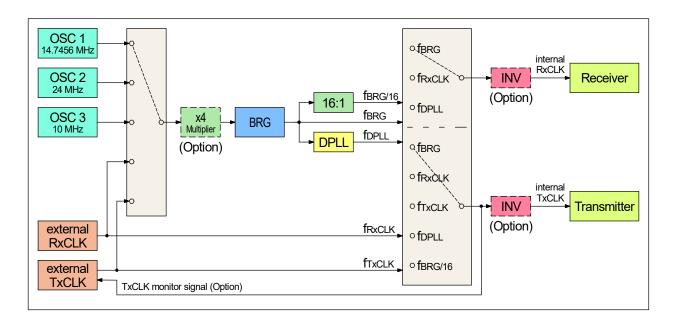

| +3.3VAUX Supply: 425mA Idle, add appr. 90mA per active Channel (10MHz HDLC)  Temperature Range  Operating Storage -40°C to +85 °C -40°C to +125°C  1.200.000 h  MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C.  The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation.  Humidity  5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Physical Data           |                                                           |                                                           |  |  |  |  |