# **TPMC150**

## 4, 3, 2 or 1 Channel Synchro/Resolver-to-Digital Converter

Version 1.0

### **User Manual**

Issue 1.0.7

August 2021

#### TPMC150-10R

4 Channel Synchro/Resolver-to-Digital Converter

#### TPMC150-11R

3 Channel Synchro/Resolver-to-Digital Converter

#### TPMC150-12R

2 Channel Synchro/Resolver-to-Digital Converter

#### **TPMC150-13R**

1 Channel Synchro/Resolver-to-Digital Converter

## Signal Conditioning Adapter

TPMC150-A1-xxR

Resolver interface

#### TPMC150-A2-xxR

Resolver interface with reference oscillator

#### **TPMC150-A3-xx**

High precision synchro/resolver interface

#### **TPMC150-A4-xx**

High precision synchro/resolver interface with reference oscillator

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

#### ©2021 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                               | Date           |

|-------|-------------------------------------------------------------------------------------------|----------------|

| -     | Preliminary Issue                                                                         | February 2003  |

| 1.0   | First Issue                                                                               | June 2003      |

| 1.1   | Corrected storage temperature, corrected typos                                            | March 2005     |

| 1.2   | Corrected Connection Examples                                                             | January 2006   |

| 1.3   | New address TEWS LLC                                                                      | September 2006 |

| 1.0.4 | New notation for HW Engineering Documentation Releases                                    | February 2013  |

| 1.0.5 | General Revision                                                                          | August 2014    |

| 1.0.6 | Technical Specification Table Update - Added Power Requirements for TPMC150-A2/A4 Adapter | November 2014  |

| 1.0.7 | Changed I/O connector<br>Changed RDC19230 to RD-19231                                     | August 2021    |

# **Table of Contents**

| 1 | PRODUCT DESCRIPTION                                 | 7   |

|---|-----------------------------------------------------|-----|

| 2 | TECHNICAL SPECIFICATION                             | 9   |

|   | 2.1 Tracking Rate Characteristics                   | 10  |

|   | 2.2 Velocity Output Characteristics                 |     |

|   | 2.3 Digital Input Characteristics                   | 11  |

| 3 | TPMC150 LOCAL SPACE ADDRESSING                      | 12  |

|   | 3.1 PCI9030 Local Space Configuration               | 12  |

|   | 3.2 Register Address Space                          | 13  |

|   | 3.2.1 Global Control/Status Register                |     |

|   | 3.2.2 Interrupt Control/Status Register             |     |

|   | 3.2.3 Digital Input Register                        |     |

|   | 3.2.5 Channel Data Register                         |     |

|   | 3.2.6 Channel Status Register                       |     |

|   | 3.2.7 Encoder Counter Preload/Data Register         | 20  |

| 4 | PCI9030 TARGET CHIP                                 | 21  |

|   | 4.1 PCI Configuration Registers (PCR)               | 21  |

|   | 4.1.1 PCI9030 Header                                |     |

|   | 4.1.2 PCI Base Address Initialization               |     |

|   | 4.2 Local Configuration Register (LCR)              |     |

|   | 4.3 Configuration EEPROM4.4 Local Software Reset    |     |

| _ |                                                     |     |

| 5 | CONFIGURATION HINTS                                 |     |

|   | 5.1 Software Reset (Controller and LRESET#)         |     |

|   | 5.2 Big / Little Endian                             |     |

|   | 5.3 Local read/write                                |     |

|   | 5.4 Changing Resolution on the Fly                  |     |

|   | 5.5 Operating Modes                                 |     |

|   | 5.5.1 Converter Operating Modes                     |     |

|   | 5.6 Binary Angle Relationships                      |     |

| 6 | SIGNAL CONDITIONING ADAPTER                         |     |

|   | 6.1 Signal Conditioning Adapter Characteristics     |     |

|   | 6.2 Required Synchro/Resolver specifications        |     |

|   | 6.3 Connector Pin Assignments                       |     |

|   | 6.3.1 20 Pin Connector – Front I/O Side             |     |

|   | 6.3.2 20 Pin Connector - Converter Side             | 38  |

| 7 | INSTALLATION HINTS                                  | 39  |

|   | 7.1 Connection Examples                             |     |

|   | 7.1.1 Resolver with external reference              |     |

|   | 7.1.2 Resolver with internal reference              |     |

|   | 7.1.3 Single ended resolver with external reference |     |

|   | •                                                   |     |

| 8 | PIN ASSIGNMENT - I/O CONNECTOR                      | 4 T |

### **LIST OF FIGURES**

| IGURE 1-1 : SIGNAL CONDITIONING ADAPTER TPMC150-A1/A3                            | 7   |

|----------------------------------------------------------------------------------|-----|

| IGURE 1-2 : SIGNAL CONDITIONING ADAPTER TPMC150-A2/A4 WITH REFERENCE OSCILLATOR. | 7   |

| IGURE 1-3: BLOCK DIAGRAM TPMC150-10R                                             | 8   |

| IGURE 2-1 : VELOCITY RIPPLE FILTER                                               | 11  |

| IGURE 2-2 : DIGITAL INPUT WIRING                                                 | 11  |

| IGURE 5-1 : ENCODER SIGNAL INTERPRETATION                                        | 30  |

| IGURE 5-2 : ENCODER PRELOAD EXAMPLE                                              | 32  |

| IGURE 6-1 : SIGNAL CONDITIONING ADAPTER TPMC150-A1/A3                            | 35  |

| IGURE 6-2 : SIGNAL CONDITIONING ADAPTER TPMC150-A2/A4 WITH REFERENCE OSCILLATOR. | 35  |

| IGURE 7-1 : TPMC150 ADAPTER PLACEMENT                                            | 39  |

| IGURE 7-2 : RESOLVER WITH EXTERNAL REFERENCE                                     | 40  |

| IGURE 7-3 : RESOLVER WITH INTERNAL REFERENCE                                     | 40  |

| IGURE 7-4 : SINGLE ENDED RESOLVER WITH EXTERNAL REFERENCE                        | 41  |

| IGURE 7-5 : SYNCHRO WITH EXTERNAL REFERENCE                                      | .41 |

### **LIST OF TABLES**

| TABLE 2-1: TECHNICAL SPECIFICATION TPMC150                   | 9  |

|--------------------------------------------------------------|----|

| TABLE 2-2 : TRACKING RATE CHARACTERISTICS                    | 10 |

| TABLE 2-3: VELOCITY OUTPUT CHARACTERISTICS                   | 10 |

| TABLE 2-4 : DIGITAL INPUT CHARACTERISTICS                    | 11 |

| TABLE 3-1 : PCI9030 LOCAL SPACE CONFIGURATION                | 12 |

| TABLE 3-2 : REGISTER ADDRESS SPACE                           | 13 |

| TABLE 3-3 : GLOBAL CONTROL/STATUS REGISTER                   | 14 |

| TABLE 3-4: INTERRUPT CONTROL/STATUS REGISTER                 |    |

| TABLE 3-5 : INPUT INTERRUPT CONFIGURATION                    | 15 |

| TABLE 3-6 : DIGITAL INPUT REGISTER                           | _  |

| TABLE 3-7 : CHANNEL CONTROL REGISTER                         | 17 |

| TABLE 3-8 : CHANNEL DATA REGISTER                            |    |

| TABLE 3-9: LSB POSITION                                      | 18 |

| TABLE 3-10: CHANNEL STATUS REGISTER                          | 19 |

| TABLE 3-11: ENCODER COUNTER PRELOAD/DATA REGISTER            | 20 |

| TABLE 4-1 : PCI9030 HEADER                                   |    |

| TABLE 4-2 : PCI9030 PCI BASE ADDRESS USAGE                   | 22 |

| TABLE 4-3 : PCI9030 LOCAL CONFIGURATION REGISTER             | 23 |

| TABLE 4-4 : CONFIGURATION EEPROM TPMC150-XX                  | 24 |

| TABLE 5-1 : LOCAL BUS LITTLE/BIG ENDIAN                      | 26 |

| TABLE 5-2 : INCREMENTAL ENCODER RESOLUTION                   | 29 |

| TABLE 5-3 : ENCODER SIGNAL ANALYSIS MODES                    | 30 |

| TABLE 5-4 : ENCODER COUNT PER REVOLUTION                     |    |

| TABLE 5-5 : ENCODER REFERENCE MODES                          | 31 |

| TABLE 5-6 : BINARY ANGLE RELATIONSHIPS                       | 34 |

| TABLE 6-1 : TPMC150 ADAPTER VARIANTS                         | 36 |

| TABLE 6-2 : TECHNICAL SPECIFICATION TPMC150-A1 – TPMC150-A4  |    |

| TABLE 6-3 : PIN ASSIGNMENT - 20 PIN CONNECTOR FRONT I/O SIDE |    |

| TABLE 6-4 : PIN ASSIGNMENT - 20 PIN CONNECTOR CONVERTER SIDE | 38 |

| TABLE 8-1: PIN ASSIGNMENT I/O CONNECTOR                      | 42 |

# 1 Product Description

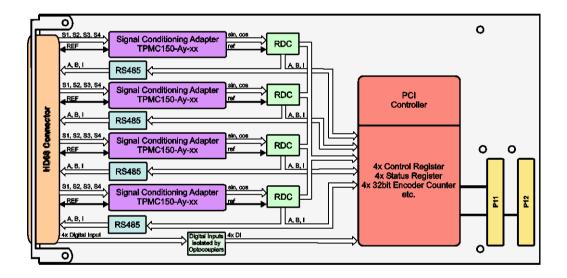

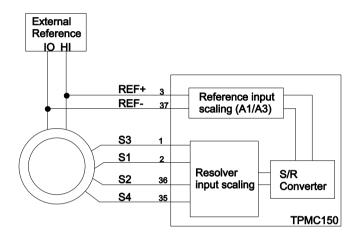

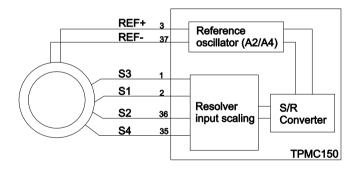

The TPMC150 is a standard single-width 32 bit PMC module providing four (TPMC150-10R), three (TPMC150-11R), two (TPMC150-12R) or one channel (TPMC150-13R) of a Tracking Synchro/Resolver-To-Digital Converter (RDC) with a converter accuracy of 2 arcmin + 1LSB.

The TPMC150 is designed for use in high performance commercial and industrial systems. It can be used for many applications like motor control, robot axis control, process control, radar antenna position information, and CNC machine tooling.

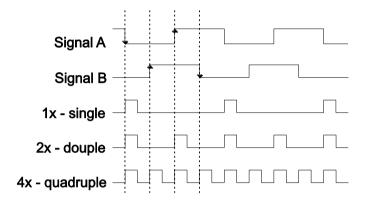

Each of the up to four RDC channels on the TPMC150 utilizes DDC's versatile state-of-the-art Tracking Synchro/Resolver-To-Digital Converter RD-19231with programmable resolution. Resolution programming allows selection of 10, 12, 14 or 16 bit conversion. This combines the high tracking rate of a 10 bit converter with the precision of a 16 bit converter. The RD-19231 provides incremental encoder emulation. Encoder phase signals A, B and Index I are fed to an on board 32 bit up-/down encoder counter with preload and output register. Additionally the synthesized encoder signals are available for external use via RS485/422 output drivers. The RD-19231provides a 4V velocity output with a linearity of typically 0.25%, which can be used to replace a tachometer. A 24V isolated digital input per channel can be used as general purpose input or as reference input.

A 'Simultaneous Read' function allows latching of the actual values of the selected converters at the same time.

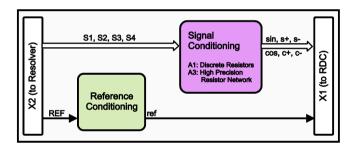

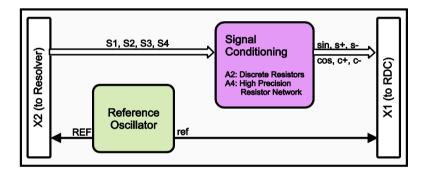

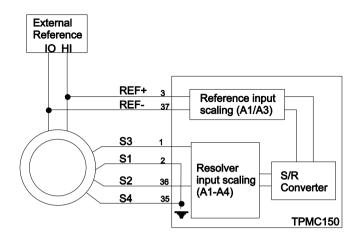

Figure 1-1: Signal Conditioning Adapter TPMC150-A1/A3

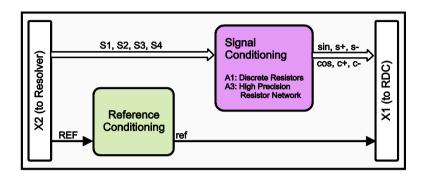

Signal Conditioning Adapters (TPMC150-Ay-xx) are required for each channel to adapt the signal levels of the Synchro/Resolver to the RD-19231and to configure the optional reference oscillator input/output. The Signal Conditioning Adapters will be built individually to customer specification of the synchro or resolver specifications, and are factory installed on the TPMC150.

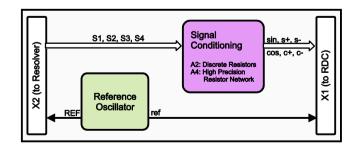

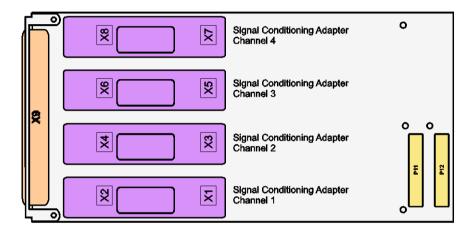

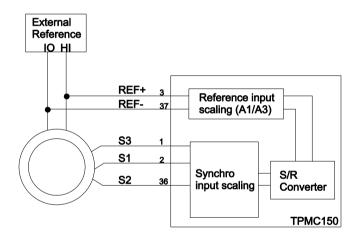

Figure 1-2: Signal Conditioning Adapter TPMC150-A2/A4 with reference oscillator

Four types of Signal Conditioning Adapters are available to adapt the signal levels of the Synchro/Resolver to the RD-19231: The TPMC150-A1-xxR and the TPMC150-A2-xxR use high precision, low TK discrete resistors. These Adapters are mainly used for resolver applications. The TPMC150-A3-xx and the TPMC150-A4-xx use a high precision resistor network with matched resistors. These Adapters are mainly used for synchro applications or resolver applications which require highest accuracy. Additionally the TPMC150-A2-xxR and the TPMC150-A4-xx offer an on board reference oscillator with factory selectable frequencies in the range of 2 kHz to 10 kHz.

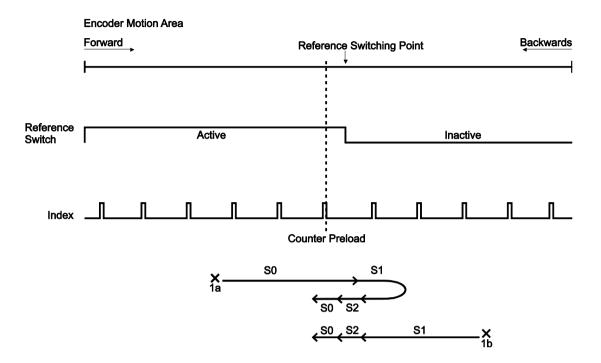

The on board encoder counter for each channel is a 32 bit up-/down counter with preload and output register. The encoder counter is fed with the emulated A, B and Index signals from the RD-19231. The counters are programmable for single, double and quad analysis of the incremental encoder signals. The counter can be manually or automatically loaded with the value of the preload register, depending on mode. An 'Auto Reference Mode' provides the possibility of automatic preload of the encoder counter during normal operation, whenever the motion system passes the reference position. A 'Simultaneous Read' function allows latching of the actual values of the selected encoder counters. These values can then be read successively without interfering with normal counter function.

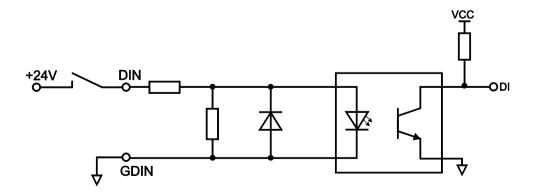

The TPMC150 offers one digital 24V input per channel which is galvanically isolated by optocouplers. A high performance input circuit ensures a defined switching point and polarization protection against confusing the pole. The inputs are electronically debounced. Each of the four digital 24V inputs can generate an interrupt, triggered on rising or falling edge. Depending on the selected mode the input can be used as general purpose input or as reference input.

Figure 1-3: Block Diagram TPMC150-10R

# 2 Technical Specification

| Mechanical Interface      |                                                                                                                                           | ne Card (PMC) Interface                             |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Floridation Interfere     | Single Size                                                                                                                               | P                                                   |  |  |

| Electrical Interface      | PCI Rev. 2.2<br>33 MHz / 32                                                                                                               | ·                                                   |  |  |

|                           |                                                                                                                                           | PCI Signaling Voltage                               |  |  |

| On Board Devices          | 3.3V and 3V                                                                                                                               | r Ci Signaling Voltage                              |  |  |

|                           | DCIO030 (DI                                                                                                                               | .X Technology)                                      |  |  |

| PCI Target Chip           | RD-19231                                                                                                                                  | .x reciniology)                                     |  |  |

| Converter Chip            |                                                                                                                                           | La 40 40 44 au 40 late                              |  |  |

| Converter Resolution      |                                                                                                                                           | ble 10,12,14 or 16 bits                             |  |  |

| Converter Accuracy        | Up to 2 arcm                                                                                                                              |                                                     |  |  |

| Input Signal Conditioning |                                                                                                                                           | tioning Adapter TPMC150-A1 – TPMC150-A4             |  |  |

| Additional Output         | Velocity outp                                                                                                                             |                                                     |  |  |

|                           |                                                                                                                                           | encoder emulation, available as RS422/485 outputs   |  |  |

| Motion Feedback           | 32 bit up/dow<br>per channel                                                                                                              | vn encoder counter with preload and output register |  |  |

| Digital Input             | 1 digital 24V                                                                                                                             | input per channel                                   |  |  |

| I/O Interface             |                                                                                                                                           |                                                     |  |  |

| I/O Connector             | HD68 SCSI-3 type female connector (no PMC P14 I/O)                                                                                        |                                                     |  |  |

| Physical Data             |                                                                                                                                           |                                                     |  |  |

| Power Requirements        | TPMC150 Base Board Power Requirements:                                                                                                    |                                                     |  |  |

|                           | • •                                                                                                                                       | cal @ +3.3V DC                                      |  |  |

|                           | • •                                                                                                                                       | II @ +5.0V DC                                       |  |  |

|                           | • •                                                                                                                                       | al @ -12V DC                                        |  |  |

|                           | 8mA typical                                                                                                                               | ower Requirements for/per TPMC150-A2/A4 Adapter:    |  |  |

|                           | • •                                                                                                                                       | @ -5V DC (derived from -12V)                        |  |  |

|                           | 5mA typical                                                                                                                               | ·                                                   |  |  |

|                           | 5mA typical                                                                                                                               |                                                     |  |  |

| Temperature Range         | Operating                                                                                                                                 | -40°C to +85°C                                      |  |  |

|                           | Storage                                                                                                                                   | -55°C to +125°C                                     |  |  |

| MTBF                      |                                                                                                                                           | DR: 240 000 h                                       |  |  |

|                           | TPMC150-11                                                                                                                                | 1R: 286 000 h                                       |  |  |

|                           |                                                                                                                                           | 2R: 354 000 h                                       |  |  |

|                           | TPMC150-13R: 464 000 h                                                                                                                    |                                                     |  |  |

|                           | MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C.       |                                                     |  |  |

|                           | The MTBF calculation is based on component FIT rates provided by the                                                                      |                                                     |  |  |

|                           | component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                                                     |  |  |

| Humidity                  | 5 – 95 % nor                                                                                                                              | n-condensing                                        |  |  |

| Weight                    | 71 g                                                                                                                                      |                                                     |  |  |

|                           |                                                                                                                                           |                                                     |  |  |

Table 2-1: Technical Specification TPMC150

### 2.1 Tracking Rate Characteristics

Tracking Rate, bandwidth and velocity scaling is dependent on the resolution of the RDC.

rps = Revolutions per second

| Resolution              | 10                        | 12     | 14     | 16   |

|-------------------------|---------------------------|--------|--------|------|

| Tracking rate (rps)     | 1022                      | 255    | 64     | 16   |

| Bandwidth (Hz)          | 1024                      |        | 270    |      |

| Carrier frequency (kHz) | (kHz) 4 - 10 4 - 10 1 - 7 |        | 1 - 5  |      |

| Scale factor (V/rps)    | 0.0039                    | 0.0157 | 0.0625 | 0.25 |

Table 2-2: Tracking Rate Characteristics

## 2.2 Velocity Output Characteristics

| Parameter                  | Unit  | Typical                       | Min/Max |

|----------------------------|-------|-------------------------------|---------|

| Polarity                   |       | Positive for increasing angle |         |

| Voltage range (full scale) | V     | ±4                            |         |

| Scale factor error         | %     | 10                            | 20      |

| Scale factor TC            | PPM/C | 100                           | 200     |

| Reversal error             | %     | 0.75                          | 1.3     |

| Linearity                  | %     | 0.25                          | 1.0     |

| Zero Offset                | mV    | 5                             | 10      |

| Zero Offset TC             | μV/C  | 15                            | 30      |

| Load                       | kΩ    |                               | 8       |

Table 2-3: Velocity Output Characteristics

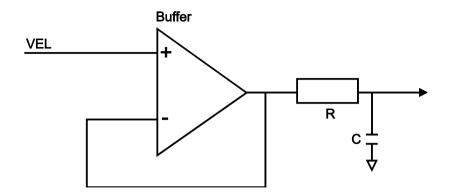

Applying loads on the velocity output may affect converter accuracy. To use the velocity output line to monitor speeds, a buffer must be added to the line.

The velocity output is a DC-signal with an AC-ripple. The main components of the ripple are the carrier frequency and double the carrier frequency. The ripple can be filtered behind the buffer. Set the RC to cut off below the carrier frequency.

Neither the buffer nor the velocity ripple filter is included on the TPMC150.

Figure 2-1: Velocity Ripple Filter

## 2.3 Digital Input Characteristics

The TPMC150 offers one digital 24V input per channel which is galvanically isolated by optocouplers. A high performance input circuit ensures a defined switching point and polarization protection against confusing the pole. The inputs are electronically debounced. Each of the four digital 24V inputs can generate an interrupt, triggered on rising or falling edge. Depending on the selected reference mode the input can be used as general purpose input or as reference input.

| Parameter       | Unit | Typical                           |

|-----------------|------|-----------------------------------|

| Input isolation |      | Optocoupler as galvanic isolation |

| Input voltage   | V    | 24                                |

| Input current   | mA   | 4.2                               |

|                 |      | (at 24V input voltage)            |

| Switching level | V    | 12                                |

|                 |      | (min. 7.5, max. 14)               |

Table 2-4: Digital Input Characteristics

Figure 2-2: Digital Input Wiring

# 3 TPMC150 Local Space Addressing

# 3.1 PCI9030 Local Space Configuration

The local on board addressable regions are accessed from the PCI side by using the PCI9030 local spaces.

| PCI9030<br>Local<br>Space | PCI9030 PCI Base Address (Offset in PCI Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description               |

|---------------------------|--------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|---------------------------|

| 0                         | 2 (0x18)                                                     | MEM                     | 128            | 32                     | BIG            | Register Address<br>Space |

| 1                         | 3 (0x1C)                                                     | -                       | -              | -                      | -              | Not Used                  |

| 2                         | 4 (0x20)                                                     | -                       | -              | -                      | -              | Not Used                  |

| 3                         | 5 (0x24)                                                     | -                       | ı              | -                      | -              | Not Used                  |

Table 3-1: PCI9030 Local Space Configuration

# 3.2 Register Address Space

PCI Base Address: PCI9030 PCI Base Address 2 (Offset 0x18 in PCI Configuration Space).

| Offset to PCI<br>Base Address 2 | Register Name                           | Size<br>(Bit) |

|---------------------------------|-----------------------------------------|---------------|

| 0x00                            | Global Control/Status Register          | 32            |

| 0x04                            | Interrupt Control/Status Register       | 32            |

| 0x08                            | Digital Input Register                  | 32            |

| 0x0C                            | Channel Control Register 1              | 32            |

| 0x10                            | Channel Control Register 2              | 32            |

| 0x14                            | Channel Control Register 3              | 32            |

| 0x18                            | Channel Control Register 4              | 32            |

| 0x1C                            | Channel Data Register 1                 | 32            |

| 0x20                            | Channel Data Register 2                 | 32            |

| 0x24                            | Channel Data Register 3                 | 32            |

| 0x28                            | Channel Data Register 4                 | 32            |

| 0x2C                            | Channel Status Register 1               | 32            |

| 0x30                            | Channel Status Register 2               | 32            |

| 0x34                            | Channel Status Register 3               | 32            |

| 0x38                            | Channel Status Register 4               | 32            |

| 0x3C                            | Encoder Counter Preload/Data Register 1 | 32            |

| 0x40                            | Encoder Counter Preload/Data Register 2 | 32            |

| 0x44                            | Encoder Counter Preload/Data Register 3 | 32            |

| 0x48                            | Encoder Counter Preload/Data Register 4 | 32            |

| 0x4C 0x80                       | Reserved                                | -             |

Table 3-2: Register Address Space

If in the following register descriptions the equivalent bits of all channels are combined into a bit field, the bit field refers to the channels in ascending order. For example the LSB of the bit field refers to Channel 1 and the MSB to Channel 4.

### 3.2.1 Global Control/Status Register

| Bit   | Symbol       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Access | Reset |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 17-31 |              | Reserved (Undefined for reads. Write as '0'.)                                                                                                                                                                                                                                                                                                                                                                                                                  | -      | Х     |

| 16    | CTRL_CON_STA | Multiple Converter Read Status  1: Multiple Converter Read in progress                                                                                                                                                                                                                                                                                                                                                                                         | R      | 0     |

| 12-15 | CTRL_CON_SEL | Multiple Converter Read Channel Select Writing a '1' to a bit select the corresponding channel for Multiple Converter Read.                                                                                                                                                                                                                                                                                                                                    | R/W    | 0000  |

| 11    | CTRL_CON_RD  | Multiple Converter Read 0: Disabled 1: Enabled See chapter 'Multiple Converter Read' for details.                                                                                                                                                                                                                                                                                                                                                              | R/W    | 0     |

| 10    | CTRL_ENC_STA | Multiple Encoder Read Status  1: Multiple Encoder Read in progress                                                                                                                                                                                                                                                                                                                                                                                             | R      | 0     |

| 6-9   | CTRL_ENC_SEL | Multiple Encoder Read Channel Select Writing a '1' to a bit select the corresponding channel for Multiple Encoder Read.                                                                                                                                                                                                                                                                                                                                        | R/W    | 0000  |

| 5     | CTRL_ENC_RD  | Multiple Encoder Read 0: Disabled 1: Enabled See chapter 'Multiple Encoder Read' for details.                                                                                                                                                                                                                                                                                                                                                                  | R/W    | 0     |

| 4     | CTRL_IRQ     | General IRQ Enable 0: globally disables interrupts 1: globally enables interrupts for the digital 24V inputs.                                                                                                                                                                                                                                                                                                                                                  | R/W    | 0     |

| 0-3   | CTRL_PRE     | Manual Encoder Counter Preload Writing a '1' issues a preload of the corresponding encoder counter with the value of the Encoder Counter Preload Register. This preload method is only possible in the 'None Reference Mode'. After the preload access is executed, these bits are cleared automatically and signal a successful preload. Before using this preload method, the corresponding Encoder Counter Preload Register must be loaded with valid data. | R/W    | 0000  |

Table 3-3: Global Control/Status Register

The digital 24V inputs generate interrupts at pin INTA# of the PMC bus. Additional to this Global Interrupt Enable the Interrupt INTA# must be enabled in the Interrupt Control Register (INTCSR; 0x4C) of the PCI Controller PCI9030. Default after power on and reset: INTA# is enabled.

### 3.2.2 Interrupt Control/Status Register

| Bit   | Symbol   | Description                                                                                                                                                                                                                   | Access | Reset |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 12-31 |          | Reserved (Undefined for reads. Write as '0'.)                                                                                                                                                                                 | -      | Χ     |

| 8-11  | IRQ_CTRL | Digital Input Interrupt Control 0: interrupt on falling edge 1: interrupt on rising edge                                                                                                                                      | R/W    | 0000  |

| 4-7   | IRQ_STA  | Digital Input Interrupt Status  0: no interrupt request is pending  1: an interrupt request is pending  A pending interrupt request for a specific digital 24V input is cleared by writing a '1' to the according status bit. | R/W    | 0000  |

| 0-3   | IRQ_EN   | Digital Input Interrupt Enable  To enable the interrupt for a digital input, set the corresponding bit to '1'.                                                                                                                | R/W    | 0000  |

Table 3-4: Interrupt Control/Status Register

The following table shows a short overview about enabling interrupts and the active trigger edge.

| Digital 24V input |

|-------------------|

| DIN1              |

| DIN2              |

| DIN3              |

| DIN4              |

| Bit | Interrupt |        |  |  |  |

|-----|-----------|--------|--|--|--|

|     | disable   | enable |  |  |  |

| 0   | '0'       | '1'    |  |  |  |

| 1   | '0'       | '1'    |  |  |  |

| 2   | '0'       | '1'    |  |  |  |

| 3   | '0'       | '1'    |  |  |  |

| Bit | Active edge |        |  |  |  |

|-----|-------------|--------|--|--|--|

|     | falling     | rising |  |  |  |

| 8   | '0'         | '1'    |  |  |  |

| 9   | '0'         | '1'    |  |  |  |

| 10  | '0'         | '1'    |  |  |  |

| 11  | '0'         | '1'    |  |  |  |

Table 3-5: Input Interrupt configuration

### 3.2.3 Digital Input Register

| Bit  | Symbol | Description                                                                                                                                                            | Access | Reset |

|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 4-31 |        | Reserved (Undefined for reads. Write as '0'.)                                                                                                                          | -      | Х     |

| 0-3  | DIN    | Digital Input State Reflects the actual state of the digital 24V inputs. This register is always active and reflects the state of the digital 24V inputs at all times. | R      | 0000  |

Table 3-6: Digital Input Register

In the 'None Reference Mode' and 'Index Mode' the digital 24V inputs can be used as general purpose inputs.

In the 'Reference Mode' and 'Auto Reference Mode' the digital 24V inputs are used as reference inputs.

### 3.2.4 Channel Control Register

| Bit   | Symbol     |                                        | Description                                                                                                                                                                                                                                                         |           |                                    |   |     | Reset |

|-------|------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------|---|-----|-------|

| 10-31 |            | Reserve                                | Reserved (Undefined for reads. Write as '0'.)                                                                                                                                                                                                                       |           |                                    |   |     | Х     |

| 9     | CH_EMU_OUT | 0: Disat<br>1: Outp<br>enab            | <ul><li>Incremental Encoder Emulation Output</li><li>0: Disabled</li><li>1: Output of the Encoder Emulation via the RS485/422 drivers enabled</li></ul>                                                                                                             |           |                                    |   | R/W | 0     |

|       |            | See cha<br>details.                    | ıpter 'I                                                                                                                                                                                                                                                            | ncreme    | ntal Encoder Emulation Output' fo  | ſ |     |       |

| 8     | CH_EMU_EN  | 0: Disab<br>1: Enab<br>Emul<br>is late | Incremental Encoder Emulation 0: Disabled 1: Enabled; this bit activates the Incremental Encoder Emulation. When set to '1', the current converter resolution is latched und used for the Incremental Encoder Emulation. This bit also enables the Encoder Counter. |           |                                    |   | R/W | 0     |

| 6-7   | CH_REF     | Encoder                                | r Refe                                                                                                                                                                                                                                                              | rence M   | lode                               |   | R/W | 00    |

|       |            |                                        | Value                                                                                                                                                                                                                                                               | )         | Reference Mode                     |   |     |       |

|       |            |                                        | 0                                                                                                                                                                                                                                                                   | 0         | None Reference Mode                |   |     |       |

|       |            |                                        | 0                                                                                                                                                                                                                                                                   | 1         | Reference Mode                     |   |     |       |

|       |            |                                        | 1                                                                                                                                                                                                                                                                   | 0         | Auto Reference Mode                |   |     |       |

|       |            |                                        | 1                                                                                                                                                                                                                                                                   | 1         | Index Mode                         |   |     |       |

|       |            | See cha                                | ıpter 'F                                                                                                                                                                                                                                                            | Reference | ce Mode' for details.              |   |     |       |

| 4-5   | CH_ESAM    | Encoder                                | r Signa                                                                                                                                                                                                                                                             | al Analy  | sis Mode                           |   | R/W | 00    |

|       |            |                                        | Value Analysis Mode                                                                                                                                                                                                                                                 |           |                                    |   |     |       |

|       |            |                                        | 0 0 disable Counter                                                                                                                                                                                                                                                 |           |                                    |   |     |       |

|       |            |                                        | 0 1 1x – single                                                                                                                                                                                                                                                     |           |                                    |   |     |       |

|       |            |                                        | 1                                                                                                                                                                                                                                                                   | 0         | 2x – double                        |   |     |       |

|       |            |                                        | 1                                                                                                                                                                                                                                                                   | 1         | 4x – quad                          |   |     |       |

|       |            | See cha                                | pter 'E                                                                                                                                                                                                                                                             | Encoder   | Signal Analysis Mode' for details. |   |     |       |

| Bit | Symbol     |                                   |        | Des       | cription         |                  | Access | Reset |

|-----|------------|-----------------------------------|--------|-----------|------------------|------------------|--------|-------|

| 3   | CH_SYN_CON | Synchronous Co                    | nvers  | sion      |                  |                  | R/W    | 0     |

|     |            | 0: Disabled                       |        |           |                  |                  |        |       |

|     |            | 1: Enabled (only                  | Char   | nnel 1 &  | . 3)             |                  |        |       |

|     |            | For channel 2 ar read access retu |        |           | CH_SYN_CON       | is ignored and a |        |       |

|     |            | See chapter 'Op details.          | eratin | ng with S | Synchronous Cor  | nversion' for    |        |       |

| 2   | CH_SYN_LAT | Synchronous Sta                   | atus L | _atch     |                  |                  | R/W    | 0     |

|     |            | 0: Disabled                       |        |           |                  |                  |        |       |

|     |            | 1: Enabled                        |        |           |                  |                  |        |       |

|     |            | See chapter 'Op details.          | eratin | ng with S | Synchronous Sta  | itus Latch' for  |        |       |

| 0-1 | CH_RES     | Converter Resol                   | ution  |           |                  |                  | R/W    | 00    |

|     |            | Sets the convert                  | er res | solution. | Available values | s are:           |        |       |

|     |            |                                   | Valu   | ue        | Resolution       | ]                |        |       |

|     |            |                                   | 0      | 0         | 10 bit           |                  |        |       |

|     |            |                                   | 0      | 1         | 12 bit           |                  |        |       |

|     |            |                                   | 1      | 0         | 14 bit           |                  |        |       |

|     |            |                                   | 1      | 1         | 16 bit           |                  |        |       |

| 1   |            |                                   |        |           | •                | -                |        |       |

Table 3-7: Channel Control Register

The converter resolution can be changed after the Incremental Encoder Emulation resolution is set, but it must not be less than the resolution of the Incremental Encoder Emulation. If the converter resolution is less than the Incremental Encoder Emulation resolution, there will be no Encoder Emulation output!

### 3.2.5 Channel Data Register

The Channel Data Register contains the 16 bit wide converted data value of the synchro or resolver. When the resolution is set to less than 16 bits, all unused bits are read as '0'. The conversion result is always MSB aligned (i.e. aligned to bit 15). The resolution is controlled by the Channel Control Register.

| Bit   | Symbol  | Description             | Access | Reset |

|-------|---------|-------------------------|--------|-------|

| 16-31 |         | Reserved (Reads as '0') | -      | Х     |

| 0-15  | CH_DATA | Converter Data          | R      | 0     |

Table 3-8: Channel Data Register

The position of the LSB depends on the resolution:

| Resolution | D31-16 | D15 | D147 | D6  | D5 | D4  | D3 | D2  | D1 | D0  |

|------------|--------|-----|------|-----|----|-----|----|-----|----|-----|

| 10         | 0      | MSB | Х    | LSB | 0  | 0   | 0  | 0   | 0  | 0   |

| 12         | 0      | MSB | Х    | Х   | Х  | LSB | 0  | 0   | 0  | 0   |

| 14         | 0      | MSB | Х    | Х   | Х  | Х   | Х  | LSB | 0  | 0   |

| 16         | 0      | MSB | Х    | X   | Х  | Х   | Х  | Х   | X  | LSB |

Table 3-9: LSB Position

### 3.2.6 Channel Status Register

| Bit  | Symbol     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Access | Reset |

|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|

| 3-31 |            | Reserved (Undefined for reads. Write as '0'.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -      | Х     |

| 2    | CH_STA_DIR | Direction of Motion 0: down (clockwise, angle decreasing) 1: up (counter clockwise, angle increasing)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        | 0     |

|      |            | On a static signal, CH_STA_DIR indicates the last direction of motion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |       |

| 1    | CH_STA_AM  | Adapter mounting 0: Adapter mounted 1: No adapter mounted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R      | 0     |

| 0    | CH_STA_BIT | Converter Build-in-Self-Test Built-In-Test (BIT) = '1' indicates an error. The causes for an error are as follows:  1. Loss of Signal (LOS). Both input signals (+S/-S and +C/-C) drop below the threshold voltage of 500mV.  2. Phase Error. The input signal phase is more than 180° different from the reference signal phase.  3. Excessive Error. The digital output is more than a 180 LSBs different from the input angle.  4. Loss of Reference (LOR). The reference input signal is less than 500mV.  On normal operation, a BIT occurs during large step changes of the input or on high accelerations that cause acceleration lag. | R      | 0     |

Table 3-10: Channel Status Register

The direction indication is reliable only when the Encoder Emulation is active. If the Encoder Emulation is not active, this bit reflects the 'U'-output of the RD-19231, which is not reliable on static angles.

If CH\_STA\_BIT is read as '1' the resolution could be changed from its programmed value one step down to a lower resolution. This would allow the converter to settle out faster (see chapter 'Changing Resolution on the Fly').

### 3.2.7 Encoder Counter Preload/Data Register

A write access updates the Encoder Counter Preload Register. A read access reads the Encoder Counter Data Register.

| Bit  | Symbol   | Description                                                                                                       | Access | Reset |

|------|----------|-------------------------------------------------------------------------------------------------------------------|--------|-------|

| 0-31 | ENC_PRE  | Encoder Counter Preload Register                                                                                  | W      | 0     |

|      |          | The Encoder Counter Preload Register is used in all modes for reference preload.                                  |        |       |

| 0-31 | ENC_DATA | Encoder Counter Data Register The actual encoder counter value is latched into the Encoder Counter Data Register. | R      | 0     |

Table 3-11: Encoder Counter Preload/Data Register

If the Multiple Encoder Read feature is used for the Encoder Counter Data Registers, a read access latches all counter values for the enabled counters at the same time. Then the Encoder Counter Data Registers can be read one after the other. A new Multiple Encoder Read access is only possible after finishing the read of all latched Encoder Counter Data Registers.

# 4 PCI9030 Target Chip

# 4.1 PCI Configuration Registers (PCR)

### 4.1.1 PCI9030 Header

| PCI CFG<br>Register | Write '0' to all u                   | nused (Reserved     | ) bits               |                    | PCI<br>writeable | Initial Values<br>(Hex Values) |

|---------------------|--------------------------------------|---------------------|----------------------|--------------------|------------------|--------------------------------|

| Address             | 31 24                                | 23 16               | 15 8                 | 7 0                |                  |                                |

| 0x00                | Devi                                 | ce ID               | Vend                 | dor ID             | N                | 0096 1498                      |

| 0x04                | Sta                                  | itus                | Com                  | mand               | Υ                | 0280 0000                      |

| 0x08                |                                      | Class Code          |                      | Revision ID        | N                | 118000 0A                      |

| 0x0C                | BIST                                 | Header Type         | PCI Latency<br>Timer | Cache Line<br>Size | Y[7:0]           | 00 00 00 00                    |

| 0x10                | PCI Base                             | Address 0 for ME    | M Mapped Config.     | Registers          | Υ                | FFFFF80                        |

| 0x14                | PCI Base                             | e Address 1 for I/C | Mapped Config.       | Registers          | Υ                | FFFFFF81                       |

| 0x18                | PCI E                                | Base Address 2 for  | Local Address Sp     | pace 0             | Υ                | FFFFFF80                       |

| 0x1C                | PCI E                                | sase Address 3 for  | Local Address Sp     | ace 1              | Υ                | 00000000                       |

| 0x20                | PCI E                                | Base Address 4 for  | Local Address Sp     | ace 2              | Υ                | 00000000                       |

| 0x24                | PCI E                                | sase Address 5 for  | Local Address Sp     | ace 3              | Υ                | 00000000                       |

| 0x28                | PC                                   | I CardBus Informa   | ation Structure Poi  | nter               | N                | 00000000                       |

| 0x2C                | Subsys                               | stem ID             | Subsystem            | Nendor ID          | N                | s.b. 1498                      |

| 0x30                | PCI                                  | Base Address for    | Local Expansion I    | ROM                | Υ                | 00000000                       |

| 0x34                |                                      | Reserved            |                      | New Cap. Ptr.      | N                | 000000 40                      |

| 0x38                |                                      | Rese                | erved                |                    | N                | 00000000                       |

| 0x3C                | Max_Lat                              | Min_Gnt             | Interrupt Pin        | Interrupt Line     | Y[7:0]           | 00 00 01 00                    |

| 0x40                | PM Cap. PM Nxt Cap. PM Cap. ID       |                     |                      |                    |                  | 4801 00 01                     |

| 0x44                | PM Data                              | PM CSR EXT          | PM                   | PM CSR             |                  | 00 00 0000                     |

| 0x48                | Reserved                             | HS CSR              | HS Nxt Cap.          | HS Cap. ID         | Y[23:16]         | 00 00 00 00                    |

| 0x4C                | VPD Address VPD Nxt Cap. VPD Cap. ID |                     |                      |                    |                  | 0000 00 03                     |

| 0x50                |                                      | VPD                 | Data                 |                    | Υ                | 00000000                       |

Table 4-1: PCI9030 Header

Subsystem-ID Value (Offset 0x0C): TPMC150-10R 0x000A

TPMC150-11R 0x000B

TPMC150-12R 0x000C

TPMC150-13R 0x000D

### 4.1.2 PCI Base Address Initialization

PCI Base Address Initialization is scope of the PCI host software.

#### PCI9030 PCI Base Address Initialization:

- 1. Write 0xFFFF FFFF to the PCI9030 PCI Base Address Register.

- 2. Read back the PCI9030 PCI Base Address Register.

- 3. For PCI Base Address Registers 0:5, check bit 0 for PCI Address Space.

- Bit 0 = '0' requires PCI Memory Space mapping

- Bit 0 = '1' requires PCI I/O Space mapping

For the PCI Expansion ROM Base Address Register, check bit 0 for usage.

- Bit 0 = '0': Expansion ROM not used

- Bit 0 = '1': Expansion ROM used

- 4. For PCI I/O Space mapping, starting at bit location 2, the first bit set determines the size of the required PCI I/O Space size.

For PCI Memory Space mapping, starting at bit location 4, the first bit set to '1' determines the size of the required PCI Memory Space size.

For PCI Expansion ROM mapping, starting at bit location 11, the first bit set to '1' determines the required PCI Expansion ROM size.

For example, if bit 5 of a PCI Base Address Register is detected as the first bit set to '1', the PCI9030 is requesting a 32 byte space (address bits 4:0 are not part of base address decoding).

5. Determine the base address and write the base address to the PCI9030 PCI Base Address Register. For PCI Memory Space mapping the mapped address region must comply with the definition of bits 3:1 of the PCI9030 PCI Base Address Register.

After programming the PCI9030 PCI Base Address Registers, the software must enable the PCI9030 for PCI I/O and/or PCI Memory Space access in the PCI9030 PCI Command Register (Offset 0x04). To enable PCI I/O Space access to the PCI9030, set bit 0 to '1'. To enable PCI Memory Space access to the PCI9030, set bit 1 to '1'.

| Offset in Config. | Description           | Usage    |

|-------------------|-----------------------|----------|

| 0x10              | PCI9030 LCR's MEM     | Used     |

| 0x14              | PCI9030 LCR's I/O     | Used     |

| 0x18              | PCI9030 Local Space 0 | Used     |

| 0x1C              | PCI9030 Local Space 1 | Not used |

| 0x30              | Expansion ROM         | Not used |

Table 4-2: PCI9030 PCI Base Address Usage

## 4.2 Local Configuration Register (LCR)

After reset, the PCI9030 Local Configuration Registers are loaded from the on board serial configuration EEPROM.

The PCI base address for the PCI9030 Local Configuration Registers is PCI9030 PCI Base Address 0 (PCI Memory Space) (Offset 0x10 in the PCI9030 PCI Configuration Register Space) or PCI9030 PCI Base Address 1 (PCI I/O Space) (Offset 0x14 in the PCI9030 PCI Configuration Register Space).

Do not change hardware dependent bit settings in the PCI9030 Local Configuration Registers.

| Offset from<br>PCI Base<br>Address | Register                             | Value       | Description               |

|------------------------------------|--------------------------------------|-------------|---------------------------|

| 0x00                               | Local Address Space 0 Range          | 0x0FFF FF80 | Memory space              |

| 0x04                               | Local Address Space 1 Range          | 0x0000 0000 | Not used                  |

| 80x0                               | Local Address Space 2 Range          | 0x0000 0000 | Not used                  |

| 0x0C                               | Local Address Space 3 Range          | 0x0000 0000 | Not used                  |

| 0x10                               | Local Exp. ROM Range                 | 0x0000 0000 | Not used                  |

| 0x14                               | Local Re-map Register Space 0        | 0x0000 0001 | Enabled, Offset 0         |

| 0x18                               | Local Re-map Register Space 1        | 0x0000 0000 | Not used                  |

| 0x1C                               | Local Re-map Register Space 2        | 0x0000 0000 | Not used                  |

| 0x20                               | Local Re-map Register Space 3        | 0x0000 0000 | Not used                  |

| 0x24                               | Local Re-map Register ROM            | 0x0000 0000 | Not used                  |

| 0x28                               | Local Address Space 0 Descriptor     | 0x01B1 7B60 | Local timing              |

| 0x2C                               | Local Address Space 1 Descriptor     | 0x0000 0000 | Not used                  |

| 0x30                               | Local Address Space 2 Descriptor     | 0x0000 0000 | Not used                  |

| 0x34                               | Local Address Space 3 Descriptor     | 0x0000 0000 | Not used                  |

| 0x38                               | Local Exp. ROM Descriptor            | 0x0000 0000 | Not used                  |

| 0x3C                               | Chip Select 0 Base Address           | 0x0000 0041 | Chip select               |

| 0x40                               | Chip Select 1 Base Address           | 0x0000 0000 | Not used                  |

| 0x44                               | Chip Select 2 Base Address           | 0x0000 0000 | Not used                  |

| 0x48                               | Chip Select 3 Base Address           | 0x0000 0000 | Not used                  |

| 0x4C                               | Interrupt Control/Status             | 0x0043      | Interrupt configuration   |

| 0x4E                               | EEPROM Write Protect Boundary        | 0x0030      | Standard write protection |

| 0x50                               | Miscellaneous Control Register       | 0x0078 0000 | Retry delay = max         |

| 0x54                               | General Purpose I/O Control          | 0x0000 0000 | All pins are outputs      |

| 0x70                               | Hidden1 Power Management data select | 0x0000 0000 | Not used                  |

| 0x74                               | Hidden 2 Power Management data scale | 0x0000 0000 | Not used                  |

Table 4-3: PCI9030 Local Configuration Register

# **4.3 Configuration EEPROM**

After power-on or PCI reset, the PCI9030 loads initial configuration register data from the on board configuration EEPROM.

The configuration EEPROM contains the following configuration data:

- Address 0x00 to 0x27 : PCI9030 PCI Configuration Register Values

- Address 0x28 to 0x87 : PCI9030 Local Configuration Register Values

- Address 0x88 to 0xFF: Reserved

See the PCI9030 Manual for more information.

| Address | Offset |        |        |        |        |        |        |        |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | 0x00   | 0x02   | 0x04   | 0x06   | 80x0   | 0x0A   | 0x0C   | 0x0E   |

| 0x00    | 0x0096 | 0x1498 | 0x0280 | 0x0000 | 0x1180 | 0x000A | s.b.   | 0x1498 |

| 0x10    | 0x0000 | 0x0040 | 0x0000 | 0x0100 | 0x4801 | 0x0001 | 0x0000 | 0x0000 |

| 0x20    | 0x0000 | 0x0000 | 0x0000 | 0x0003 | 0x0FFF | 0xFF80 | 0x0000 | 0x0000 |

| 0x30    | 0x0000 | 0x0001 |

| 0x40    | 0x0000 |

| 0x50    | 0x01B1 | 0x7B60 | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0x0000 |

| 0x60    | 0x0000 | 0x0000 | 0x0000 | 0x0041 | 0x0000 | 0x0000 | 0x0000 | 0x0000 |

| 0x70    | 0x0000 | 0x0000 | 0x0030 | 0x0043 | 0x0078 | 0x0000 | 0x0000 | 0x0000 |

| 0x80    | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0xFFFF | 0xFFFF | 0xFFFF | 0xFFFF |

| 0x90    | 0xFFFF |

| 0xA0    | 0xFFFF |

| 0xB0    | 0xFFFF |

| 0xC0    | 0xFFFF |

| 0xD0    | 0xFFFF |

| 0xE0    | 0xFFFF |

| 0xF0    | 0xFFFF |

Table 4-4: Configuration EEPROM TPMC150-xx

Subsystem-ID Value (Offset 0x0C): TPMC150-10R 0x000A

TPMC150-11R 0x000B

TPMC150-12R 0x000C

TPMC150-13R 0x000D

### 4.4 Local Software Reset

The PCI9030 Local Reset Output LRESETo# is used to reset the on board local logic.

The PCI9030 local reset is active during PCI reset or if the PCI Adapter Software Reset bit is set in the PCI9030 local configuration register CNTRL (offset 0x50).

#### CNTRL[30] PCI Adapter Software Reset:

Value of 1 resets the PCI9030 and issues a reset to the Local Bus (LRESETo# asserted). The PCI9030 remains in this reset condition until the PCI Host clears this bit. The contents of the PCI9030 PCI and Local Configuration Registers are not reset. The PCI9030 PCI Interface is not reset.

# **5 Configuration Hints**

## 5.1 Software Reset (Controller and LRESET#)

A host on the PCI bus can set the software reset bit in the Miscellaneous Control Register (CNTRL; 0x50) of the PCI Controller PCI9030 to reset the Controller and assert LRESET# output. The PCI9030 remains in this reset condition until the PCI host clears the software reset bit.

## 5.2 Big / Little Endian

• PCI - Bus (Little Endian)

| Byte 0 | AD[70]   |

|--------|----------|

| Byte 1 | AD[158]  |

| Byte 2 | AD[2316] |

| Byte 3 | AD[3124] |

• Every Local Address Space (0...3) and the Expansion ROM Space can programmed to operate in Big or Little Endian Mode.

| Big Endi          | an               | Little Endian |         |  |  |

|-------------------|------------------|---------------|---------|--|--|

| 32 Bit            |                  | 32 Bit        |         |  |  |

| Byte 0            | D[3124]          | Byte 0        | D[70]   |  |  |

| Byte 1            | D[2316]          | Byte 1        | D[158]  |  |  |

| Byte 2            | D[158]           | Byte 2        | D[2316] |  |  |

| Byte 3            | D[70]            | Byte 3        | D[3124] |  |  |

| 16 Bit upper lane |                  | 16 Bit        | 16 Bit  |  |  |

| Byte 0            | D[3124]          | Byte 0        | D[70]   |  |  |

| Byte 1            | D[2316]          | Byte 1        | D[158]  |  |  |

| 16 Bit lo         | wer lane         |               |         |  |  |

| Byte 0            | D[158]           |               |         |  |  |

| Byte 1            | D[70]            |               |         |  |  |

| 8 Bit upp         | 8 Bit upper lane |               |         |  |  |

| Byte 0            | D[3124]          | Byte 0        | D[70]   |  |  |

| 8 Bit low         | 8 Bit lower lane |               |         |  |  |

| Byte 0            | D[70]            |               |         |  |  |

Table 5-1: Local Bus Little/Big Endian

#### Standard use of the TPMC150:

| Local Address Space 0 | 32 bit bus in Big Endian Mode |

|-----------------------|-------------------------------|

|                       |                               |

Local Address Space 1 not used

Local Address Space 2 not used

Local Address Space 3 not used

Expansion ROM Space not used

To change the Endian Mode use the Local Configuration Registers for the corresponding Space. Bit 24 of the according register sets the Mode. A value of 1 indicates Big Endian and a value of 0 indicates Little Endian.

Use the PCI Base Address 0 + Offset or PCI Base Address 1 + Offset:

| Short cut Offset | Name |                                                       |

|------------------|------|-------------------------------------------------------|

| LAS0BRD          | 0x28 | Local Address Space 0 Bus Region Description Register |

| LAS1BRD          | 0x2C | Local Address Space 0 Bus Region Description Register |

| LAS2BRD          | 0x30 | Local Address Space 0 Bus Region Description Register |

| LAS3BRD          | 0x34 | Local Address Space 0 Bus Region Description Register |

| EROMBRD          | 0x38 | Expansion ROM Bus Region Description Register         |

You could also use the PCI - Base Address 1 I/O Mapped Configuration Registers.

### 5.3 Local read/write

The local register design is developed for a long word (32 bit) read/write access. A byte or word access could fail.

## 5.4 Changing Resolution on the Fly

A technique used to increase the tracking rate while maintaining low speed accuracy is to switch the resolution of the converter on the fly (sometimes called gear shifting). This allows the user to increase resolution when the input is changing at slow speeds, or decrease the resolution when high tracking rates are required. This change is accomplished by simply changing the digital resolution controls.

However, the change in resolution will introduce a transient in the output code as well as the velocity. This is due to internal gain changes when the resolution is switched.

This technique can also be used to reduce errors from large input steps or over velocity conditions. When the Build-In-Test of the converter indicates an error, the resolution can be changed from its programmed value one step down to a lower resolution. This allows the converter to settle out faster.

### 5.5 Operating Modes

### 5.5.1 Converter Operating Modes

### 5.5.1.1 Operating with Synchronous Status Latch

Operating with Synchronous Status Latch is separately selected for each channel if CH\_SYN\_LAT of the respective Channel Control Register is set to '1'. In this case, the Channel Status Register latches the status at Channel Data Register read time. The latch is released by a read access to the Channel Status Register. Subsequent reads to the Channel Data Register without reading the Channel Status Register will leave the Status Register unchanged, i.e. the latched Status Register will not be updated.

#### Sequence:

read Data → freeze the status at data read

read Status → release status latch

check Build-In-Test → If CH STA BIT is read as '0', the data value is valid

### 5.5.1.2 Operating with Synchronous Conversion

Operating with Synchronous Conversion for Channel 1 and Channel 2 is selected if CH SYN CON of the Channel 1 Control Register is set to '1'. Operating with Synchronous Conversion for Channel 3 and Channel 4 is selected if CH SYN CON of the Channel 3 Control Register is set to'1'. In this case the value of channel 2 (channel 4) is converted simultaneously with channel 1 (channel 3). Status Registers are latched at Channel 1 (Channel 3) Data Register read time if the Synchronous Status Latch is enabled.

Sequence (example for channel 1 & 2):

read channel 1 data → start conversion for channel 1 and 2

→ latch the status for channel 1 and 2 (if Synchronous

Status Latch enabled)

read channel 1 status → release latch of Channel 1 Status Register (if enabled)

read channel 2 data → release Channel 2 Data Register

read channel 2 status → release latch of Channel 2 Status Register (if enabled)

of both status registers

→ If CH STA BIT is read as '0', the data value is valid. Check Build-In-Test

This feature may be useful, when two-speed-resolvers (coarse and fine) are used. Refer to the RD-19231 manual available on www.ddc-web.com for a software example.

### 5.5.1.3 Multiple Converter Read