## The Embedded I/O Company

# **TPMC160**

## **Automotive Sensor Simulator**

Version 1.1

#### **User Manual**

Issue 1.1.0 September 2025

#### **TPMC160-10R**

Automotive Sensor Simulator (RoHS compliant)

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However, TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### ©2025 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                                                                                                                                                                                          | Date           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 0.9.0 | Preliminary issue                                                                                                                                                                                                                                                    | June 2021      |

| 1.0.0 | Initial issue                                                                                                                                                                                                                                                        | August 2021    |

| 1.0.1 | - The PSI5 Microcut Rejection Time detection and the associated interrupts have been removed. The detection was not deterministic.                                                                                                                                   | October 2021   |

|       | - The description for the PSI5 SYNC Data Registers has been extended.                                                                                                                                                                                                |                |

|       | - The Protocol Setup Examples were revised.                                                                                                                                                                                                                          |                |

| 1.0.2 | <ul> <li>Description of the Board health register has been improved</li> <li>The description of the interrupt status registers was added</li> <li>Corrected I/O Connector description</li> </ul>                                                                     | July 2022      |

| 1.0.3 | <ul> <li>Clarified the "Cycle Register" behavior when it gets new values.</li> <li>Description of the PWM Protocol Register has been enhanced.</li> </ul>                                                                                                            | July 2024      |

| 1.0.4 | Added "7.1.4 Typical Test and Application Circuit"                                                                                                                                                                                                                   | August 2024    |

| 1.1.0 | - Corrected ADC Data Register Reserved Bits Index - Added the new "Extended Cycle" and "Extended TP" functionality to the "5.3.1 Register Map" - Added the register descriptions of the "5.3.10 Extended Timer Registers" - Updated Firmware Identification Register | September 2025 |

## **Table of Contents**

| 1 | PRO   | DUCT         | DESCRIPTION                                                                     | 8        |

|---|-------|--------------|---------------------------------------------------------------------------------|----------|

| 2 | TECH  | HNICA        | L SPECIFICATION                                                                 | 9        |

| 3 | HANI  | DLING        | AND OPERATION INSTRUCTIONS                                                      | 10       |

|   | 3.1   | ESD Pr       | otection                                                                        | 10       |

|   |       |              | Dissipation                                                                     |          |

|   |       |              | d for Isolated I/O                                                              |          |

| 4 |       |              | D DEFINITIONS                                                                   |          |

| 4 |       |              |                                                                                 |          |

|   |       |              | er Bit Access Types                                                             |          |

|   |       | -            | onventions                                                                      |          |

| 5 |       |              | FACE                                                                            |          |

|   |       |              | ers                                                                             |          |

|   | 5.2   | PCI Ba       | se Address Register Configuration                                               | 12       |

|   | 5.3   | Registe      | er Space                                                                        | 12       |

|   | 5.3.1 | l Re         | egister Map                                                                     | 12       |

|   | 5.3.2 | 2 Cc         | ommon Protocol Registers                                                        |          |

|   |       | .2.1         | Channel Control Register: 0x000                                                 |          |

|   |       | .2.2         | Current Level Registers 0x004 – 0x020                                           |          |

|   |       | .2.3         | ADC Data Register Ch0-1 0x024                                                   |          |

|   |       | .2.4         | ADC Data Register Ch2-3 0x028                                                   |          |

|   |       | .2.5         | ADC Data Register Ch4-5 0x02C                                                   |          |

|   |       | .2.6         | ADC Data Register Ch6-7 0x030                                                   |          |

|   | 5.3.3 |              | ustom Protocol Registers 0v050                                                  |          |

|   | 5.3.  | .3.1         | CP Cycle Registers 0x050 – 0x06C                                                |          |

|   |       | .3.2         | CP FIFO Status Register 0x070                                                   |          |

|   | 5.3.4 |              | uare Wave Protocol Registers                                                    |          |

|   |       | .4.1         | SWP Cycle Registers 0x0B0 – 0x0CC                                               | 22       |

|   | 5.3.5 |              | VM Protocol Registers                                                           |          |

|   |       | .5.1         | PWM Cycle Registers 0x120 – 0x13C                                               |          |

|   | 5.3.6 |              | G-Protocol / VDA Registers                                                      |          |

|   |       | .6.1         | AK Cycle Registers 0x160 – 0x17C                                                |          |

|   | 5.3.  | .6.2         | AK Control Registers 0x180 – 0x19C                                              |          |

|   | 5.3.7 | 7 PS         | SI5 Protocol Registers                                                          |          |

|   | 5.3.  | .7.1         | PSI5 Cycle Registers 0x220 – 0x23C                                              |          |

|   | 5.3.  | .7.2         | PSI5 Interrupt Status Registers 0x240                                           |          |

|   |       | .7.3         | PSI5 Status Registers 0x244 – 0x260                                             |          |

|   |       | .7.4         | PSI5 Detection Registers 0x264 – 0x280                                          |          |

|   |       | .7.5         | PSI5 Control Registers 0x284 – 0x2A0                                            |          |

|   |       | .7.6         | PSI5 Default Data Frame Registers 0x2E4 – 0x300                                 |          |

|   |       | .7.7<br>.7.8 | PSI5 Data Frame FIFO Registers 0x304 – 0x320<br>PSI5 FIFO Status Register 0x324 |          |

|   |       | .7.0<br>.7.9 | PSI5 SYNC Data Registers 0x330 – 0x34C                                          | ১/<br>২০ |

|   | 5.3.8 |              | /cle Counter Registers                                                          |          |

|   |       | .8.1         | Cycle Counter Control Register 0x370                                            | 39       |

|   |       | .8.2         | Cycle Counter Match Registers 0x374 – 0x380                                     |          |

|   |       | .3.8.2.1     | ·                                                                               |          |

|   |       | .3.8.2.2     |                                                                                 |          |

|   |       | .3.8.2.3     | · · · · · · · · · · · · · · · · · · ·                                           |          |

|   | 5.    | .3.8.2.4     | Cycle Counter Match Register Ch6-7 0x380                                        | 42       |

|   | 5.3.  | .8.3         | Cycle Counter Value Registers 0x384 – 0x390                                     | 43       |

|   |       |              |                                                                                 |          |

|   | 5.3.8.3.1 Cycle Counter Value Register Ch0-1 0x384    | 43 |

|---|-------------------------------------------------------|----|

|   | 5.3.8.3.2 Cycle Counter Value Register Ch2-3 0x388    |    |

|   | 5.3.8.3.3 Cycle Counter Value Register Ch4-5 0x38C    | 43 |

|   | 5.3.8.3.4 Cycle Counter Value Register Ch6-7 0x390    | 43 |

|   | 5.3.9 Interrupt Registers                             | 44 |

|   | 5.3.9.1 Interrupt Enable Register 0x420               | 44 |

|   | 5.3.9.2 PSI5 IRQ Trigger Enable Register 0x424        | 45 |

|   | 5.3.9.3 Interrupt Status Register 0x428               |    |

|   | 5.3.10 Extended Timer Registers                       |    |

|   | 5.3.10.1 Extended Cycle Registers 0x500 – 0x51C       |    |

|   | 5.3.10.2 Extended TP Registers 0x520 – 0x53C          |    |

|   | 5.3.11 Board Status                                   |    |

|   | 5.3.11.1 Board Health Register 0xFF4                  |    |

|   | 5.3.11.2 Scratchpad Register 0xFF8                    |    |

|   | 5.3.11.3 Firmware Identification Register 0xFFC       | 49 |

| 6 | PROTOCOL SETUP EXAMPLES                               | 50 |

|   | 6.1 Custom Protocol: Software procedure example       | 50 |

|   | 6.1.1 Direct control by software                      | 50 |

|   | 6.1.2 Custom Protocol in FIFO mode - Sequencer        |    |

|   | 6.1.3 Custom Protocol in FIFO mode - manual triggered |    |

|   | 6.2 Square Wave Protocol: Software procedure example  |    |

|   | 6.3 PWM Protocol: Software procedure example          |    |

|   | 6.4 AK Protocol: Software procedure example           |    |

|   | 6.5 PSI5 Protocol: Software procedure example         |    |

|   | 6.5.1 Asynchronous Mode                               |    |

|   | 6.5.2 Synchronous Mode:                               |    |

|   | 6.5.3 Daisy Chain Operation                           |    |

| 7 | FUNCTIONAL DESCRIPTION                                |    |

| - | 7.1 I/O Electrical Interface                          |    |

|   | 7.1.1 Current Sink                                    |    |

|   | 7.1.2 Voltage Monitor                                 |    |

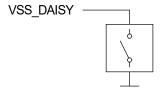

|   | 7.1.3 Daisy-Chain GND                                 |    |

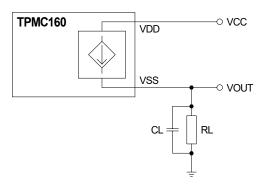

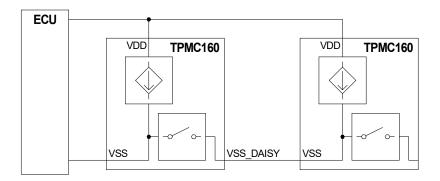

|   | 7.1.4 Typical Test and Application Circuits           |    |

|   | 7.2 Supported Protocols                               |    |

|   | 7.2.1 Wheel Speed                                     |    |

|   | 7.2.1.1 Square Wave "Speed Protocol" or "Duty Cycle"  |    |

|   | 7.2.1.2 "PWM"                                         |    |

|   | 7.2.1.3 "AK-Protocol" or "VDA"                        | 63 |

|   | 7.2.1.4 Custom Protocol                               |    |

|   | 7.2.2 PSI5                                            |    |

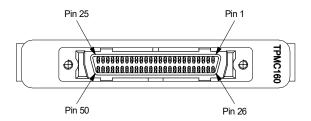

| 8 | PIN ASSIGNMENT – I/O CONNECTOR                        |    |

| 5 |                                                       |    |

|   | 8.1 Front Panel I/O Connector                         | 65 |

## **List of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                                          | 8  |

|--------------------------------------------------------------------|----|

| FIGURE 5-1: SQUARE WAVE PROTOCOL                                   | 22 |

| FIGURE 5-2: PWM WAVE PROTOCOL                                      | 24 |

| FIGURE 5-3: AK-PROTOCOL                                            | 26 |

| FIGURE 7-1: TYPICAL TEST AND APPLICATION CIRCUIT: WHEEL SPEED      | 61 |

| FIGURE 7-2: TYPICAL TEST AND APPLICATION CIRCUIT: PSI5 DAISY CHAIN | 61 |

| FIGURE 7-3: SPEED PROTOCOL / DUTY CYCLE DIAGRAM                    | 62 |

| FIGURE 7-4: PWM DIAGRAM                                            | 62 |

| FIGURE 7-5: AK-PROTOCOL / VDA DIAGRAM                              | 63 |

| FIGURE 7-6: PSI5 DIAGRAM                                           | 64 |

| FIGURE 8-1: FRONT PANEL I/O CONNECTOR PIN NUMBERING                | 65 |

| List of Tables                                                     |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                                 | 9  |

| TABLE 5-1: PCI IDENTIFIERS                                         | 12 |

| TABLE 5-2: PCI BASE ADDRESS REGISTERS                              | 12 |

| TABLE 5-3: REGISTER SPACE                                          | 13 |

| TABLE 5-4: CONTROL REGISTER                                        | 14 |

| TABLE 5-5 : CURRENT LEVEL REGISTERS                                | 15 |

| TABLE 5-6: ADC DATA REGISTER CH0-1                                 | 16 |

| TABLE 5-7: ADC DATA REGISTER CH2-3                                 | 16 |

| TABLE 5-8: ADC DATA REGISTER CH4-5                                 | 16 |

| TABLE 5-9: ADC DATA REGISTER CH6-7                                 | 17 |

| TABLE 5-10 : CP CYCLE REGISTERS                                    | 19 |

| TABLE 5-11 : CP FIFO STATUS REGISTER                               | 20 |

| TABLE 5-12 : CP FIFO DATA REGISTERS                                | 21 |

| TABLE 5-13: SWP CYCLE REGISTERS                                    | 23 |

| TABLE 5-14: PWM CYCLE REGISTERS                                    | 25 |

| TABLE 5-15: AK CYCLE REGISTERS                                     | 26 |

| TABLE 5-16: AK CONTROL REGISTERS                                   | 28 |

| TABLE 5-17: PSI5 CYCLE REGISTERS                                   | 29 |

| TABLE 5-18: PSI5 INTERRUPT STATUS REGISTERS                        | 31 |

| TABLE 5-19: PSI5 STATUS REGISTERS                                  | 32 |

| TABLE 5-20: PSI5 DETECTION REGISTERS                               | 33 |

| TABLE 5-21: PSI5 CONTROL REGISTERS                                 | _  |

| TABLE 5-22 : PSI5 CONTROL REGISTERS                                |    |

| TABLE 5-23: PSI5 DATA FRAME FIFO REGISTERS                         | 36 |

| TABLE 5-24: PSI5 FIFO STATUS REGISTER                              |    |

| TABLE 5-25: PSI5 SYNC DATA REGISTERS                               | 38 |

| TABLE 5-26 : CYCLE COUNTER    | CONTROL REGISTER     | 41 |

|-------------------------------|----------------------|----|

| TABLE 5-27 : CYCLE COUNTER I  | MATCH REGISTER CH0-1 | 42 |

| TABLE 5-28 : CYCLE COUNTER    | MATCH REGISTER CH2-3 | 42 |

| TABLE 5-29 : CYCLE COUNTER    | MATCH REGISTER CH4-5 | 42 |

| TABLE 5-30 : CYCLE COUNTER    | MATCH REGISTER CH6-7 | 42 |

| TABLE 5-31 : CYCLE COUNTER '  | VALUE REGISTER CH0-1 | 43 |

| TABLE 5-32 : CYCLE COUNTER '  | VALUE REGISTER CH2-3 | 43 |

| TABLE 5-33 : CYCLE COUNTER    | VALUE REGISTER CH4-5 | 43 |

| TABLE 5-34 : CYCLE COUNTER '  | VALUE REGISTER CH6-7 | 43 |

| TABLE 5-35 : INTERRUPT ENABL  | LE REGISTER          | 44 |

| TABLE 5-36 : PSI5 IRQ TRIGGER | ENABLE REGISTER      | 46 |

| TABLE 5-37 : INTERRUPT STATU  | JS REGISTER          | 46 |

| TABLE 5-38 : EXTENDED CYCLE   | REGISTERS            | 47 |

| TABLE 5-39 : EXTENDED TP REG  | SISTERS              | 48 |

| TABLE 5-40 : BOARD HEALTH RI  | EGISTER              | 49 |

| TABLE 5-41 : SCRATCHPAD REC   | GISTER               | 49 |

| TABLE 5-42 : FIRMWARE IDENTI  | FICATION REGISTER    | 49 |

| TABLE 7-1:CHANNEL SIGNAL L    | INES TO FPGA         | 59 |

| TABLE 7-2 : CURRENT SINK CHA  | ARACTERISTICS        | 59 |

| TABLE 7-3: VOLTAGE MONITOR    | CHARACTERISTICS      | 60 |

| TABLE 8-1: PIN ASSIGNMENT F   | RONT I/O CONNECTOR   | 66 |

## 1 Product Description

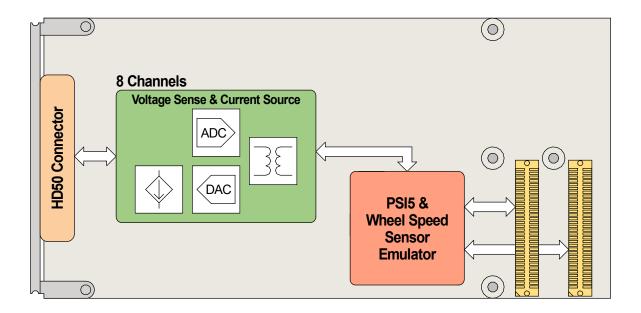

The TPMC160 is a standard single-width 32 bit PMC module and supports a 33 MHz / 32-bit universal (5 V / 3.3 V) PCI interface.

The TPMC160 offers eight isolated automotive sensor simulator channels, which can act as a PSI5 or as wheel speed sensor. The sensor simulation supports a current sink with three adjustable levels. It also features PSI5 Sync and Reset pulse detection. The sensor simulation channels are isolated against the system and against each other.

PSI5 support includes PSI5-P, -U and -D bus topologies and both 125 kbps and 189 kbps transmission rates. Asynchronous and Variable Time Triggered Synchronous Operation Modes are supported.

Wheel speed sensor support covers two- and three current levels sensors, sensors with additional status information and the "AK-protocol".

All TPMC160 signals are accessible through a HD50 SCSI-2 type front I/O connector.

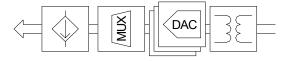

Figure 1-1: Block Diagram

## **2** Technical Specification

| PMC Interface                                                                         |                                                                                      |  |  |  |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| Mechanical Interface  PCI Mezzanine Card (PMC) Interface Single Size (149 mm x 74 mm) |                                                                                      |  |  |  |

| Electrical Interface                                                                  | PCI Rev. 3.0 compliant<br>33 MHz / 32 bit PCI<br>3.3 V and 5 V PCI Signaling Voltage |  |  |  |

| On Board Devices |                            |

|------------------|----------------------------|

| PCI Target Chip  | Artix-7 FPGA with PCI core |

| I/O Interface                                                 |                            |  |  |  |

|---------------------------------------------------------------|----------------------------|--|--|--|

| Number of Channels 8                                          |                            |  |  |  |

| I/O Standards                                                 | PSI5<br>Wheel Speed Sensor |  |  |  |

| Sensor Supply                                                 | 4-24 V                     |  |  |  |

| I/O Connector HD50 SCSI-2 type connector (e.g. AMP# 787395-5) |                            |  |  |  |

| Physical Data                            |                                                                                                                                                                                                                                                                                                                                                     |            |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Power Requirements 450 mA typical @ +5 V |                                                                                                                                                                                                                                                                                                                                                     | cal @ +5 V |  |  |

| Temperature Range                        | Operating -40°C to +85°C<br>Storage -40°C to +85°C                                                                                                                                                                                                                                                                                                  |            |  |  |

| MTBF                                     | 369 000 h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: $G_B$ 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |            |  |  |

| Humidity                                 | 5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                             |            |  |  |

| Weight                                   | 77 g                                                                                                                                                                                                                                                                                                                                                |            |  |  |

Table 2-1: Technical Specification

## 3 Handling and Operation Instructions

#### 3.1 ESD Protection

This PMC module is sensitive to static electricity.

Packing, unpacking and all other module handling has to be done with appropriate care.

## 3.2 Power Dissipation

This PMC module requires adequate forced air cooling!

## 3.3 Ground for Isolated I/O

I/O Connector's isolated ground signals must be connected to external ground.

## 4 Terms and Definitions

## 4.1 Register Bit Access Types

| Register Bit Access<br>Type |            | Description                                                                                            |  |  |

|-----------------------------|------------|--------------------------------------------------------------------------------------------------------|--|--|

| R                           | Read       | The bit is readable by software                                                                        |  |  |

| R/W                         | Read/Write | The bit is readable and writeable by software                                                          |  |  |

| R/C                         | Read/Clear | The bit is readable by software The bit is set by firmware Software may clear the bit by writing a '1' |  |  |

| R/S                         | Read/Set   | The bit is readable by software Software may set this bit to '1' The bit is cleared by firmware        |  |  |

When reading reserved register bits, the read value is undefined.

For future software compatibility: For register write access reserved bits shall be written '0'.

## 4.2 Style Conventions

Hexadecimal characters are specified with prefix 0x (i.e. 0x029E).

For signals on hardware products, "Active Low" is represented by the signal name with an added # (i.e. IP\_RESET#).

## 5 PCI Interface

## 5.1 Identifiers

| Vendor-ID           | 0x1498 (TEWS Technologies)                                      |  |  |

|---------------------|-----------------------------------------------------------------|--|--|

| Device-ID           | 0x00A0 (TPMC160)                                                |  |  |

| Class Code          | 0x118000 (Other data acquisition/signal processing controllers) |  |  |

| Subsystem Vendor-ID | 0x1498 (TEWS Technologies)                                      |  |  |

| Subsystem Device-ID | 0x000A (TPMC160-10R)                                            |  |  |

Table 5-1: PCI Identifiers

## **5.2 PCI Base Address Register Configuration**

| PCI Base Address Register<br>(Offset in PCI<br>Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description    |

|---------------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|----------------|

| 0 (0x10)                                                            | MEM                     | 4096           | 32                     | Little         | Register Space |

Table 5-2: PCI Base Address Registers

## 5.3 Register Space

## 5.3.1 Register Map

| PCI Base Address<br>Register 0 Offset | Description                    | Size<br>(Bit) |  |  |  |

|---------------------------------------|--------------------------------|---------------|--|--|--|

|                                       | Common Protocol Registers      | ·             |  |  |  |

| 0x000                                 | Channel Control Register       | 32            |  |  |  |

| 0x004 - 0x020                         | Current Level Registers        | 32            |  |  |  |

| 0x024 - 0x030                         | ADC Data Registers             | 32            |  |  |  |

| 0x034 - 0x04C                         | Reserved                       | 32            |  |  |  |

|                                       | Custom Protocol Registers      |               |  |  |  |

| 0x050 - 0x06C                         | CP Cycle Registers             | 32            |  |  |  |

| 0x070                                 | CP FIFO Status Register        | 32            |  |  |  |

| 0x074 - 0x090                         | CP FIFO Data Registers         | 32            |  |  |  |

| 0x094 - 0x0AC                         | Reserved                       | 32            |  |  |  |

|                                       | Square Wave Protocol Registers | ·             |  |  |  |

| 0x0B0 - 0x0CC                         | SWP Cycle Registers            | 32            |  |  |  |

| 0x0D0 - 0x11C                         | Reserved                       | 32            |  |  |  |

|                                       | PWM Protocol Registers         |               |  |  |  |

| 0x120 - 0x13C                         | PWM Cycle Registers            | 32            |  |  |  |

| 0x140 - 0x15C                         | Reserved                       | 32            |  |  |  |

| PCI Base Address<br>Register 0 Offset | Description                             | Size<br>(Bit) |  |  |  |

|---------------------------------------|-----------------------------------------|---------------|--|--|--|

| AK / VDA Protocol Registers           |                                         |               |  |  |  |

| 0x160 - 0x17C                         | AK Cycle Registers                      | 32            |  |  |  |

| 0x180 - 0x19C                         | AK Control Registers                    | 32            |  |  |  |

| 0x1A0 - 0x21C                         | Reserved                                | 32            |  |  |  |

|                                       | PSI5 Mode Registers                     |               |  |  |  |

| 0x220 - 0x23C                         | PSI5 Cycle Registers                    | 32            |  |  |  |

| 0x240                                 | PSI5 Interrupt Status Register          | 32            |  |  |  |

| 0x244 - 0x260                         | PSI5 Status Registers                   | 32            |  |  |  |

| 0x264 - 0x280                         | PSI5 Detection Registers                | 32            |  |  |  |

| 0x284 - 0x2A0                         | PSI5 Control Registers                  | 32            |  |  |  |

| 0x2A4 - 0x2E0                         | Reserved                                | 32            |  |  |  |

| 0x2E4 - 0x300                         | PSI5 Default Data Frame Registers       | 32            |  |  |  |

| 0x304 - 0x320                         | PSI5 Transmit Data Frame FIFO Registers | 32            |  |  |  |

| 0x324                                 | PSI5 FIFO Status Register               | 32            |  |  |  |

| 0x328 - 0x32C                         | Reserved                                | 32            |  |  |  |

| 0x330 - 0x34C                         | PSI5 SYNC Data Registers                | 32            |  |  |  |

| 0x350 - 0x36C                         | Reserved                                | 32            |  |  |  |

|                                       | Cycle Counter Registers                 |               |  |  |  |

| 0x370                                 | Cycle Counter Control Register          | 32            |  |  |  |

| 0x374 - 0x380                         | Cycle Counter Match Registers           | 32            |  |  |  |

| 0x384 - 0x390                         | Cycle Counter Value Registers           | 32            |  |  |  |

| 0x400 - 0x41C                         | Reserved                                | 32            |  |  |  |

|                                       | Interrupt Registers                     |               |  |  |  |

| 0x420                                 | Interrupt Enable Register               | 32            |  |  |  |

| 0x424                                 | PSI5 Status IRQ Trigger Register        | 32            |  |  |  |

| 0x428                                 | Interrupt Status Register               | 32            |  |  |  |

| 0x42C - 0x4FC                         | Reserved                                | 32            |  |  |  |

|                                       | Extended Timer Registers                |               |  |  |  |

| 0x500 - 0x51C                         | Extended Cycle Register                 | 32            |  |  |  |

| 0x520 - 0x53C                         | Extended TP Register                    | 32            |  |  |  |

| 0x540 - 0xFF0                         | Reserved                                | 32            |  |  |  |

|                                       | Board Status Registers                  |               |  |  |  |

| 0xFF4                                 | Board Health Register                   | 32            |  |  |  |

| 0xFF8                                 | Scratchpad Register                     | 32            |  |  |  |

| 0xFFC                                 | Firmware Identification Register        | 32            |  |  |  |

Table 5-3: Register Space

## **5.3.2 Common Protocol Registers**

These registers are not protocol specific, and are used by all protocols.

#### 5.3.2.1 Channel Control Register: 0x000

| Bit   | Symbol | Description                      | Access | Reset<br>Value |

|-------|--------|----------------------------------|--------|----------------|

| 31:29 | MODE7  | Protocol selection for Channel 7 | R/W    | 0x0            |

| 27:24 | MODE6  | Protocol selection for Channel 6 | R/W    | 0x0            |

| 23:20 | MODE5  | Protocol selection for Channel 5 | R/W    | 0x0            |

| 19:16 | MODE4  | Protocol selection for Channel 4 | R/W    | 0x0            |

| 15:12 | MODE3  | Protocol selection for Channel 3 | R/W    | 0x0            |

| 11:8  | MODE2  | Protocol selection for Channel 2 | R/W    | 0x0            |

| 7:4   | MODE1  | Protocol selection for Channel 1 | R/W    | 0x0            |

| 3:0   | MODE0  | Protocol selection for Channel 0 | R/W    | 0x0            |

Table 5-4: Control Register

For each of the eight channels the protocol is freely selectable. Protocol options:

| MODE   | Description                              |

|--------|------------------------------------------|

| 0x0    | Channel disabled                         |

| 0x1    | Custom protocol / Manual current setting |

| 0x2    | Square Wave Protocol                     |

| 0x3    | PWM Protocol                             |

| 0x4    | AK Protocol / VDA Protocol               |

| 0x5    | PSI5 Protocol                            |

| Others | Reserved                                 |

#### **5.3.2.2 Current Level Registers 0x004 – 0x020**

| Bit   | Symbol  | Description                                                                        | Access | Reset<br>Value |

|-------|---------|------------------------------------------------------------------------------------|--------|----------------|

| 31:30 | -       | Reserved'                                                                          | -      | -              |

| 29:20 | HIGH[x] | HIGH Current Level Setting for Channel [x] HIGH = Desired Current (μA) / 73.85 μΑ  | R/W    | 0              |

| 19:10 | MID[x]  | MID Current Level Setting for Channel [x] MID = Desired Current (μA) / 73.85 μA    | R/W    | 0              |

| 9:0   | LOW[x]  | LOW Current Level Setting for Channel [x]<br>LOW = Desired Current (μA) / 73.85 μA | R/W    | 0              |

Table 5-5: Current Level Registers

For each channel a current level register is provided, in which three adjustable values, LOW, MID, and HIGH can be defined.

The Custom protocol and the AK protocol use all three current levels. The other protocols just use the HIGH and LOW current level.

Typical values for these protocols are:

| Protocol                  | HIGH  | MID    | LOW   |

|---------------------------|-------|--------|-------|

| Square Wave Protocol      | 14 mA | unused | 7 mA  |

| PWM Protocol              | 14 mA | unused | 7 mA  |

| AK Protocol / VD Protocol | 28 mA | 14 mA  | 7 mA  |

| PSI5 Protocol             | 26 mA | unused | 19 mA |

| Register                         | Bar Offset |

|----------------------------------|------------|

| Current Level Register Channel 0 | 0x004      |

| Current Level Register Channel 1 | 800x0      |

| Current Level Register Channel 2 | 0x00C      |

| Current Level Register Channel 3 | 0x010      |

| Current Level Register Channel 4 | 0x014      |

| Current Level Register Channel 5 | 0x018      |

| Current Level Register Channel 6 | 0x01C      |

| Current Level Register Channel 7 | 0x020      |

#### 5.3.2.3 ADC Data Register Ch0-1 0x024

| Bit   | Symbol | Description                                                   | Access | Reset<br>Value |

|-------|--------|---------------------------------------------------------------|--------|----------------|

| 31:26 | -      | Reserved                                                      | -      | -              |

| 25:16 | ADC1   | Last sampled ADC value of Channel 1 Voltage = ADC1 * 26.16 mV | R      | 0              |

| 15:10 | -      | Reserved                                                      | -      | -              |

| 9:0   | ADC0   | Last sampled ADC value of Channel 0 Voltage = ADC0 * 26.16 mV | R      | 0              |

Table 5-6: ADC Data Register Ch0-1

A new value is provided every 1.6 µs.

#### 5.3.2.4 ADC Data Register Ch2-3 0x028

| Bit   | Symbol | Description                                                   | Access | Reset<br>Value |

|-------|--------|---------------------------------------------------------------|--------|----------------|

| 31:26 | -      | Reserved                                                      | -      | -              |

| 25:16 | ADC3   | Last sampled ADC value of Channel 3 Voltage = ADC3 * 26.16 mV | R      | 0              |

| 15:10 | -      | Reserved                                                      | -      | -              |

| 9:0   | ADC2   | Last sampled ADC value of Channel 2 Voltage = ADC2 * 26.16 mV | R      | 0              |

Table 5-7: ADC Data Register Ch2-3

A new value is provided every 1.6 µs.

#### 5.3.2.5 ADC Data Register Ch4-5 0x02C

| Bit   | Symbol | Description                                                   | Access | Reset<br>Value |

|-------|--------|---------------------------------------------------------------|--------|----------------|

| 31:26 | -      | Reserved                                                      | -      | -              |

| 25:16 | ADC5   | Last sampled ADC value of Channel 5 Voltage = ADC5 * 26.16 mV | R      | 0              |

| 15:10 | -      | Reserved                                                      | -      | -              |

| 9:0   | ADC4   | Last sampled ADC value of Channel 4 Voltage = ADC4 * 26.16 mV | R      | 0              |

Table 5-8: ADC Data Register Ch4-5

A new value is provided every 1.6 µs.

## 5.3.2.6 ADC Data Register Ch6-7 0x030

| Bit   | Symbol | Description                                                   | Access | Reset<br>Value |

|-------|--------|---------------------------------------------------------------|--------|----------------|

| 31:26 | -      | Reserved                                                      | -      | -              |

| 25:16 | ADC7   | Last sampled ADC value of Channel 7 Voltage = ADC7 * 26.16 mV | R      | 0              |

| 15:10 | -      | Reserved                                                      | -      | -              |

| 9:0   | ADC6   | Last sampled ADC value of Channel 6 Voltage = ADC6 * 26.16 mV | R      | 0              |

Table 5-9: ADC Data Register Ch6-7

A new value is provided every 1.6  $\mu s$ .

#### 5.3.3 Custom Protocol Registers

The TPMC160 supports custom protocols by allowing the manual setting of the current level. This can be done either directly through the CP[x] DEFAULT bits, or as a sequence through the CP FIFO.

After starting a sequence, each current level is provided one after the other for a duration of CP[x] TP. As soon as the Manual Sequence FIFO is empty the corresponding output is set to the value defined by the CP[x] DEFAULT bits. After filling the FIFO again, the next sequence can be started.

#### 5.3.3.1 CP Cycle Registers 0x050 – 0x06C

| Bit   | Symbol                 | Description                                                                                                                                                                                                                                                            | Access | Reset<br>Value |

|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:30 | CP[x]<br>DEFAULT       | Default Current Level of Channel [x]  Determines which current level, defined in the Channel's "Current Level Register", shall be used as default output current:  0x0 = Off  0x1 = LOW  0x2 = MID  0x3 = HIGH                                                         | R/W    | 0              |

| 29:28 | CP[x] TP<br>BASE       | Channel [x]: Time base used for the Custom Protocol bit width.  0x0 = 50 ns time base  0x1 = 0.1 µs time base  0x2 = 1 µs time base  0x3 = 1 ms time base  A new value becomes active as soon as the current pulse is completed.                                       | R/W    | 0              |

| 27:16 | CP[x] TP               | Channel [x]: Custom protocol bit width.  Bit width of a single bit in the corresponding protocol. The time base depends on the CP[x] TP BASE.  A new value becomes active as soon as the currently transmitted pulse is completed.                                     | R/W    | 0              |

| 15    | CP[x]<br>TRIG          | Channel [x]: Manual Trigger for the Custom Protocol Starts the transfer of the full content of the sequence stored in the Custom Protocol FIFO. Only valid if CP[x] MODE is set to 0 and no sequence is currently transferred. The bit is cleared automatically.       | R/S    | 0              |

| 14    | CP[X]<br>MODE          | Channel [x]: Custom Protocol Trigger Selection 0 = Manual Mode, Triggered by CP[x] TRIG 1 = Sequencer Mode Triggered via the CP[x] CYCLE timer.                                                                                                                        | R/W    | 0              |

| 13:12 | CP[x]<br>CYCLE<br>BASE | Channel [x]: Time base used for the Custom Protocol Cycle Time $0x0 = 50$ ns time base $0x1 = 0.1 \mu s$ time base $0x2 = 1 \mu s$ time base $0x3 = 1 \mu s$ time base $0x3 = 1 \mu s$ time base A new value becomes active as soon as the current cycle is completed. | R/W    | 0              |

| Bit  | Symbol         | Description                                                                                                                                            | Access | Reset<br>Value |

|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 11:0 | CP[x]<br>CYCLE | Channel [x]: Custom Protocol Cycle Time The time base depends on CP[x] CYCLE BASE. The value has to be longer than the sequence stored in the CP FIFO. | R/W    | 0              |

|      |                | A new value becomes active as soon as the current cycle is completed.                                                                                  |        |                |

Table 5-10 : CP Cycle Registers

A long timer value of the pulse width or cycle time can be reset by disabling the protocol via the Channel Control Register.

| Register                    | Bar Offset |

|-----------------------------|------------|

| CP Cycle Register Channel 0 | 0x050      |

| CP Cycle Register Channel 1 | 0x054      |

| CP Cycle Register Channel 2 | 0x058      |

| CP Cycle Register Channel 3 | 0x05C      |

| CP Cycle Register Channel 4 | 0x060      |

| CP Cycle Register Channel 5 | 0x064      |

| CP Cycle Register Channel 6 | 0x068      |

| CP Cycle Register Channel 7 | 0x06C      |

## 5.3.3.2 CP FIFO Status Register 0x070

| Bit  | Symbol           | Description                                                                | Access | Reset<br>Value |

|------|------------------|----------------------------------------------------------------------------|--------|----------------|

| 31:8 | -                | Reserved                                                                   | -      | -              |

| 15   | CP FIFO7<br>RST  | reset of the channel 7 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 14   | CP FIFO6<br>RST  | reset of the channel 6 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 13   | CP FIFO5<br>RST  | reset of the channel 5 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 12   | CP FIFO4<br>RST  | Reset of the channel 4 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 11   | CP FIFO3<br>RST  | Reset of the channel 3 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 10   | CP FIFO2<br>RST  | Reset of the channel 2 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 9    | CP FIFO1<br>RST  | Reset of the channel 1 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 8    | CP FIFO0<br>RST  | Reset of the channel 0 Custom Protocol FIFO Writing a '1' flushes the FIFO | R/C    | 0              |

| 7    | CP FIFO7<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 7                    | R      | 0              |

| 6    | CP FIFO6<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 6                    | R      | 0              |

| 5    | CP FIFO5<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 5                    | R      | 0              |

| 4    | CP FIFO4<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 4                    | R      | 0              |

| 3    | CP FIFO3<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 3                    | R      | 0              |

| 2    | CP FIFO2<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 2                    | R      | 0              |

| 1    | CP FIFO1<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 1                    | R      | 0              |

| 0    | CP FIFO0<br>FULL | FIFO full flag of the Custom Protocol FIFO of channel 0                    | R      | 0              |

Table 5-11: CP FIFO Status Register

#### 5.3.3.3 CP FIFO Data Registers 0x074 – 0x090

| Bit   | Symbol   | Description                             | Access | Reset<br>Value |

|-------|----------|-----------------------------------------|--------|----------------|

| 31:30 | CP[x]_15 | Current Level setting 15 of channel [x] | W      | 0              |

|       |          | Same as CP[x] DEFAULT:                  |        |                |

|       |          | 00 = Off                                |        |                |

|       |          | 01 = LOW                                |        |                |

|       |          | 10 = MID<br>11 = HIGH                   |        |                |

| 29:28 | CP[x]_14 | Current Level setting 14 of channel [x] | W      | 0              |

| 27:26 | CP[x]_13 | Current Level setting 13 of channel [x] | W      | 0              |

| 25:24 | CP[x]_12 | Current Level setting 12 of channel [x] | W      | 0              |

| 23:22 | CP[x]_11 | Current Level setting 11 of channel [x] | W      | 0              |

| 21:20 | CP[x]_10 | Current Level setting 10 of channel [x] | W      | 0              |

| 19:18 | CP[x]_9  | Current Level setting 9 of channel [x]  | W      | 0              |

| 17:16 | CP[x]_8  | Current Level setting 8 of channel [x]  | W      | 0              |

| 15:14 | CP[x]_7  | Current Level setting 7 of channel [x]  | W      | 0              |

| 13:12 | CP[x]_6  | Current Level setting 6 of channel [x]  | W      | 0              |

| 11:10 | CP[x]_5  | Current Level setting 5 of channel [x]  | W      | 0              |

| 9:8   | CP[x]_4  | Current Level setting 4 of channel [x]  | W      | 0              |

| 7:6   | CP[x]_3  | Current Level setting 3 of channel [x]  | W      | 0              |

| 5:4   | CP[x]_2  | Current Level setting 2 of channel [x]  | W      | 0              |

| 3:2   | CP[x]_1  | Current Level setting 1 of channel [x]  | W      | 0              |

| 1:0   | CP[x]_0  | Current Level setting 0 of channel [x]  | W      | 0              |

Table 5-12: CP FIFO Data Registers

Writing to the CP FIFO Data Register fills a FIFO that can hold up to 16 x 16 (=256) current level settings. If a channel is triggered in the custom protocol, the current FIFO contents are transmitted. Fill unneeded current level settings within the CP FIFO Data Registers with the CP[x] DEFAULT or with the OFF value (as appropriate for the implemented protocol).

| Register                        | Bar Offset |

|---------------------------------|------------|

| CP FIFO Data Register Channel 0 | 0x074      |

| CP FIFO Data Register Channel 1 | 0x078      |

| CP FIFO Data Register Channel 2 | 0x07C      |

| CP FIFO Data Register Channel 3 | 0x080      |

| CP FIFO Data Register Channel 4 | 0x084      |

| CP FIFO Data Register Channel 5 | 0x088      |

| CP FIFO Data Register Channel 6 | 0x08C      |

| CP FIFO Data Register Channel 7 | 0x090      |

#### 5.3.4 Square Wave Protocol Registers

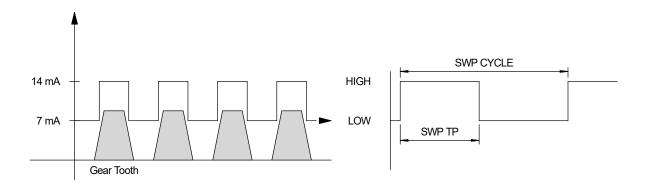

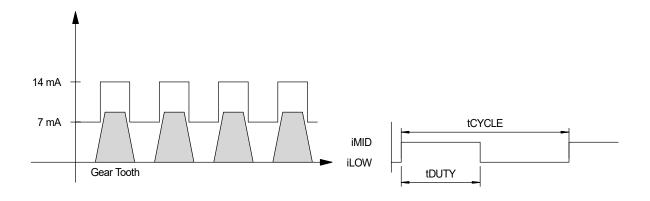

The Square Wave Protocol (SWP) supports mainly the simulation of Standard 2-level (7/14 mA) sensors which work after the "Speed Protocol" or "Duty Cycle" principle.

Figure 5-1: Square Wave Protocol

The Square Wave Protocol uses the HIGH and the LOW Current Level of the Current Level Register.

#### 5.3.4.1 SWP Cycle Registers 0x0B0 - 0x0CC

| Bit   | Symbol                  | Description                                                                                                                                                                                                                                  | Access | Reset<br>Value |

|-------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:30 | -                       | Reserved                                                                                                                                                                                                                                     | -      | -              |

| 29:28 | SWP[x] TP<br>BASE       | Channel [x]: Time base used for the SWP high time SWP[x] TP.  0x0 = 50 ns time base  0x1 = 0.1 µs time base  0x2 = 1 µs time base  0x3 = 1 ms time base  A new value becomes active as soon as the currently transmitted pulse is completed. | R/W    | 0              |

| 27:16 | SWP[x] TP               | Channel [x]: SWP high time SWP TP. The time base depends on the SWP[x] TP Base . A new value becomes active as soon as the currently transmitted pulse is completed.                                                                         | R/W    | 0              |

| 15:14 | -                       | Reserved                                                                                                                                                                                                                                     | -      | -              |

| 13:12 | SWP[x]<br>CYCLE<br>BASE | Channel [x]: Time base used for the SWP Cycle Time SWP[x] CYCLE  0x0 = 50 ns time base  0x1 = 0.1 µs time base  0x2 = 1 µs time base  0x3 = 1 ms time base  A new value becomes active as soon as the current cycle is completed.            | R/W    | 0              |

| Bit  | Symbol          | Description                                                                                                                                       | Access | Reset<br>Value |

|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 11:0 | SWP[x]<br>CYCLE | Channel [x]: SWP Cycle Time The time base depends on the SWP[x] CYCLE BASE. A new value becomes active as soon as the current cycle is completed. | R/W    | 0              |

Table 5-13: SWP Cycle Registers

A long timer value of the pulse width or cycle time can be reset by disabling the protocol via the Channel Control Register.

| Register                     | Bar Offset |

|------------------------------|------------|

| SWP Cycle Register Channel 0 | 0x0B0      |

| SWP Cycle Register Channel 1 | 0x0B4      |

| SWP Cycle Register Channel 2 | 0x0B8      |

| SWP Cycle Register Channel 3 | 0x0BC      |

| SWP Cycle Register Channel 4 | 0x0C0      |

| SWP Cycle Register Channel 5 | 0x0C4      |

| SWP Cycle Register Channel 6 | 0x0C8      |

| SWP Cycle Register Channel 7 | 0x0CC      |

#### 5.3.5 PWM Protocol Registers

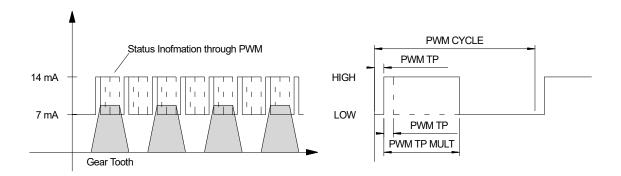

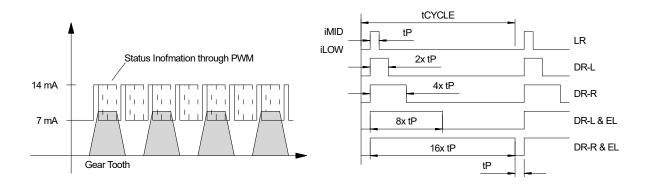

PWM Wheel Speed Sensors transmit additional information by varying the length of the speed pulses.

Figure 5-2: PWM Wave Protocol

PWM encoding is based on the TP setting. All pulse widths are derived from this value. The two current levels of the PWM Protocol are defined as LOW and HIGH in the Current Level Registers.

The usual value for PWM TP is at around 50 µs.

Each sequence starts with a PWM TP wide LOW Level, followed by a HIGH Level of duration PWM TP \* PWM TP MULT. After the cycle time has elapsed, the sequence starts again with the PWM TP wide LOW level.

If the cycle time is too short (less then PWM TP  $^*$  (PWM TP MULT  $\pm$  1)) the sequence interrupted and restarted.

#### 5.3.5.1 PWM Cycle Registers 0x120 - 0x13C

| Bit   | Symbol            | Description                                                                               | Access | Reset<br>Value |

|-------|-------------------|-------------------------------------------------------------------------------------------|--------|----------------|

| 31:20 | PWM[x]<br>TP      | Channel [x]: PWM Protocol bit width TP in 0.1 µs, used for the PWM bit width calculation. | R\W    | 0              |

|       |                   | The time base is always 0.1 µs.                                                           |        |                |

|       |                   | A new value becomes active as soon as the currently transmitted pulse is completed.       |        |                |

| 19:14 | PWM[x]<br>TP MULT | Channel [x]: TP length multiplier                                                         | R\W    | 0              |

|       |                   | 0x0 = no high time                                                                        |        |                |

|       |                   | 0x1 = 1 * PWM[x] TP high time                                                             |        |                |

|       |                   | 0x3F = 63 * PWM[x] TP high time                                                           |        |                |

|       |                   | A new value becomes active as soon as the currently transmitted pulse is completed.       |        |                |

| Bit   | Symbol                  | Description                                                                                                                                                                                                                               | Access | Reset<br>Value |

|-------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 13:12 | PWM[x]<br>CYCLE<br>BASE | Channel [x]: Time base used for the PWM Protocol Cycle Time $0x0 = 50$ ns time base $0x1 = 0.1 \mu s$ time base $0x2 = 1 \mu s$ time base $0x3 = 1 \mu s$ time base A new value becomes active as soon as the current cycle is completed. | R\W    | 0              |

| 11:0  | PWM[x]<br>CYCLE         | Channel [x]: PWM Protocol Cycle Time The time base depends on the PWM[x] CYCLE BASE A new value becomes active as soon as the current cycle is completed.                                                                                 | R\W    | 0              |

Table 5-14: PWM Cycle Registers

A long timer value of the pulse width or cycle time can be reset by disabling the protocol via the Channel Control Register.

| Register                     | Bar Offset |

|------------------------------|------------|

| PWM Cycle Register Channel 0 | 0x120      |

| PWM Cycle Register Channel 1 | 0x124      |

| PWM Cycle Register Channel 2 | 0x128      |

| PWM Cycle Register Channel 3 | 0x12C      |

| PWM Cycle Register Channel 4 | 0x130      |

| PWM Cycle Register Channel 5 | 0x134      |

| PWM Cycle Register Channel 6 | 0x138      |

| PWM Cycle Register Channel 7 | 0x13C      |

#### 5.3.6 AK-Protocol / VDA Registers

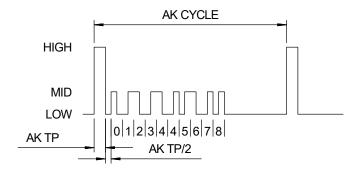

Wheel Speed Sensors with "AK-Protocol" or "VDA" use three current levels and transmit up to 9 status bits after the speed pulse.

Figure 5-3: AK-Protocol

The AK encoding starts with a "speed pulse" with HIGH or MID current level, followed by a short gap, and then followed by the Manchester encoded protocol bits with MID current levels.

#### 5.3.6.1 AK Cycle Registers 0x160 - 0x17C

| Bit   | Symbol                 | Description                                                                                                                                                                                                                   | Access | Reset<br>Value |

|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:28 | -                      | Reserved                                                                                                                                                                                                                      | -      | -              |

| 27:16 | AK[x] TP               | Channel [x]: AK protocol bit width TP in in 0.1 µs.  The time base is always 0.1 µs.  A new value becomes active as soon as the currently transmitted pulse is completed.                                                     | R\W    | 0              |

| 15:14 | -                      | Reserved                                                                                                                                                                                                                      | -      | -              |

| 13:12 | AK[x]<br>CYCLE<br>BASE | Channel [x]: Time base used for the AK Protocol Cycle Time.  0x0 = 50 ns time base  0x1 = 0.1 µs time base  0x2 = 1 µs time base  0x3 = 1 ms time base  A new value becomes active as soon as the current cycle is completed. | R\W    | 0              |

| 11:0  | AK[x]<br>CYCLE         | Channel [x]: AK Protocol Cycle Time The time base depends on the AK[x] CYCLE BASE A new value becomes active as soon as the current cycle is completed.                                                                       | R\W    | 0              |

Table 5-15: AK Cycle Registers

A long timer value of the pulse width or cycle time can be reset by disabling the protocol via the Channel Control Register.

| Register                    | Bar Offset |

|-----------------------------|------------|

| AK Cycle Register Channel 0 | 0x160      |

| AK Cycle Register Channel 1 | 0x164      |

| AK Cycle Register Channel 2 | 0x168      |

| AK Cycle Register Channel 3 | 0x16C      |

| AK Cycle Register Channel 4 | 0x170      |

| AK Cycle Register Channel 5 | 0x174      |

| AK Cycle Register Channel 6 | 0x178      |

| AK Cycle Register Channel 7 | 0x17C      |

## **5.3.6.2 AK Control Registers 0x180 – 0x19C**

| Bit   | Symbol              | Description                                                                                                        | Access | Reset<br>Value |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:16 | -                   | Reserved                                                                                                           | -      | -              |

| 15:12 | AK[x] BIT<br>NUMBER | Channel [x]: Number of bits to transmit. (Excluding speed pulse)                                                   | R/W    | 0              |

|       |                     | 0x0 = No bits are transmitted 0x9 = Nine bits are transmitted >0x9 = reserved                                      |        |                |

| 11:10 | ı                   | Reserved                                                                                                           | -      | -              |

| 9     | AK[x] ASP           | Channel [x]: Artificial Speed Pulse 0 = Normal Speed Pulse (High Current) 1 = Artificial Speed Pulse (Mid Current) | R/W    | 0              |

| 8     | AK[x] B8            | Channel [x]: AK protocol: Bit position 8                                                                           | R/W    | 0              |

| 7     | AK[x] B7            | Channel [x]: AK protocol: Bit position 7                                                                           | R/W    | 0              |

| 6     | AK[x] B6            | Channel [x]: AK protocol: Bit position 6                                                                           | R/W    | 0              |

| 5     | AK[x] B5            | Channel [x]: AK protocol: Bit position 5                                                                           | R/W    | 0              |

| 4     | AK[x] B4            | Channel [x]: AK protocol: Bit position 4                                                                           | R/W    | 0              |

| 3     | AK[x] B3            | Channel [x]: AK protocol: Bit position 3                                                                           | R/W    | 0              |

| 2     | AK[x] B2            | Channel [x]: AK protocol: Bit position 2                                                                           | R/W    | 0              |

| 1     | AK[x] B1            | Channel [x]: AK protocol: Bit position 1                                                                           | R/W    | 0              |

| 0     | AK[x] B0            | Channel [x]: AK protocol: Bit position 0                                                                           | R/W    | 0              |

Table 5-16: AK Control Registers

| Register                      | Bar Offset |

|-------------------------------|------------|

| AK Control Register Channel 0 | 0x180      |

| AK Control Register Channel 1 | 0x184      |

| AK Control Register Channel 2 | 0x188      |

| AK Control Register Channel 3 | 0x18C      |

| AK Control Register Channel 4 | 0x190      |

| AK Control Register Channel 5 | 0x194      |

| AK Control Register Channel 6 | 0x198      |

| AK Control Register Channel 7 | 0x19C      |

#### 5.3.7 PSI5 Protocol Registers

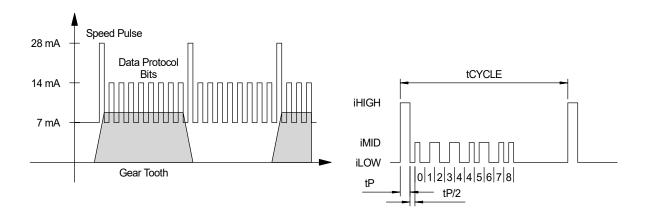

The PSI5 Protocol uses the LOW and HIGH Current Levels of the Current Level Registers.

#### 5.3.7.1 PSI5 Cycle Registers 0x220 - 0x23C

| Bit   | Symbol           | Description                                                                                                                                                                                                                                         | Access | Reset<br>Value |

|-------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:28 | -                | Reserved                                                                                                                                                                                                                                            | -      | -              |

| 27:16 | PSI5[x] TP       | Channel [x]: PSI5 Protocol bit width TP in in 0.1 µs. The time base is always 0.1 µs. This is basically the PSI5 nominal time for a single bit T <sub>BIT</sub> A new value becomes active as soon as the currently transmitted pulse is completed. | R\W    | 0              |

| 15:12 | -                | Reserved                                                                                                                                                                                                                                            | -      | -              |

| 11:0  | PSI5[x]<br>CYCLE | Channel [x]: PSI5 Protocol Cycle Time in µs. The time base is always 1 µs. This is basically the PSI5 sync period T <sub>SYNC</sub> A new value becomes active as soon as the current cycle is completed.                                           | R\W    | 0              |

Table 5-17: PSI5 Cycle Registers

The period duration of a bit PSI5[x] TP is defined for each channel individually. Typical values for a PSI5 sensor are 8.0  $\mu$ s for the 125 kbp/s mode and 5.3  $\mu$ s for the 189 kbp/s mode.

A long timer value of the pulse width or cycle time can be reset by disabling the protocol via the Channel Control Register.

| Register                      | Bar Offset |

|-------------------------------|------------|

| PSI5 Cycle Register Channel 0 | 0x220      |

| PSI5 Cycle Register Channel 1 | 0x224      |

| PSI5 Cycle Register Channel 2 | 0x228      |

| PSI5 Cycle Register Channel 3 | 0x22C      |

| PSI5 Cycle Register Channel 4 | 0x230      |

| PSI5 Cycle Register Channel 5 | 0x234      |

| PSI5 Cycle Register Channel 6 | 0x238      |

| PSI5 Cycle Register Channel 7 | 0x23C      |

## 5.3.7.2 PSI5 Interrupt Status Registers 0x240

For an interrupt status bit to be set, the interrupt must be enabled before the interrupt event.

| Bit | Symbol           | Description                                                                                                               | Access | Reset<br>Value |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31  | PSI5[7]<br>OFLOW | Channel [x]: PSI5[x] SYNC bit overflow.                                                                                   | R/C    | 0              |

| 30  | PSI5[6]<br>OFLOW | After a PSI5[x] SYNC MATCH interrupt is generated, new SYNC pulses are stored in a swap register until the PSI5 SYNC Data | R/C    | 0              |

| 29  | PSI5[5]<br>OFLOW | Registers was read.  If the swap register overflows before PSI5 SYNC Data Registers                                       | R/C    | 0              |

| 28  | PSI5[4]<br>OFLOW | was read and SYNC pulses are lost, corresponding PSI5[x] OFLOW bit is set to '1'.                                         | R/C    | 0              |

| 27  | PSI5[3]<br>OFLOW | This bits are cleared by reading this register.                                                                           | R/C    | 0              |

| 26  | PSI5[2]<br>OFLOW |                                                                                                                           | R/C    | 0              |

| 25  | PSI5[1]<br>OFLOW |                                                                                                                           | R/C    | 0              |

| 24  | PSI5[0]<br>OFLOW |                                                                                                                           | R/C    | 0              |

| 23  | PSI5 [7]<br>SPUR | Channel [x]: PSI5 Spurious Sync signal                                                                                    | R/C    | 0              |

| 22  | PSI5 [6]<br>SPUR | Spurious sync signal detected The SYNC Threshold Voltage was reached outside of the T <sub>TRIG</sub>                     | R/C    | 0              |

| 21  | PSI5 [5]<br>SPUR | window or an invalid SYNC Pulse was detected during the TRIG window.                                                      | R/C    | 0              |

| 20  | PSI5 [4]<br>SPUR | This bits are cleared by reading this register.                                                                           | R/C    | 0              |

| 19  | PSI5 [3]<br>SPUR |                                                                                                                           | R/C    | 0              |

| 18  | PSI5 [2]<br>SPUR |                                                                                                                           | R/C    | 0              |

| 17  | PSI5 [1]<br>SPUR |                                                                                                                           | R/C    | 0              |

| 16  | PSI5 [0]<br>SPUR |                                                                                                                           | R/C    | 0              |

| Bit | Symbol            | Description                                                                                                           | Access | Reset<br>Value |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 15  | PSI5 [7]<br>RESET | Channel [x]: PSI5[x] RESET TTH status                                                                                 | R/C    | 0              |

| 14  | PSI5 [6]<br>RESET | The ADC reading was below the value set in PSI5[x] RESET THRESHOLD for longer than the time set in PSI5[x] RESET TTH. | R/C    | 0              |

| 13  | PSI5 [5]<br>RESET | This bits are cleared by reading this register.                                                                       | R/C    | 0              |

| 12  | PSI5 [4]<br>RESET |                                                                                                                       | R/C    | 0              |

| 11  | PSI5 [3]<br>RESET |                                                                                                                       | R/C    | 0              |

| 10  | PSI5 [2]<br>RESET |                                                                                                                       | R/C    | 0              |

| 9   | PSI5 [1]<br>RESET |                                                                                                                       | R/C    | 0              |

| 8   | PSI5 [0]<br>RESET |                                                                                                                       | R/C    | 0              |

| 7:0 | Reserved          | Reserved                                                                                                              | -      | -              |

Table 5-18: PSI5 Interrupt Status Registers

## 5.3.7.3 PSI5 Status Registers 0x244 – 0x260

| Bit   | Symbol                   |                                          |                                                                                                                                                                                                                                                  | Description                                           |               | Access | Reset<br>Value |

|-------|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------|--------|----------------|

| 31:18 | -                        | Reserved                                 | Reserved                                                                                                                                                                                                                                         |                                                       |               | -      | -              |

| 17:12 | PSI5[x]<br>SYNC<br>CNT   | SYNC Regis<br>SYNC Regis<br>When this va | Channel [x]: This value shows the current unread bits in the PSI5 PYNC Register (0 to 32). This status is reset to 0 when the PSI5 PYNC Register was read.  When this value reaches the PSI5[x] SYNC MATCH value, an atterrupt can be generated. |                                                       |               |        |                |

| 11:10 | -                        | Reserved                                 |                                                                                                                                                                                                                                                  |                                                       |               | -      | -              |

| 9:4   | PSI5[x]<br>FIFO CNT      | Channel [x]:<br>DWORDs (0                |                                                                                                                                                                                                                                                  | ue shows the current PSI5 FIFO                        | fill level in | R      | 0              |

| 3:0   | PSI5[x]<br>SYNC<br>ERROR |                                          |                                                                                                                                                                                                                                                  | ulse Error Status<br>sync signal was a:               |               | R/C    | 0              |

|       | TYPE                     |                                          | Value                                                                                                                                                                                                                                            | Mode                                                  |               |        |                |

|       |                          |                                          | 0000                                                                                                                                                                                                                                             | No unexpected sync pulse detected yet                 |               |        |                |

|       |                          |                                          | 0001                                                                                                                                                                                                                                             | Absence of the sync pulse at the expected time window |               |        |                |

|       |                          |                                          | 0010                                                                                                                                                                                                                                             | Too short for a short pulse                           |               |        |                |

|       |                          |                                          | 0011                                                                                                                                                                                                                                             | Too long for a short pulse too short for a long pulse |               |        |                |