The Embedded I/O Company

# **TPMC530**

### 16/8-Channel Isolated Simultaneous Sampling AD/DA

Version 1.1

### **User Manual**

Issue 1.1.1 December 2017

TEWS TECHNOLOGIES GmbH

Am Bahnhof 7

25469 Halstenbek, Germany

Phone: +49 (0) 4101 4058 0

Fax: +49 (0) 4101 4058 19

e-mail: info@tews.com

www.tews.com

#### **TPMC530-10R**

16 Channels of 16 bit A/D, 8 Channels of 16 bit D/A, with front panel I/O  $\,$

#### **TPMC530-20R**

1

8 Channels of 16 bit A/D, 4 Channels of 16 bit D/A, with front panel I/O

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an <u>,</u>'Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

| W   | Write Only |

|-----|------------|

| R   | Read Only  |

| R/W | Read/Write |

| R/C | Read/Clear |

| R/S | Read/Set   |

|     |            |

©2017 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0.0 | Initial Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | July 2014     |

| 1.0.1 | Minor Clarifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | July 2014     |

| 1.0.2 | Correction of Connector Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | August 2014   |

| 1.0.3 | Added TPMC530-20R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | June 2015     |

| 1.1.0 | <ul> <li>Added "Internal Synchronization" to the ADC &amp; DAC<br/>Configuration Register</li> <li>Added "DAC Suspend on Frame End" to the DAC<br/>Configuration Register</li> <li>Added "DAC Frame Interrupt" to the Interrupt Mask<br/>and Status Register</li> <li>Added DAC Data Readback Register</li> <li>Added Firmware Version Register</li> <li>Added DMA "Bulk" and "Low Latency" Modes to the<br/>DMA Control / Status Register</li> <li>Added FIFO Fill Level Register</li> <li>Updated "6.1.1 DMA Controller" with block-mode<br/>support</li> <li>Updated "6.1.2 DMA Descriptor" with new "EARLY"<br/>and "FRAME" control and status bits</li> <li>Added "6.1.3 DMA FIFO Modes"</li> <li>Updated "6.1.4 DMA Errors" with "EARLY" and<br/>"FRAME" control and status bits</li> </ul> | June 2017     |

|       | Removed Write protection from Correction Value ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

| 1.1.1 | Correction of Figure 7-1: Front Panel I/O Connector Pin<br>Numbering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | December 2017 |

### **Table of Contents**

| 2       TECHNICAL SPECIFICATION         3       ADDRESS MAP         3.1       PCI Configuration Space         3.2.1       Register Space         3.2.2       Correction Value ROM         4       REGISTER DESCRIPTION         4.1       ADC Registers         4.1.1       ADC Control Register         4.1.2       ADC Control Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Configuration Register         4.2.4       DAC Configuration Register         4.2.5       DAC Status Register         4.2.4       DAC Configuration Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register                                            | 9  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1       PCI Configuration Space         3.2       PCI Memory Space         3.2.1       Register Space         3.2.2       Correction Value ROM         4       REGISTER DESCRIPTION         4.1       ADC Registers         4.1.1       ADC Configuration Register         4.1.2       ADC Configuration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.1.7       DAC Data Register         4.2       DAC Configuration Register         4.2.1       DAC Configuration Register         4.2.2       DAC Control Register         4.2.3       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Mask Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Reg                                     | 10 |

| 3.2       PCI Memory Space         3.2.1       Register Space         3.2.2       Correction Value ROM         4       REGISTER DESCRIPTION         4.1       ADC Data Register         4.1.1       ADC Configuration Register         4.1.2       ADC Contriguration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Configuration Register         4.2.4       DAC Condiguration Register         4.2.5       DAC Condiguration Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Load Register         4.3.8       General Registers         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Mask Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register                                             | 12 |

| 3.2       PCI Memory Space         3.2.1       Register Space         3.2.2       Correction Value ROM         4       REGISTER DESCRIPTION         4.1       ADC Data Register         4.1.1       ADC Configuration Register         4.1.2       ADC Contriguration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Configuration Register         4.2.4       DAC Condiguration Register         4.2.5       DAC Condiguration Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Load Register         4.3.8       General Registers         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Mask Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register                                             |    |

| 3.2.1       Register Space         3.2.2       Correction Value ROM.         4       REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.2.2       Correction Value ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4       REGISTER DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 4.1       ADC Registers         4.1.1       ADC Configuration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Data Register         4.2.2       DAC Configuration Register         4.2.3       DAC Configuration Register         4.2.4       DAC Control Register         4.2.5       DAC Status Register         4.2.6       DAC Status Register         4.2.7       DAC Bat Register         4.2.8       DAC Control Register         4.2.4       DAC Cottol Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Tata Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Preload Register         4.3.6       General Purpose Interval Timer Preload Register         4                            |    |

| 4.1.1       ADC Data Register         4.1.2       ADC Configuration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Control Register         4.2.4       DAC Control Register         4.2.5       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.2.7       DAC Data Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register <td>-</td>     | -  |

| 4.1.2       ADC Configuration Register         4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Configuration Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Status Register         4.2.7       DAC Bata Register         4.2.7       DAC Data Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Mask Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Preload Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register         4.3.4       Descriptor Pointer Register         4.3.5       General Purpose Interval Timer Register         4.3.6       General   |    |

| 4.1.3       ADC Control Register         4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.1.0       DAC Registers         4.2.1       DAC Data Register         4.2.2       DAC Configuration Register         4.2.3       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.2.8       Interrupt Mask Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Preload Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register         4.3.4       DMA Control / Status Register         4.3.5       Descriptor Pointer Register         4.3.6       General Purpose Interval Timer Control Register         4.3.6     |    |

| 4.1.4       ADC Conversion Start Register         4.1.5       ADC Status Register         4.1.6       ADC Sample Clock Register         4.2       DAC Registers         4.2.1       DAC Data Register         4.2.2       DAC Configuration Register         4.2.3       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Status Register         4.2.7       DAC Data Readback Register         4.2.7       DAC Data Readback Register         4.2.7       DAC Data Readback Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register         4.3.9       MA Current Descriptor Pointer Register         4.4.1       DMA Current Descriptor Pointer Register         4.4.2       DMA First Descriptor Pointer Register         4.4.4 |    |

| 4.1.6       ADC Sample Clock Register.         4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.2.8       Interrupt Mask Register         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register         4.3.8       Firmware Version Register         4.4.1       DMA Control / Status Register         4.4.2       DMA First Descriptor Pointer Register         4.4.4       FIFO Fill Level Register         4.4.4       FIFO Fill Level Register         5.1       I/O Electrical Interface                             | 19 |

| 4.2       DAC Registers         4.2.1       DAC Configuration Register         4.2.2       DAC Configuration Register         4.2.3       DAC Control Register         4.2.4       DAC Load Register         4.2.5       DAC Status Register         4.2.6       DAC Sample Clock Register         4.2.7       DAC Data Readback Register         4.2.8       General Registers         4.3.1       Interrupt Mask Register         4.3.2       Interrupt Status Register         4.3.3       External Trigger & Sync Register         4.3.4       General Purpose Interval Timer Control Register         4.3.5       General Purpose Interval Timer Register         4.3.6       General Purpose Interval Timer Register         4.3.7       Correction Control/Status Register         4.3.8       Firmware Version Register         4.3.8       Firmware Version Register         4.3.1       DMA Control / Status Register         4.4.2       DMA First Descriptor Pointer Register         4.4.3       DMA Current Descriptor Pointer Register         4.4.4       FIFO Fill Level Register         5       CONFIGURATION HINTS         5.1       I/O Electrical Interface                               |    |

| <ul> <li>4.2.1 DAC Data Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| <ul> <li>4.2.2 DAC Configuration Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21 |

| <ul> <li>4.2.3 DAC Control Register</li> <li>4.2.4 DAC Load Register</li> <li>4.2.5 DAC Status Register</li> <li>4.2.6 DAC Sample Clock Register</li> <li>4.2.7 DAC Data Readback Register</li> <li>4.3 General Registers</li> <li>4.3.1 Interrupt Mask Register</li> <li>4.3.2 Interrupt Status Register</li> <li>4.3.3 External Trigger &amp; Sync Register</li> <li>4.3.4 General Purpose Interval Timer Control Register</li> <li>4.3.5 General Purpose Interval Timer Preload Register</li> <li>4.3.6 General Purpose Interval Timer Register</li> <li>4.3.7 Correction Control/Status Register</li> <li>4.3.8 Firmware Version Register</li> <li>4.4.1 DMA Control / Status Register</li> <li>4.4.2 DMA First Descriptor Pointer Register</li> <li>4.3 DMA Current Descriptor Pointer Register</li> <li>4.4 FIFO Fill Level Register</li> <li>5 CONFIGURATION HINTS</li> </ul>                                                                                                                                                                                                                                                                                                                            | 21 |

| <ul> <li>4.2.4 DAC Load Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22 |

| <ul> <li>4.2.5 DAC Status Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| <ul> <li>4.2.6 DAC Sample Clock Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>4.2.7 DAC Data Readback Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| <ul> <li>4.3 General Registers</li> <li>4.3.1 Interrupt Mask Register</li> <li>4.3.2 Interrupt Status Register</li> <li>4.3.3 External Trigger &amp; Sync Register</li> <li>4.3.4 General Purpose Interval Timer Control Register</li> <li>4.3.5 General Purpose Interval Timer Preload Register</li> <li>4.3.6 General Purpose Interval Timer Register</li> <li>4.3.7 Correction Control/Status Register</li> <li>4.3.8 Firmware Version Register</li> <li>4.4 DMA Registers</li> <li>4.4.1 DMA Control / Status Register</li> <li>4.4.2 DMA First Descriptor Pointer Register</li> <li>4.4.3 DMA Current Descriptor Pointer Register</li> <li>4.4.4 FIFO Fill Level Register</li> <li>5 CONFIGURATION HINTS</li> <li>5.1 I/O Electrical Interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| <ul> <li>4.3.1 Interrupt Mask Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| <ul> <li>4.3.2 Interrupt Status Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>4.3.3 External Trigger &amp; Sync Register</li> <li>4.3.4 General Purpose Interval Timer Control Register</li> <li>4.3.5 General Purpose Interval Timer Preload Register</li> <li>4.3.6 General Purpose Interval Timer Register</li> <li>4.3.7 Correction Control/Status Register</li> <li>4.3.8 Firmware Version Register</li> <li>4.4.1 DMA Control / Status Register</li> <li>4.4.2 DMA First Descriptor Pointer Register</li> <li>4.4.3 DMA Current Descriptor Pointer Register</li> <li>4.4.4 FIFO Fill Level Register</li> <li>5 CONFIGURATION HINTS</li> <li>5.1 I/O Electrical Interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| <ul> <li>4.3.4 General Purpose Interval Timer Control Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| <ul> <li>4.3.5 General Purpose Interval Timer Preload Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| <ul> <li>4.3.6 General Purpose Interval Timer Register</li> <li>4.3.7 Correction Control/Status Register</li> <li>4.3.8 Firmware Version Register</li> <li>4.4 DMA Registers</li> <li>4.4.1 DMA Control / Status Register</li> <li>4.4.2 DMA First Descriptor Pointer Register</li> <li>4.4.3 DMA Current Descriptor Pointer Register</li> <li>4.4.4 FIFO Fill Level Register</li> <li>5 CONFIGURATION HINTS</li> <li>5.1 I/O Electrical Interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| <ul> <li>4.3.7 Correction Control/Status Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| <ul> <li>4.3.8 Firmware Version Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>4.4 DMA Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| <ul> <li>4.4.1 DMA Control / Status Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| <ul> <li>4.4.2 DMA First Descriptor Pointer Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| <ul> <li>4.4.3 DMA Current Descriptor Pointer Register</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4.4.4 FIFO Fill Level Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 5.1 I/O Electrical Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

| 5.1.1 ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38 |

| 5.1.2 DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 5.1.3 DAC Overcurrent Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

| 6 | FUNCT   | IONAL DESCRIPTION         |    |

|---|---------|---------------------------|----|

|   | 6.1 DN  | ИА                        | 40 |

|   | 6.1.1   | DMA Controller            |    |

|   | 6.1.2   | DMA Descriptor            |    |

|   | 6.1.3   | DMA FIFO Modes            |    |

|   | 6.1.4   | DMA Errors                |    |

|   | 6.1.5   | DMA Endianness            |    |

|   | 6.1.6   | DMA Data Buffer Structure |    |

|   | 6.2 Co  | prrection                 | 45 |

|   | 6.2.1   | Internal Correction       |    |

|   | 6.2.2   | Off-Module Correction     | 45 |

|   | 6.3 Tri | igger and Sync            | 46 |

|   | 6.4 Co  | ontinuous Sampling Mode   | 46 |

| 7 | PIN AS  | SIGNMENT – I/O CONNECTOR  |    |

|   | 7.1 Fr  | ont Panel I/O Connector   | 47 |

|   | 7.2 P1  | 4 Back I/O Connector      |    |

## List of Figures

| FIGURE 1-1 : BLOCK DIAGRAM                           | 9  |

|------------------------------------------------------|----|

| FIGURE 6-1 : LINKED DESCRIPTOR LIST                  | 40 |

| FIGURE 6-2 : LINKED DESCRIPTOR LIST EXPANSION        | 41 |

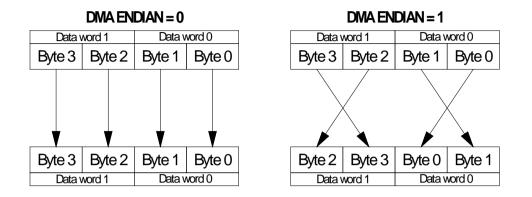

| FIGURE 6-3 : ENDIAN BYTE SWAPS                       | 44 |

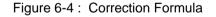

| FIGURE 6-4 : CORRECTION FORMULA                      | 45 |

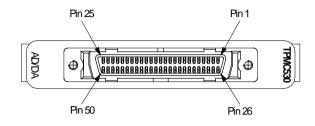

| FIGURE 7-1 : FRONT PANEL I/O CONNECTOR PIN NUMBERING | 47 |

### List of Tables

| TABLE 2-1 : TECHNICAL SPECIFICATION                         | 11 |

|-------------------------------------------------------------|----|

| TABLE 3-1 : PCI CONFIGURATION SPACE HEADER                  | 12 |

| TABLE 3-2 : MEMORY ADDRESS SPACES                           | 13 |

| TABLE 3-3 : REGISTER SPACE ADDRESS MAP                      | 14 |

| TABLE 3-4 : CORRECTION VALUE SPACE ADDRESS MAP              | 15 |

| TABLE 4-1 : ADC DATA REGISTER                               | 16 |

| TABLE 4-2 : ADC DATA CODING EXAMPLE                         | 16 |

| TABLE 4-3 : ADC DATA CODING, BIPOLAR INPUT RANGE            | 16 |

| TABLE 4-4 : ADC CONFIGURATION REGISTER                      | 18 |

| TABLE 4-5 : ADC CONTROL REGISTER                            | 18 |

| TABLE 4-6 : ADC CONVERSION START REGISTER                   | 19 |

| TABLE 4-7 : ADC STATUS REGISTER                             | 19 |

| TABLE 4-8 : ADC SAMPLE CLOCK                                |    |

| TABLE 4-9 : DAC DATA REGISTER                               | 21 |

| TABLE 4-10: DAC DATA CODING, BIPOLAR OUTPUT RANGE           |    |

| TABLE 4-11: DAC DATA CODING, UNIPOLAR OUTPUT RANGE          | 21 |

| TABLE 4-12: DAC CONFIGURATION REGISTER                      | 23 |

| TABLE 4-13: DAC CONTROL REGISTER                            | 24 |

| TABLE 4-14: DAC LOAD REGISTER                               |    |

| TABLE 4-15: DAC STATUS REGISTER                             |    |

| TABLE 4-16: DAC SAMPLE CLOCK REGISTER                       |    |

| TABLE 4-17 : DAC DATA READBACK REGISTER                     | 27 |

| TABLE 4-18: INTERRUPT MASK REGISTER                         |    |

| TABLE 4-19: INTERRUPT STATUS REGISTER                       |    |

| TABLE 4-20: TRIGGER & SYNC REGISTER                         |    |

| TABLE 4-21: GENERAL PURPOSE INTERVAL TIMER CONTROL REGISTER |    |

| TABLE 4-22: GENERAL PURPOSE INTERVAL TIMER CONTROL REGISTER |    |

| TABLE 4-23: GENERAL PURPOSE INTERVAL TIMER REGISTER         |    |

| TABLE 4-24: CORRECTION CONTROL/STATUS REGISTER              |    |

| TABLE 4-25:         FIRMWARE VERSION REGISTER               |    |

| TABLE 4-26: DMA CONTROL / STATUS REGISTER                   |    |

| TABLE 4-27: DMA FIFO MODE                                   |    |

| TABLE 4-28: DMA FIRST DESCRIPTOR POINTER REGISTER           |    |

| TABLE 4-29: DMA CURRENT DESCRIPTOR POINTER REGISTER         |    |

| TABLE 4-30: FIFO FILL LEVEL REGISTER                        |    |

| TABLE 5-1 : ADC ELECTRICAL INTERFACE                        | 38 |

| TABLE 5-2 : ADC INPUT SCHEMES                               |    |

| TABLE 5-3 : DAC ELECTRICAL INTERFACE                        | 38 |

|                                                             |    |

| TABLE 6-1 : DMA DESCRIPTOR                           | 42 |

|------------------------------------------------------|----|

| TABLE 7-1 : PIN ASSIGNMENT FRONT PANEL I/O CONNECTOR | 47 |

| TABLE 7-2 : PIN ASSIGNMENT FRONT PANEL I/O CONNECTOR | 48 |

# 1 **Product Description**

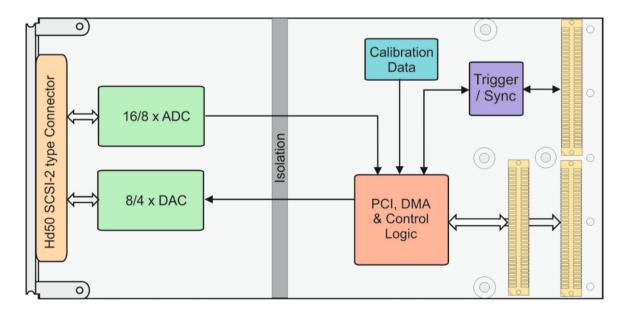

The TPMC530 is a standard single width 32 bit PMC with faceplate I/O. The TPMC530-10R provides 16 channels of isolated 16 bit simultaneous sampling analog input and 8 channels of isolated 16 bit simultaneous update analog output. The TPMC530-20R provides 8 ADC channels and 4 DAC channels. All signals are accessible through a HD50 SCSI-2 type front I/O connector.

The ADC offers true differential inputs with software selectable  $\pm 5$  V and  $\pm 10$  V bipolar input voltage ranges (one setting for all channels). The sampling rate is up to 200 ksps and the ADC offers an oversampling capability with digital filter.

The DAC offers software selectable 0-5 V, 0-10 V, ±5 V and ±10 V output voltage ranges (one setting for all channels). The conversion time is typ. 10  $\mu$ s and the DAC outputs are capable to drive a load of 2 k $\Omega$ , with a capacitance up to 4000 pF.

Both ADC and DAC offer programmable sample clocks. External synchronization is possible with a Trigger/Sync RS485 I/O.

Each ADC / DAC provides a 1024 sample input / output FIFO with programmable trigger levels. Data transfer on the PCI bus is handled by TPMC530 initiated scatter-gather DMA cycles with minimum host/CPU intervention.

Each TPMC530 is factory calibrated. The calibration can be automatically applied to data written to and read from the TPMC530.

Figure 1-1 : Block Diagram

# 2 **Technical Specification**

| PMC Interface         |                                                                                                                   |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mechanical Interface  | PCI Mezzanine Card (PMC) Interface ANSI/VITA 20-2001<br>(R2005)<br>Single Size                                    |  |  |  |  |

| Electrical Interface  | PCI Rev. 3.0 compatible<br>33 MHz / 32 bit PCI<br>3.3 V and 5 V PCI Signaling Voltage                             |  |  |  |  |

| On Board Devices      |                                                                                                                   |  |  |  |  |

| PCI Target Chip       | Spartan-6 FPGA with PCI core                                                                                      |  |  |  |  |

| ADC                   | AD7609                                                                                                            |  |  |  |  |

| DAC                   | AD5754R                                                                                                           |  |  |  |  |

|                       |                                                                                                                   |  |  |  |  |

| Analog Input          |                                                                                                                   |  |  |  |  |

| Resolution            | 16 Bit                                                                                                            |  |  |  |  |

| Input Type            | True bipolar differential input                                                                                   |  |  |  |  |

| Input Voltage Ranges  | Software selectable: ±5 V, ±10 V<br>Maximum ground related voltage on ADC input pins                              |  |  |  |  |

| Full Scale Range      | Software Selectable: ±10 V, ±20 V                                                                                 |  |  |  |  |

| Sample Rate           | 200 ksps                                                                                                          |  |  |  |  |

| Input Impedance       | 1 ΜΩ                                                                                                              |  |  |  |  |

| Protection            | Overvoltage protection up to ±16.5 V, 7 kV ESD rating                                                             |  |  |  |  |

| DNL/INL (typical)     | ±0.75 / ±3 LSB                                                                                                    |  |  |  |  |

| FIFO Size             | 1024 samples                                                                                                      |  |  |  |  |

|                       |                                                                                                                   |  |  |  |  |

| Analog Output         |                                                                                                                   |  |  |  |  |

| Resolution            | 16 Bit                                                                                                            |  |  |  |  |

| Output Type           | Single-ended, software selectable: unipolar / bipolar                                                             |  |  |  |  |

| Output Voltage Ranges | Software selectable: ±5 V, ±10 V, +5 V, +10 V                                                                     |  |  |  |  |

| Settling Time         | 10 µs                                                                                                             |  |  |  |  |

| Output Load           | Max. 2 kΩ   4000 pF per channel                                                                                   |  |  |  |  |

| Protection            | 20 mA current limit, thermal shutdown option, 3.5 kV ESD rating                                                   |  |  |  |  |

| DNL/INL (typical)     | ±1 / ±16 LSB                                                                                                      |  |  |  |  |

| FIFO Size             | 1024 samples                                                                                                      |  |  |  |  |

|                       |                                                                                                                   |  |  |  |  |

| I/O Interface         |                                                                                                                   |  |  |  |  |

| Number of Channels    | 16 (-10R) or 8 (-20R) simultaneous sampling ADC channels<br>8 (-10R) or 4 (-20R) simultaneous update DAC channels |  |  |  |  |

| I/O Connector         | Front I/O: HD50 SCSI-2 type connector (e.g. AMP# 787395-5)<br>PMC P14 I/O (64 pin Mezzanine Connector)            |  |  |  |  |

| Physical Data      |                                                                                                                                                                                                                                                                                                                                                                    |                         |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| Power Requirements | 330 mA typic                                                                                                                                                                                                                                                                                                                                                       | 330 mA typical @ +5V DC |  |  |

| Temperature Range  | Operating-40 °C to +85 °CStorage-40 °C to +85 °C                                                                                                                                                                                                                                                                                                                   |                         |  |  |

| MTBF               | 544.000 h<br>MTBF values shown are based on calculation according to MIL-HDBK-217F and<br>MIL-HDBK-217F Notice 2; Environment: $G_B$ 20°C.<br>The MTBF calculation is based on component FIT rates provided by the<br>component suppliers. If FIT rates are not available, MIL-HDBK-217F and<br>MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                         |  |  |

| Humidity           | 5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                            |                         |  |  |

| Weight             | 78 g                                                                                                                                                                                                                                                                                                                                                               |                         |  |  |

Table 2-1 : Technical Specification

# 3 Address Map

## **3.1 PCI Configuration Space**

| PCI CFG<br>Register | Write '0' to all u                           | Initial Values<br>(Hex Values) |                     |               |             |

|---------------------|----------------------------------------------|--------------------------------|---------------------|---------------|-------------|

| Address             | 31 24                                        | 23 16                          | 15 8                | 7 0           |             |

| 0x00                | Devi                                         | ce ID                          | Vend                | lor ID        | 0212 1498   |

| 0x04                | Sta                                          | itus                           | Com                 | mand          | 0280 0000   |

| 0x08                |                                              | Class Code                     |                     | Revision ID   | 118000 00   |

| 0x0C                | not supported Header Type PCI Latent         |                                |                     | not supported | 00 00 00 00 |

| 0x10                |                                              | Base Address R                 | egister 0 (BAR0)    |               | FFFFF00     |

| 0x14                |                                              | FFFFE00                        |                     |               |             |

| 0x18                |                                              | 00000000                       |                     |               |             |

| 0x1C                |                                              | 00000000                       |                     |               |             |

| 0x20                | not supported                                |                                |                     |               | 00000000    |

| 0x24                | not supported                                |                                |                     | 00000000      |             |

| 0x28                | PC                                           | I CardBus Informa              | tion Structure Poir | nter          | 00000000    |

| 0x2C                | Subsystem ID Subsystem Vendor ID             |                                |                     | s.b. 1498     |             |

| 0x30                | not supported                                |                                |                     | 00000000      |             |

| 0x34                | Reserved New Cap. Ptr.                       |                                |                     | 000000 00     |             |

| 0x38                | Reserved                                     |                                |                     | 00000000      |             |

| 0x3C                | Max_Lat Min_Gnt Interrupt Pin Interrupt Line |                                |                     | 00 00 01 00   |             |

| 0x40-<br>0xFF       | Reserved                                     |                                |                     |               | 0000000     |

Table 3-1 : PCI Configuration Space Header

| Device-ID:              | 0x0212 | TPMC530           |

|-------------------------|--------|-------------------|

| Vendor-ID:              | 0x1498 | TEWS TECHNOLOGIES |

| Subsystem-ID:           | 0x000A | -10R              |

|                         | 0x0014 | -20R              |

| Subsystem<br>Vendor-ID: | 0x1498 | TEWS TECHNOLOGIES |

### 3.2 PCI Memory Space

The TPMC530 maps its internal registers into two address spaces within the PCI memory space, using two Base Address Registers.

| Base<br>Address<br>Register<br>(BAR) | PCI Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description          |

|--------------------------------------|----------------------|----------------|------------------------|----------------|----------------------|

| 0                                    | MEM                  | 256            | 32                     | Little         | Register Space       |

| 1                                    | MEM                  | 512            | 32                     | Little         | Correction Value ROM |

Table 3-2 : Memory Address Spaces

#### 3.2.1 Register Space

The Register Space is accessible via the PCI Base Address Register 0 (BAR0).

| Offset    | Description                      | Size (Bit) |  |  |  |

|-----------|----------------------------------|------------|--|--|--|

|           | ADC Registers                    |            |  |  |  |

| 0x00      | ADC Data Register 1 & 2          | 32         |  |  |  |

|           |                                  | 32         |  |  |  |

| 0x1C      | ADC Data Register 15 & 16        | 32         |  |  |  |

| 0x20      | ADC Configuration Register       | 32         |  |  |  |

| 0x24      | ADC Control Register             | 32         |  |  |  |

| 0x28      | ADC Conversion Start Register    | 32         |  |  |  |

| 0x2C      | ADC Status Register              | 32         |  |  |  |

| 0x30      | ADC Sample Clock                 | 32         |  |  |  |

| 0x34 0x3C | Reserved                         | -          |  |  |  |

|           | DAC Registers                    |            |  |  |  |

| 0x40      | DAC Data Register 1 & 2          | 32         |  |  |  |

|           |                                  | 32         |  |  |  |

| 0x4C      | DAC Data Register 7 & 8          | 32         |  |  |  |

| 0x50      | DAC Configuration Register       | 32         |  |  |  |

| 0x54      | DAC Control Register             | 32         |  |  |  |

| 0x58      | DAC Load Register                | 32         |  |  |  |

| 0x5C      | DAC Status Register              | 32         |  |  |  |

| 0x60      | DAC Sample Clock                 | 32         |  |  |  |

| 0x64 0x6C | Reserved                         | -          |  |  |  |

| 0x70      | DAC Data Readback Register 1 & 2 | 32         |  |  |  |

|           |                                  | 32         |  |  |  |

| 0x7C      | DAC Data Readback Register 7 & 8 | 32         |  |  |  |

|           | General Registers                |            |  |  |  |

| 0x80      | Interrupt Mask Register          | 32         |  |  |  |

| Offset    | Description                                       | Size (Bit) |

|-----------|---------------------------------------------------|------------|