# **TPMC542**

# 16/8 Channel Voltage & Current Range D/A and 20 Channel LVTTL/TTL Digital I/O

Version 1.0

## **User Manual**

Issue 1.0.3 April 2022

e-mail: info@tews.com www.tews.com

#### **TPMC542-10R**

16 Channels of Simultaneous Update Single-Ended 16 bit Voltage & Current Range D/A and 20 Channels of LVTTL/TTL Digital I/O, with MDR68 front panel I/O

(RoHS compliant)

#### TPMC542-20R

8 Channels of Simultaneous Update Single-Ended 16 bit Voltage & Current Range D/A and 20 Channels of LVTTL/TTL Digital I/O, with MDR68 front panel I/O

(RoHS compliant)

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

©2017-2022 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                                                                                                                                                     | Date          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.0.0 | Initial issue                                                                                                                                                                                                                   | April 2017    |

| 1.0.1 | Description Block Diagram                                                                                                                                                                                                       | June 2017     |

| 1.0.2 | Added notes to <i>Technical Specification Table</i> , <i>D/A Channel Output</i> section  Added notes to the <i>Voltage Output Mode</i> and <i>Current Output Mode</i> paragraphs in the <i>Analog Output Interface</i> chapter. | February 2021 |

| 1.0.3 | Added chapter <i>Programming Hints</i> and sub-chapter <i>Global DAC Status</i> Register Read                                                                                                                                   | April 2022    |

# **Table of Contents**

| 1 | PRODUCT DES                | SCRIPTION                                                                                                               | 9        |

|---|----------------------------|-------------------------------------------------------------------------------------------------------------------------|----------|

| 2 | TECHNICAL S                | PECIFICATION                                                                                                            | 11       |

| 3 | HANDLING AN                | ID OPERATION INSTRUCTIONS                                                                                               | 13       |

|   | 3.1 ESD Protec             | tion                                                                                                                    | 13       |

|   |                            | ipation Limit                                                                                                           |          |

|   |                            | Cooling Requirements                                                                                                    |          |

| 4 |                            |                                                                                                                         |          |

| 7 |                            |                                                                                                                         |          |

|   |                            | er & BAR Configuration                                                                                                  |          |

|   |                            | Dace                                                                                                                    |          |

|   | 4.2.1 D/A Glo              | obal Registers                                                                                                          | 19       |

|   |                            | bal DAC Control Register (0x158)                                                                                        |          |

|   |                            | bal DAC Status Register (0x15C)                                                                                         |          |

|   |                            | evice Registers                                                                                                         |          |

|   | 4.2.2.1 DAG<br>4.2.2.2 DAG | C Configuration Register(s) (0x168, 0x198, 0x1C8, 0x1F8)<br>C Correction Registers (0x170, 0x174, 0x178, 0x17C, 0x1A0,) | ۱∠       |

|   | 4.2.2.3 DAG                | C Data Registers (0x180, 0x184, 0x180, 0x184,)                                                                          | 23<br>24 |

|   |                            | C Status Register(s) (0x188, 0x1B8, 0x1E8, 0x218)                                                                       |          |

|   |                            | C Mode Register(s) (0x18C, 0x1BC, 0x1EC, 0x21C)                                                                         |          |

|   |                            | equencer Register                                                                                                       |          |

|   |                            | juencer Control Register (0x2E8)                                                                                        |          |

|   | 4.2.3.2 Sec                | uencer Status Register (0x2EC)                                                                                          | 30       |

|   |                            | nber of Conversions Register (0x2F4)                                                                                    |          |

|   | 4.2.3.4 Cor                | nversion Count Register (0x2F8)                                                                                         | 32       |

|   |                            | O Level Register (0x2FC)                                                                                                |          |

|   |                            | A Buffer Base Address Register (0x308)                                                                                  |          |

|   |                            | A Buffer Length Register (0x30C)                                                                                        |          |

|   |                            | A Buffer Next Address Register (0x310)                                                                                  |          |

|   |                            | rsion Signal Registers                                                                                                  |          |

|   |                            | nversion Clock 1 Generator Register (0x320)                                                                             |          |

|   |                            | nversion Clock 2 Generator Register (0x324)                                                                             |          |

|   |                            | me Trigger Generator Register 1 (0x32C)                                                                                 |          |

|   |                            | me Trigger Generator Register 2 (0x330)<br>nversion Signal Generator Enable Register (0x33C)                            |          |

|   |                            | oversion Signal Generator Citable Register (0x330)                                                                      |          |

|   | 4.2.4.7 Cor                | oversion Signal Source Selection Register (0x344)                                                                       | 38       |

|   |                            | me Timer Register (0x348)                                                                                               |          |

|   |                            | egisters                                                                                                                |          |

|   |                            | Input Register (0x354)                                                                                                  |          |

|   |                            | Input Filter Register (0x358)                                                                                           |          |

|   |                            | Output Register (0x35C)                                                                                                 |          |

|   | 4.2.5.4 DIO                | Output Enable Register (0x360)                                                                                          | 42       |

|   | 4.2.6 Interrup             | pt Registers                                                                                                            | 43       |

|   | 4.2.6.1 Inte               | rrupt Enable Register (0x36C)                                                                                           | 43       |

|   | 4.2.6.2 Erro               | or Interrupt Enable Register (0x370)                                                                                    | 44       |

|   |                            | Rising Edge Interrupt Enable Register (0x374)                                                                           |          |

|   |                            | Falling Edge Interrupt Enable Register (0x378)                                                                          |          |

|   | 4.2.6.5 Inte               | rrupt Status Register (0x384)                                                                                           | 49       |

|   |                            |                                                                                                                         |          |

|    | 4.2.6.6 Error Interrupt Status Register (0x388)                |          |

|----|----------------------------------------------------------------|----------|

|    | 4.2.6.7 DIO Interrupt Status Register (0x38C)                  |          |

|    | 4.2.7 Other Registers                                          | 52       |

|    | 4.2.7.1 Global Configuration Register (0x396)                  | 52<br>53 |

|    | 4.2.7.3 P14 I/O Pull Reference Register (0x3A0)                |          |

|    | 4.2.7.4 Correction Data EEPROM Control/Status Register (0x3A4) |          |

|    | 4.2.7.5 Temperature Sensor Trigger Register (0x3A8)            |          |

|    | 4.2.7.6 Temperature Sensor Data Register (0x3AC)               | 55       |

|    | 4.2.7.7 Firmware Version Register (0x3FC)                      |          |

|    | 4.3 Correction Data Space                                      |          |

| 5  | I/O INTERFACE DESCRIPTION                                      | 66       |

|    | 5.1 Digital I/O Interface                                      | 66       |

|    | 5.2 Analog Output Interface                                    | 68       |

| 6  | DAC (RE-) CONFIGURATION                                        | 70       |

| 7  | DAC DATA CODING                                                | 71       |

| 8  | DAC DATA CORRECTION                                            | 73       |

| 9  | D/A OPERATING MODES                                            | 74       |

|    | 9.1 D/A Operating Modes Overview                               |          |

|    | 9.1.1 DAC Operating Modes                                      |          |

|    | 9.1.2 Sequencer Operating Modes                                |          |

|    | 9.2 D/A Manual Mode                                            | 75       |

|    | 9.2.1 Immediate Conversion Mode                                |          |

|    | 9.2.2 Controlled Conversion Mode                               |          |

|    | 9.3 D/A Sequencer Mode                                         |          |

|    | 9.3.1 Sequencer Overview                                       |          |

|    | 9.3.2 Host Memory Data Buffers                                 |          |

|    | 9.3.3 Sequencer DMA Operation                                  |          |

|    | 9.3.5 Sequencer Operating Modes                                |          |

|    | 9.3.6 Sequencer Normal Mode                                    |          |

|    | 9.3.6.1 Sequencer Normal Mode Description                      |          |

|    | 9.3.6.2 Sequencer Normal Mode Example                          |          |

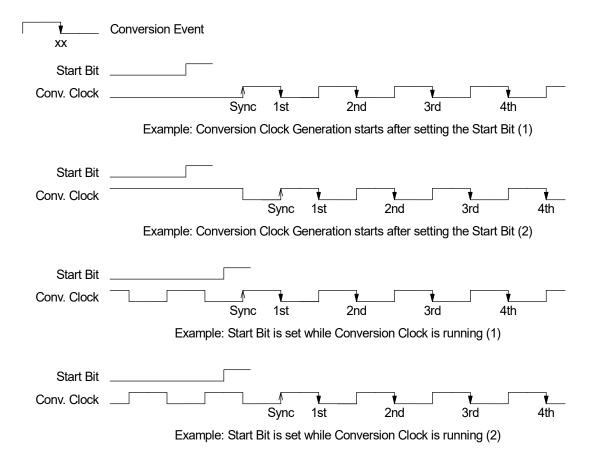

|    | 9.3.6.3 Sequencer Normal Mode Start Synchronization            |          |

|    | 9.3.7 Sequencer Frame Mode                                     |          |

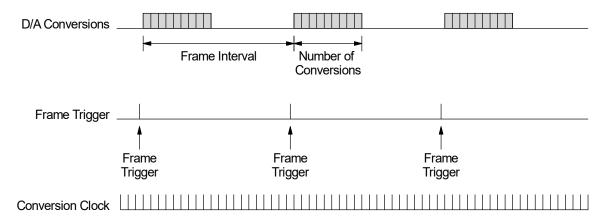

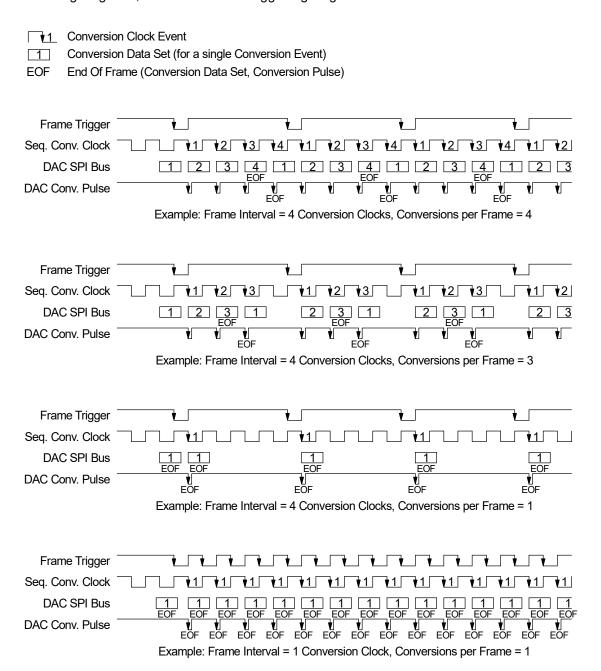

|    | 9.3.7.2 Sequencer Frame Mode Example Diagrams (D/A)            |          |

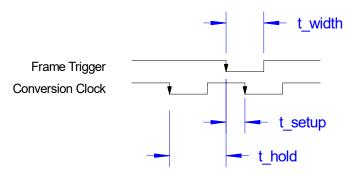

|    | 9.3.7.3 Sequencer Frame Mode Notes                             |          |

| 10 | CONVERSION CONTROL SIGNALS                                     |          |

|    | 10.1 Internal Conversion Control Signals                       | 90       |

|    | 10.2 Internal Signal Generators                                |          |

|    | 10.2.1 Conversion Clock Signal Generators                      |          |

|    | 10.2.2 Frame Trigger Signal Generator                          |          |

|    | 10.3 I/O Signals                                               |          |

|    | 10.4 Conversion Control Signal Block Diagram                   |          |

|    | 10.5 Multi-Board Synchronization                               |          |

| 11 | I/O PIN ASSIGNMENT                                             |          |

|    | 11.1 Front I/O Connector                                       |          |

|    | 11.2 P14 Rear I/O Connector                                    |          |

| 12 | PROGRAMMING HINTS                                              | 98       |

| 121  | ilobal DAC Status Register Read | 0.0 |

|------|---------------------------------|-----|

| 12.1 | IIODAI DAG SIAIUS REGISIEL REAU | 76  |

# **List of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                                                    | 10 |

|------------------------------------------------------------------------------|----|

| FIGURE 5-1: DIGITAL I/O LINE CIRCUIT                                         | 66 |

| FIGURE 9-1 : D/A SEQUENCER UNIT                                              | 76 |

| FIGURE 9-2: SEQUENCER NORMAL MODE DIAGRAM                                    | 80 |

| FIGURE 9-3: SEQUENCER NORMAL MODE START SYNCHRONIZATION                      | 85 |

| FIGURE 9-4: SEQUENCER FRAME MODE DIAGRAM                                     | 86 |

| FIGURE 9-5: FRAME MODE EXAMPLE DIAGRAMS (D/A)                                | 88 |

| FIGURE 9-6: FRAME TRIGGER TIMING REQUIREMENTS                                | 89 |

| FIGURE 9-7: SEQUENCER FRAME MODE 1ST CONVERSION EVENT                        | 89 |

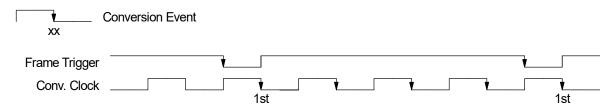

| FIGURE 10-1 : FRAME TRIGGER SIGNAL GEN. EXAMPLE (FRAME TRIGGER INTERVAL = 4) | 91 |

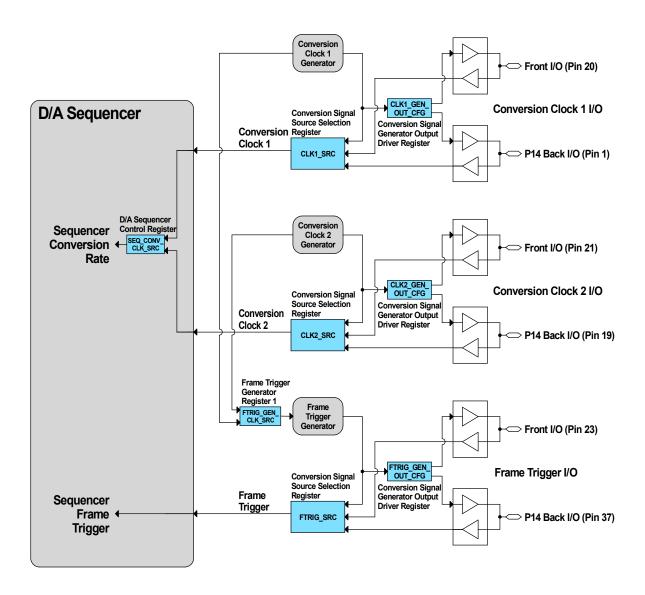

| FIGURE 10-2: CONVERSION CONTROL SIGNAL BLOCK DIAGRAM                         | 93 |

| List of Tables                                                               |    |

| TABLE 2-1: TECHNICAL SPECIFICATION                                           | 12 |

| TABLE 4-1: PCI IDENTIFIER                                                    | 14 |

| TABLE 4-2: PCI BASE ADDRESS REGISTER (BAR) CONFIGURATION                     | 14 |

| TABLE 4-3: REGISTER SPACE                                                    | 18 |

| TABLE 4-4: REGISTER BIT ACCESS TYPES                                         |    |

| TABLE 4-5: GLOBAL DAC CONTROL REGISTER (0X158)                               | 19 |

| TABLE 4-6: GLOBAL DAC STATUS REGISTER (0X15C)                                | 20 |

| TABLE 4-7: DAC CONFIGURATION REGISTER (0X168, 0X198, 0X1C8, 0X1F8)           | 22 |

| TABLE 4-8: DAC CORRECTION REGISTER A (0X170, 0X1A0, 0X1D0, 0X200)            | 23 |

| TABLE 4-9: DAC CORRECTION REGISTER B (0X174, 0X1A4, 0X1D4, 0X204)            | 23 |

| TABLE 4-10: DAC CORRECTION REGISTER C (0X178, 0X1A8, 0X1D8, 0X208)           | 23 |

| TABLE 4-11: DAC CORRECTION REGISTER D (0X17C, 0X1AC, 0X1DC, 0X20C)           | 23 |

| TABLE 4-12: DAC DATA REGISTER A & B (0X180, 0X1B0, 0X1E0, 0X210)             | 24 |

| TABLE 4-13: DAC DATA REGISTER C & D (0X184, 0X1B4, 0X1E4, 0X214)             | 24 |

| TABLE 4-14: DAC STATUS REGISTER (0X188, 0X1B8, 0X1E8, 0X218)                 | 26 |

| TABLE 4-15: DAC MODE REGISTER (0X18C, 0X1BC, 0X1EC, 0X21C)                   | 27 |

| TABLE 4-16: SEQUENCER CONTROL REGISTER (0X2E8)                               | 29 |

| TABLE 4-17: SEQUENCER STATUS REGISTER (0X2EC)                                | 31 |

| TABLE 4-18: NUMBER OF CONVERSIONS REGISTER (0X2F4)                           | 32 |

| TABLE 4-19: CONVERSION COUNT REGISTER (0X2F8)                                | 32 |

| TABLE 4-20: FIFO LEVEL REGISTER (0X2FC)                                      | 33 |

| TABLE 4-21: DMA BUFFER BASE ADDRESS REGISTER (0X308)                         | 33 |

| TABLE 4-22: DMA BUFFER LENGTH REGISTER (0X30C)                               | 33 |

| TABLE 4-23: DMA BUFFER NEXT ADDRESS REGISTER (0X310)                         | 33 |

| TABLE 4-24: CONVERSION CLOCK 1 GENERATOR REGISTER (0X320)                    | 34 |

| TABLE 4-25: CONVERSION CLOCK 2 GENERATOR REGISTER (0X324)              | 35 |

|------------------------------------------------------------------------|----|

| TABLE 4-26: FRAME TRIGGER GENERATOR REGISTER 1 (0X32C)                 | 35 |

| TABLE 4-27: FRAME TRIGGER GENERATOR REGISTER 2 (0X330)                 | 36 |

| TABLE 4-28: CONVERSION SIGNAL GENERATOR ENABLE REGISTER (0X33C)        | 36 |

| TABLE 4-29: CONVERSION SIGNAL GENERATOR OUTPUT DRIVER REGISTER (0X340) | 37 |

| TABLE 4-30: CONVERSION SIGNAL SOURCE SELECTION REGISTER (0X344)        | 38 |

| TABLE 4-31: CONVERSION SIGNAL PATH CONFIGURATION EXAMPLES              | 38 |

| TABLE 4-32: FRAME TIMER REGISTER (0X348)                               | 39 |

| TABLE 4-33: DIO INPUT REGISTER (0X354)                                 |    |

| TABLE 4-34: DIO INPUT FILTER REGISTER (0X358)                          | 41 |

| TABLE 4-35 : DIO OUTPUT REGISTER (0X35C)                               | 41 |

| TABLE 4-36: DIO OUTPUT ENABLE REGISTER (0X360)                         | 42 |

| TABLE 4-37: INTERRUPT ENABLE REGISTER (0X36C)                          | 43 |

| TABLE 4-38: ERROR INTERRUPT ENABLE REGISTER (0X370)                    | 44 |

| TABLE 4-39: DIO RISING EDGE INTERRUPT ENABLE REGISTER (0X374)          | 46 |

| TABLE 4-40: DIO FALLING EDGE INTERRUPT ENABLE REGISTER (0X378)         | 48 |

| TABLE 4-41: INTERRUPT STATUS REGISTER (0X384)                          | 49 |

| TABLE 4-42: ERROR INTERRUPT STATUS REGISTER (0X388)                    | 50 |

| TABLE 4-43: DIO INTERRUPT STATUS REGISTER (0X38C)                      | 51 |

| TABLE 4-44: GLOBAL CONFIGURATION REGISTER (0X398)                      | 52 |

| TABLE 4-45: DIO PULL REFERENCE REGISTER (0X39C)                        | 53 |

| TABLE 4-46: P14 I/O PULL REFERENCE REGISTER (0X3A0)                    | 53 |

| TABLE 4-47: CORRECTION DATA EEPROM CONTROL/STATUS REGISTER (0X3A4)     | 54 |

| TABLE 4-48: TEMPERATURE SENSOR TRIGGER REGISTER (0X3A8)                | 55 |

| TABLE 4-49: TEMPERATURE SENSOR DATA REGISTER (0X3AC)                   | 55 |

| TABLE 4-50: FIRMWARE VERSION REGISTER (0X3FC)                          | 55 |

| TABLE 4-51: CORRECTION DATA SPACE                                      |    |

| TABLE 5-1: DIO OUTPUT LEVEL CONFIGURATION                              |    |

| TABLE 7-1: DAC DATA CODING - UNIPOLAR VOLTAGE OUTPUT RANGE             | 71 |

| TABLE 7-2: DAC DATA CODING - BIPOLAR VOLTAGE OUTPUT RANGE              | 71 |

| TABLE 7-3: DAC DATA CODING - CURRENT OUTPUT RANGE                      | 72 |

| TABLE 9-1: HOST MEMORY DATA BUFFER EXAMPLE                             | 77 |

| TABLE 9-2: SIMPLE NORMAL MODE EXAMPLE: CONVERSION DATA PLAN            | 81 |

| TABLE 9-3: SIMPLE NORMAL MODE EXAMPLE: DATA IN HOST MEMORY             | 82 |

| TABLE 9-4: FRAME TRIGGER TIMING PARAMETER                              | 89 |

| TABLE 10-1: CONVERSION SIGNAL PATH CONFIGURATION EXAMPLES              |    |

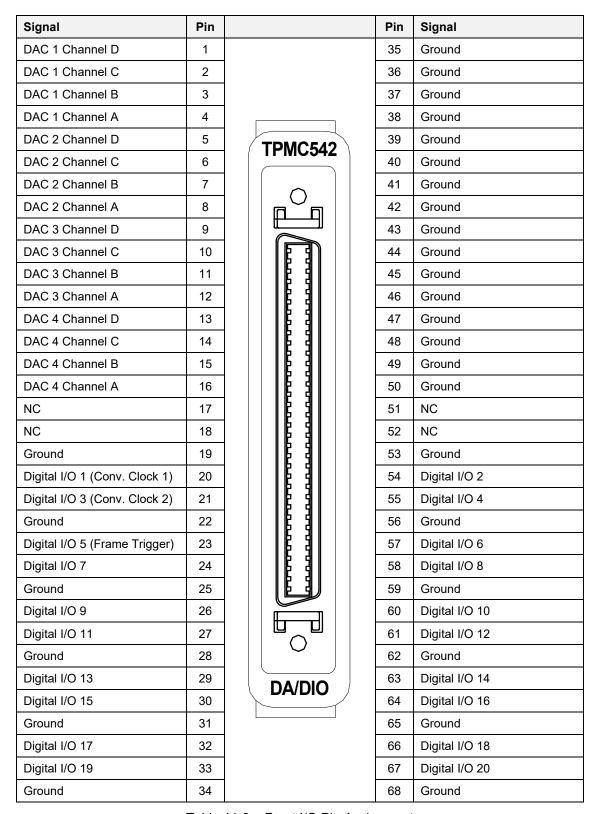

| TABLE 11-1: FRONT I/O CONNECTOR TYPE                                   | 95 |

| TABLE 11-2: FRONT I/O SIGNAL TYPES                                     | 95 |

| TABLE 11-3: FRONT I/O PIN ASSIGNMENT                                   | 96 |

| TABLE 11-4: P14 REAR I/O CONNECTOR TYPE                                | 97 |

| TARLE 11-5 · D1/LREAR I/O DIN ASSIGNMENT                               | 97 |

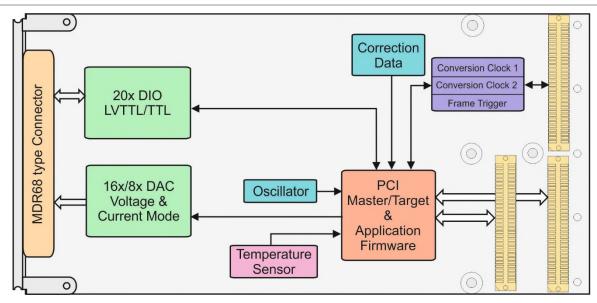

# 1 Product Description

The TPMC542 is a standard single-wide PCI Mezzanine Card (PMC) compatible module providing 16 or 8 channels of simultaneous update single-ended 16bit analog output and 20 channels of tristate capable 5V-tolerant LVTTL/TTL digital input/output.

A 32 bit 33 MHz PCI interface is provided at the PMC P11 and P12 connectors.

The analog output signals and digital I/O signals are accessible via a 68 pin Mini D Ribbon (MDR68) type front I/O connector.

For each individual D/A channel, the following output ranges are configurable:

- 0V to 5V Voltage Range

- 0V to 10V Voltage Range

- ±5V Voltage Range

- ±10V Voltage Range

- 4mA to 20mA Current Range

- 0mA to 20mA Current Range

- 0mA to 24mA Current Range

Additionally, a 20% over-range may be enabled for each Voltage Range.

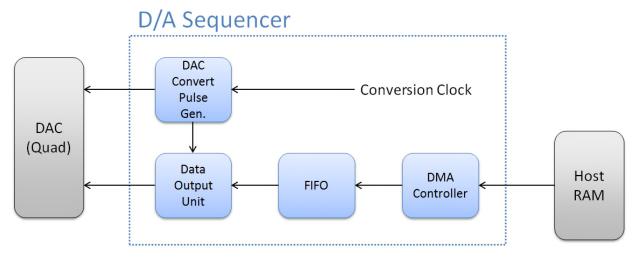

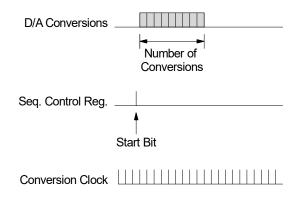

The TPMC542 provides a D/A Sequencer unit for periodic simultaneous digital to analog conversions at a configurable conversion rate. In sequencer mode, the D/A conversion data is fetched from buffers in host memory by PCI master DMA transfer and is temporarily stored in an on-board data buffer. The Sequencer provides a Frame Mode used for repetitive frames of simultaneous D/A conversions upon a frame trigger signal event.

Conversion clock (conversion rate) and frame trigger signals may be generated on-board for internal use and may also be driven out on P14 rear I/O if the card is operating as a master card in a Multi-Board configuration. The conversion clock (conversion rate) and frame trigger signals may also be sourced externally via the P14 rear I/O interface if the card is operating as a target card in a Multi-Board configuration.

Each TPMC542 is factory calibrated. The correction data is stored in an on-board serial EEPROM unique to each PMC module. These correction values may be used to perform a hardware correction for every D/A channel and output range.

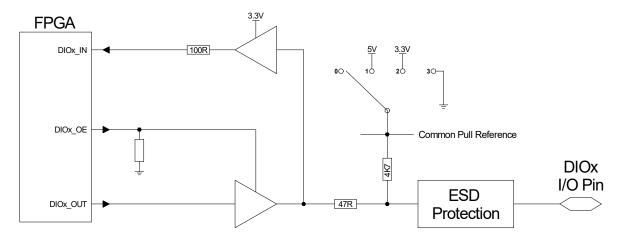

The digital I/O lines are ESD protected. Each digital I/O line has a dedicated line transmitter with individual output enable control and a dedicated line receiver. The line receivers are always enabled, so the digital I/O line level can always be monitored. Each digital I/O line input is capable of generating an interrupt triggered on rising edge, falling edge or both. Additionally, a debounce filter can be configured to get rid of bouncing on the digital I/O inputs. Each digital I/O line has a  $4.7 \text{k}\Omega$  pull resistor to a common reference. The common pull resistor reference is programmable by software (one setting for all digital I/O lines) to +3.3 V, +5 V or GND.

Figure 1-1: Block Diagram

# 2 <u>Technical Specification</u>

| PMC Interface                                         |                                                                                                                                                                                       |  |  |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PCI Mezzanine Card (PMC) Interface confirming to IEEE |                                                                                                                                                                                       |  |  |  |  |

| Mechanical Interface                                  | P1386/P1386.1                                                                                                                                                                         |  |  |  |  |

|                                                       | Standard single-wide                                                                                                                                                                  |  |  |  |  |

|                                                       | PCI Rev. 3.0 compatible                                                                                                                                                               |  |  |  |  |

| Electrical Interface                                  | 33MHz / 32bit PCI Initiator/Target                                                                                                                                                    |  |  |  |  |

|                                                       | 3.3V and 5V PCI Signaling Voltage compatible                                                                                                                                          |  |  |  |  |

| On-Board Devices                                      |                                                                                                                                                                                       |  |  |  |  |

| FPGA                                                  | XC6SLX25-2FTG256I (Xilinx)                                                                                                                                                            |  |  |  |  |

| DAC                                                   | AD5755-1ACPZ (Analog Devices)                                                                                                                                                         |  |  |  |  |

| Digital I/O                                           | 74LVT126PW (NXP)                                                                                                                                                                      |  |  |  |  |

| Non-Volatile Memory                                   |                                                                                                                                                                                       |  |  |  |  |

| FPGA Configuration Flash                              | 32 Mbit Serial Flash                                                                                                                                                                  |  |  |  |  |

| FFGA Configuration Flash                              | W25Q32FVZPIG (Winbond)                                                                                                                                                                |  |  |  |  |

| Correction Data EEPROM                                | 16 kbit Serial EEPROM                                                                                                                                                                 |  |  |  |  |

| Correction Data LLF NOW                               | M93C86-WMN6TP (ST)                                                                                                                                                                    |  |  |  |  |

| I/O Interface                                         |                                                                                                                                                                                       |  |  |  |  |

| D/A Channels                                          | TPMC542-10R: 16 D/A Channels                                                                                                                                                          |  |  |  |  |

| DIA GIIdillicis                                       | TPMC542-20R: 8 D/A Channels                                                                                                                                                           |  |  |  |  |

|                                                       | Voltage Mode Ranges:                                                                                                                                                                  |  |  |  |  |

|                                                       | 0V 5V, 0V 10V, -5V +5V, -10V +10V                                                                                                                                                     |  |  |  |  |

|                                                       | Voltage Ranges available with 20% Overrange Mode:                                                                                                                                     |  |  |  |  |

|                                                       | 0V 6V, 0V 12V, -6V +6V, -12V +12V                                                                                                                                                     |  |  |  |  |

|                                                       | Up to 10mA load current per D/A channel output D/A channel output slew rate 1.9V/us (typical)                                                                                         |  |  |  |  |

| D/A Channel Output                                    | Current Mode Ranges:                                                                                                                                                                  |  |  |  |  |

|                                                       | 4mA 20mA, 0mA 20mA, 0mA 24mA                                                                                                                                                          |  |  |  |  |

|                                                       | External load resistor range per channel: up to 1K (with increased                                                                                                                    |  |  |  |  |

|                                                       | power dissipation and cooling requirements), recommended                                                                                                                              |  |  |  |  |

|                                                       | maximum load resistor value: $680\Omega$ , recommended load resistor                                                                                                                  |  |  |  |  |

|                                                       | value: less than or equal to 390Ω                                                                                                                                                     |  |  |  |  |

| D/A Conversion Rate                                   | Max. 38ksps Conversion Rate (all D/A Channels simultaneous)                                                                                                                           |  |  |  |  |

|                                                       |                                                                                                                                                                                       |  |  |  |  |

|                                                       | 20 TTL/LVTTL Digital I/O Lines                                                                                                                                                        |  |  |  |  |

|                                                       | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable                                                                                                                           |  |  |  |  |

| Digital I/O Channels                                  | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable Control, Common Pull Resistor Reference Control (3.3V, 5V,                                                                |  |  |  |  |

| Digital I/O Channels                                  | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable                                                                                                                           |  |  |  |  |

| Digital I/O Channels                                  | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable Control, Common Pull Resistor Reference Control (3.3V, 5V, GND)                                                           |  |  |  |  |

| Digital I/O Channels  I/O Connectors                  | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable Control, Common Pull Resistor Reference Control (3.3V, 5V, GND)  Up to 15mA Source Current and up to 6mA Sink Current per |  |  |  |  |

|                                                       | 3.3V Driver, 5V tolerant Receiver, Individual Output Enable Control, Common Pull Resistor Reference Control (3.3V, 5V, GND)  Up to 15mA Source Current and up to 6mA Sink Current per |  |  |  |  |

| Physical Data      |                                                                                                                                                                                                                                                                                                                                                                                              |                                  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Power Requirements | Only the 5V PMC Power Supply is used Typically 0.25A @ +5V DC without I/O Load I/O Load Calculation: Add 0.010A per active DIO Output Line Add 0.070A per active D/A Voltage Output without Overrange Add 0.082A per active D/A Voltage Output with Overrange Add approx. (IRANGE_MAX <sup>2</sup> * REXT) / 2.25V ampere per active D/A Current Output                                      |                                  |  |  |

| Temperature Range  | Operating<br>Storage                                                                                                                                                                                                                                                                                                                                                                         | -40°C to +85°C<br>-40°C to +85°C |  |  |

| мтвғ               | TPMC542-10R: 283000h TPMC542-20R: 356000h MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C. The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |                                  |  |  |

| Humidity           | 5 – 95 % non-condensing                                                                                                                                                                                                                                                                                                                                                                      |                                  |  |  |

| Weight             | TPMC542-10R: 92g<br>TPMC542-20R: 84g                                                                                                                                                                                                                                                                                                                                                         |                                  |  |  |

Table 2-1: Technical Specification

# 3 Handling and Operation Instructions

## 3.1 ESD Protection

The PMC module is sensitive to static electricity. Packing, unpacking and all other module handling has to be done with the appropriate care.

# 3.2 Power Dissipation Limit

Please note that with multiple D/A channels operating in Current Mode, the PMC power consumption and dissipation may exceed the maximum values defined in IEEE Std. 1386-2001. This is largely depending on the resistance value of the external load resistors used for D/A channels in current mode. Although the DAC device supports external load resistor values of up to 1K Ohm in Current Mode, the value of the external load resistor should not exceed  $680\Omega$ . Load resistor values of less than (or equal to)  $390\Omega$  are recommended.

See also the *I/O Load Calculation* in the *Technical Specification* table. Normally the total current drawn from the PMC 5V power supply should not exceed 1.5A (7.5W).

# 3.3 Forced Air-Cooling Requirements

The TPMC542 requires forced air cooling.

Moderate air cooling is required when D/A channels are only used in Voltage Mode or when D/A channels are used in Current Mode with external load resistor values  $\leq 390\Omega$ .

Air cooling requirements increase with: Ambient Temperature, Number of Current Mode D/A Channels on the same DAC device, Resistance value of external Current Mode load resistors.

Firm air cooling is required when D/A channels are used in Current Mode with external load resistor values >  $390\Omega$ .

It is recommended to limit the number of D/A Current Mode channels with external resistor values >  $390\Omega$  and to spread these over the DAC devices (e.g. use D/A channels 1, 5, 9, 13).

# 4 PCI Interface

# 4.1 PCI Identifier & BAR Configuration

| Vendor-ID           | 0x1498 (TEWS TECHNOLOGIES)                                      |  |  |

|---------------------|-----------------------------------------------------------------|--|--|

| Device-ID           | 0x021E (TPMC542)                                                |  |  |

| Class Code          | 0x118000 (Other data acquisition/signal processing controllers) |  |  |

| Subsystem Vendor-ID | 0x1498 (TEWS TECHNOLOGIES)                                      |  |  |

| Subsystem Device-ID | 0x000A (TPMC542-10R)<br>0x0014 (TPMC542-20R)                    |  |  |

Table 4-1: PCI Identifier

The TPMC542 provides two spaces mapped in PCI Memory Space.

| PCI Base Address Register (Offset in PCI Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description           |

|---------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|-----------------------|

| 0 (0x10)                                                      | MEM                     | 1024           | 32                     | Little         | Register Space        |

| 1 (0x14)                                                      | MEM                     | 2048           | 32                     | Little         | Correction Data Space |

Table 4-2: PCI Base Address Register (BAR) Configuration

# 4.2 Register Space

PCI Base Address Register 0 (Offset 0x10 in PCI Configuration Space).

| Offset to BAR0 | Description                 | Size (Bit) |

|----------------|-----------------------------|------------|

| 0x000          |                             |            |

| •••            | Reserved                    | -          |

| 0x154          |                             |            |

|                | DAC Global Registers        |            |

| 0x158          | Global DAC Control Register | 32         |

| 0x15C          | Global DAC Status Register  | 32         |

| 0x160          | Reserved                    | -          |

| 0x164          | Reserved                    | -          |

|                | DAC Device Registers        |            |

| 0x168          | DAC1 Configuration Register | 32         |

| 0x16C          | DAC1 Reserved               | -          |

| 0x170          | DAC1 Correction Register A  | 32         |

| 0x174          | DAC1 Correction Register B  | 32         |

| 0x178          | DAC1 Correction Register C  | 32         |

| 0x17C          | DAC1 Correction Register D  | 32         |

| 0x180          | DAC1 Data Register A & B    | 32         |

| 0x184          | DAC1 Data Register C & D    | 32         |

| 0x188          | DAC1 Status Register        | 32         |

| 0x18C          | DAC1 Mode Register          | 32         |

| 0x190          | Reserved                    | -          |

| 0x194          | Reserved                    | -          |

| 0x198          | DAC2 Configuration Register | 32         |

| 0x19C          | DAC2 Reserved               | -          |

| 0x1A0          | DAC2 Correction Register A  | 32         |

| 0x1A4          | DAC2 Correction Register B  | 32         |

| 0x1A8          | DAC2 Correction Register C  | 32         |

| 0x1AC          | DAC2 Correction Register D  | 32         |

| 0x1B0          | DAC2 Data Register A & B    | 32         |

| 0x1B4          | DAC2 Data Register C & D    | 32         |

| 0x1B8          | DAC2 Status Register        | 32         |

| 0x1BC          | DAC2 Mode Register          | 32         |

| 0x1C0          | Reserved                    | -          |

| 0x1C4          | Reserved                    | -          |

| 0x1C8          | DAC3 Configuration Register | 32         |

| 0x1CC          | DAC3 Reserved               | -          |

| 0x1D0          | DAC3 Correction Register A  | 32         |

| Offset to BAR0               | Description                                    | Size (Bit) |  |  |  |

|------------------------------|------------------------------------------------|------------|--|--|--|

| 0x1D4                        | DAC3 Correction Register B                     | 32         |  |  |  |

| 0x1D8                        | DAC3 Correction Register C                     | 32         |  |  |  |

| 0x1DC                        | DAC3 Correction Register D                     | 32         |  |  |  |

| 0x1E0                        | DAC3 Data Register A & B                       | 32         |  |  |  |

| 0x1E4                        | DAC3 Data Register C & D                       | 32         |  |  |  |

| 0x1E8                        | DAC3 Status Register                           | 32         |  |  |  |

| 0x1EC                        | DAC3 Mode Register                             | 32         |  |  |  |

| 0x1F0                        | Reserved                                       | -          |  |  |  |

| 0x1F4                        | Reserved                                       | -          |  |  |  |

| 0x1F8                        | DAC4 Configuration Register                    | 32         |  |  |  |

| 0x1FC                        | DAC4 Reserved                                  | -          |  |  |  |

| 0x200                        | DAC4 Correction Register A                     | 32         |  |  |  |

| 0x204                        | DAC4 Correction Register B                     | 32         |  |  |  |

| 0x208                        | DAC4 Correction Register C                     | 32         |  |  |  |

| 0x20C                        | DAC4 Correction Register D                     | 32         |  |  |  |

| 0x210                        | DAC4 Data Register A & B                       | 32         |  |  |  |

| 0x214                        | DAC4 Data Register C & D                       | 32         |  |  |  |

| 0x218                        | DAC4 Status Register                           | 32         |  |  |  |

| 0x21C                        | DAC4 Mode Register                             | 32         |  |  |  |

| 0x220                        |                                                |            |  |  |  |

|                              | Reserved                                       | -          |  |  |  |

| 0x2E4                        | DAC Sequencer Registers                        |            |  |  |  |

| 0050                         | DAC Sequencer Registers                        | 20         |  |  |  |

| 0x2E8                        | D/A Sequencer Control Register                 | 32         |  |  |  |

| 0x2EC                        | D/A Sequencer Status Register                  | 32         |  |  |  |

| 0x2F0                        | Reserved                                       | -          |  |  |  |

| 0x2F4                        | D/A Sequencer Number of Conversions Register   | 32         |  |  |  |

| 0x2F8                        | D/A Sequencer Conversion Count Register        | 32         |  |  |  |

| 0x2FC                        | D/A Sequencer FIFO Level Register              | 32         |  |  |  |

| 0x300                        | Reserved                                       | -          |  |  |  |

| 0x304                        | Reserved                                       | -          |  |  |  |

| 0x308                        | D/A Sequencer DMA Buffer Base Address Register | 32         |  |  |  |

| 0x30C                        | D/A Sequencer DMA Buffer Length Register       | 32         |  |  |  |

| 0x310                        | D/A Sequencer DMA Buffer Next Address Register | 32         |  |  |  |

| 0x314                        | Reserved                                       | -          |  |  |  |

| 0x318                        | Reserved                                       | -          |  |  |  |

| 0x31C Reserved -             |                                                |            |  |  |  |

| Conversion Signals Registers |                                                |            |  |  |  |

| 0x320                        | Conversion Clock 1 Generator Register          | 32         |  |  |  |

| 0x324                        | Conversion Clock 2 Generator Register          | 32         |  |  |  |

| Offset to BAR0 | Description                                        | Size (Bit) |

|----------------|----------------------------------------------------|------------|

| 0x328          | Reserved                                           | -          |

| 0x32C          | Frame Trigger Generator Configuration Register 1   | 32         |

| 0x330          | Frame Trigger Generator Configuration Register 2   | 32         |

| 0x334          | Reserved                                           | -          |

| 0x338          | Reserved                                           | -          |

| 0x33C          | Conversion Signal Generator Enable Register        | 32         |

| 0x340          | Conversion Signal Generator Output Driver Register | 32         |

| 0x344          | Conversion Signal Source Selection Register        | 32         |

| 0x348          | Frame Timer Register                               | 32         |

| 0x34C          | Reserved                                           | -          |

| 0x350          | Reserved                                           | -          |

|                | DIO Registers                                      |            |

| 0x354          | DIO Input Register                                 | 32         |

| 0x358          | DIO Input Filter Register                          | 32         |

| 0x35C          | DIO Output Register                                | 32         |

| 0x360          | DIO Output Enable Register                         | 32         |

| 0x364          | Reserved                                           | -          |

| 0x368          | Reserved                                           | -          |

|                | Interrupt Registers                                |            |

| 0x36C          | Interrupt Enable Register                          | 32         |

| 0x370          | Error Interrupt Enable Register                    | 32         |

| 0x374          | DIO Rising Edge Interrupt Enable Register          | 32         |

| 0x378          | DIO Falling Edge Interrupt Enable Register         | 32         |

| 0x37C          | Reserved                                           | -          |

| 0x380          | Reserved                                           | -          |

| 0x384          | Interrupt Status Register                          | 32         |

| 0x388          | Error Interrupt Status Register                    | 32         |

| 0x38C          | DIO Interrupt Status Register                      | 32         |

| 0x390          | Reserved                                           | -          |

| 0x394          | Reserved                                           | -          |

|                | Other Registers                                    |            |

| 0x398          | Global Configuration Register                      | 32         |

| 0x39C          | DIO Pull Resistors Register                        | 32         |

| 0x3A0          | P14 Back I/O Pull Resistors Register               | 32         |

| 0x3A4          | Correction Data EEPROM Control/Status Register     | 32         |

| 0x3A8          | Temperature Sensor Trigger Register                | 32         |

| 0x3AC          | Temperature Sensor Data Register                   | 32         |

| 0x3B0          |                                                    |            |

|                | Reserved                                           | -          |

| 0x3F8          |                                                    |            |

| Offset to BAR0 | Description               | Size (Bit) |

|----------------|---------------------------|------------|

| 0x3FC          | Firmware Version Register | 32         |

Table 4-3: Register Space

For the TPMC542-20R the registers for DAC3 and DAC4 are reserved.

| Reg | ister Bit Access Type | Description                                                                                                   |

|-----|-----------------------|---------------------------------------------------------------------------------------------------------------|

| R   | Read                  | The bit is readable by software.                                                                              |

| R/W | Read/Write            | The bit is readable and writeable by software.                                                                |

| R/C | Read/Clear            | The bit is readable by software. The bit is set by the firmware. Software may clear the bit by writing a '1'. |

| R/S | Read/Set              | The bit is readable by software. Software may set this bit to '1'. The bit is cleared by the firmware.        |

Table 4-4: Register Bit Access Types

When reading reserved register bits, the value is undefined.

Reserved register bits shall be written as '0'.

# 4.2.1 D/A Global Registers

## 4.2.1.1 Global DAC Control Register (0x158)

This register provides control options for all on-board DAC devices.

| Bit   | Symbol                | Description                                                                                                                                                                                                                                                                                                                                                                                                             | Access | Reset<br>Value |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:20 | -                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                | -      | -              |

| 19    | DAC4_<br>RST_<br>REQ  | DAC4 Reset Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                            | R/S    | 0              |

| 18    | DAC3_<br>RST_<br>REQ  | DAC3 Reset Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                            | R/S    | 0              |

| 17    | DAC2_<br>RST_<br>REQ  | DAC2 Reset Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                            | R/S    | 0              |

| 16    | DAC1_<br>RST_<br>REQ  | DAC1 Reset Request When set, performs a DAC reset via the DAC (AD5755-1) RESET# pin. After the actual reset phase, a post-reset DAC auto-configuration is performed. This bit is automatically cleared. The DAC Busy Bit in the Global DAC Status Register indicates the active DAC reset and post-reset auto-configuration phase (also see chapter Programming Hints / Global DAC Status Register Read!).              | R/S    | 0              |

| 15:4  | -                     | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                | -      | -              |

| 3     | DAC4_<br>CONV_<br>REQ | DAC4 Conversion Pulse Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                 | R/S    | 0              |

| 2     | DAC3_<br>CONV_<br>REQ | DAC3 Conversion Pulse Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                 | R/S    | 0              |

| 1     | DAC2_<br>CONV_<br>REQ | DAC2 Conversion Pulse Request See description for DAC1.                                                                                                                                                                                                                                                                                                                                                                 | R/S    | 0              |

| 0     | DAC1_<br>CONV_<br>REQ | DAC1 Conversion Pulse Request Manual Controlled Conversion Mode: When set, generates a DAC conversion pulse. Software should check the DAC Busy Bit to be clear in the Global DAC Status Register before (also see chapter <i>Programming Hints / Global DAC Status Register Read!</i> ). This bit is automatically cleared. Sequencer Mode & Manual Immediate Mode: This bit has no effect and is cleared immediately. | R/S    | 0              |

Table 4-5: Global DAC Control Register (0x158)

## 4.2.1.2 Global DAC Status Register (0x15C)

This read only register provides status information for all on-board DAC devices.

| Bit   | Symbol         | Description                                                                                                                                                                                                                                         | Access | Reset<br>Value |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:20 | -              | Reserved                                                                                                                                                                                                                                            | -      | -              |

| 19    | DAC4_<br>FAULT | DAC4 Fault Status See description for DAC1.                                                                                                                                                                                                         | R      | 0              |

| 18    | DAC3_<br>FAULT | DAC3 Fault Status See description for DAC1.                                                                                                                                                                                                         | R      | 0              |

| 17    | DAC2_<br>FAULT | DAC2 Fault Status See description for DAC1.                                                                                                                                                                                                         | R      | 0              |

| 16    | DAC1_<br>FAULT | DAC1 Fault Status This bit is set when the DAC (AD5755-1) FAULT# output pin is active (low).                                                                                                                                                        | R      | 0              |

| 15:12 | -              | Reserved                                                                                                                                                                                                                                            | -      | -              |

| 11    | DAC4_SETL      | DAC4 Settle Status See description for DAC1.                                                                                                                                                                                                        | R      | -              |

| 10    | DAC3_SETL      | DAC3 Settle Status See description for DAC1.                                                                                                                                                                                                        | R      | -              |

| 9     | DAC2_SETL      | DAC2 Settle Status See description for DAC1.                                                                                                                                                                                                        | R      | -              |

| 8     | DAC1_SETL      | DAC1 Settle Status Indicates a fix 24us passing time after a DAC conversion.                                                                                                                                                                        | R      | -              |

| 7:4   | -              | Reserved                                                                                                                                                                                                                                            | -      | -              |

| 3     | DAC4_<br>BUSY  | DAC4 Busy Status See description for DAC1.                                                                                                                                                                                                          | R      | 0              |

| 2     | DAC3_<br>BUSY  | DAC3 Busy Status See description for DAC1.                                                                                                                                                                                                          | R      | 0              |

| 1     | DAC2_<br>BUSY  | DAC2 Busy Status See description for DAC1.                                                                                                                                                                                                          | R      | 0              |

| 0     | DAC1_<br>BUSY  | DAC1 Busy Status  Set when:  • a DAC transfer request is being processed (including any required recovery times)  • A DAC reset request is processed (including postreset auto-configuration time)  Does not cover any analog output settling time. | R      | 0              |

Table 4-6: Global DAC Status Register (0x15C)

Also see chapter Programming Hints / Global DAC Status Register Read!

### 4.2.2 D/A Device Registers

The registers described in this section are provided per on-board DAC device.

#### 4.2.2.1 DAC Configuration Register(s) (0x168, 0x198, 0x1C8, 0x1F8)

This register is intended for initial DAC configuration.

Each DAC device must be configured before use.

DAC configuration should be performed while the DAC is configured for Manual Mode.

After writing the DAC Configuration Register, the DAC Busy Bit in the Global DAC Status Register should be monitored to become clear again. Also see chapter Programming Hints / Global DAC Status Register Read!

This register is available per DAC device.

A write to the DAC configuration register logs an internal request for writing the configuration data to the corresponding DAC device (via the DAC serial interface) as soon as possible. If not already set, the DAC Busy bit in the Global DAC Status Register is set and remains so, until the configuration data transfer to the DAC device is done.

This register may be accessed with 32 bit, 16 bit or 8 bit transfer size.

| Bit   | Symbol | Description                                                            | Access | Reset<br>Value |

|-------|--------|------------------------------------------------------------------------|--------|----------------|

|       |        | DAC Channel D                                                          |        |                |

| 31    | -      | Reserved                                                               | -      | -              |

| 30    | OE_D   | Output Enable DAC Channel D                                            | R/W    | 0              |

| 29    | PU_D   | Power-Up DAC Channel D                                                 | R/W    | 0              |

| 28    | OVR_D  | Over Range DAC Channel D Enables 20% over-range for Voltage Ranges.    | R/W    | 0              |

| 27:24 | OR_D   | Output Range DAC Channel D See description for DAC Channel A.          | R/W    | 0              |

|       |        | DAC Channel C                                                          |        |                |

| 23    | -      | Reserved                                                               | -      | -              |

| 22    | OE_C   | Power-Up DAC Channel C                                                 | R/W    | 0              |

| 21    | PU_C   | Output Enable DAC Channel C                                            | R/W    | 0              |

| 20    | OVR_C  | Over Range DAC Channel C<br>Enables 20% over-range for Voltage Ranges. | R/W    | 0              |

| 19:16 | OR_C   | Output Range DAC Channel C<br>See description for DAC Channel A.       | R/W    | 0              |

|       |        | DAC Channel B                                                          |        |                |

| 15    | ı      | Reserved                                                               | -      | -              |

| 14    | OE_B   | Power-Up DAC Channel B                                                 | R/W    | 0              |

| 13    | PU_B   | Output Enable DAC Channel B                                            | R/W    | 0              |

| 12    | OVR_B  | Over Range DAC Channel B<br>Enables 20% over-range for Voltage Ranges. | R/W    | 0              |

| Bit  | Symbol | Desc                                                                               | cription                                                                                                                                                                           | Access | Reset<br>Value |

|------|--------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 11:8 | OR_B   | Output Range DAC Channel<br>See description for DAC Cha                            |                                                                                                                                                                                    | R/W    | 0              |

|      |        |                                                                                    |                                                                                                                                                                                    |        |                |

| 7    | -      | Reserved                                                                           |                                                                                                                                                                                    | -      | -              |

| 6    | OE_A   | Output Enable DAC Channel                                                          | Α                                                                                                                                                                                  | R/W    | 0              |

| 5    | PU_A   | Power-Up DAC Channel A                                                             |                                                                                                                                                                                    | R/W    | 0              |

| 4    | OVR_A  | Over Range DAC Channel A Enables 20% over-range for                                |                                                                                                                                                                                    | R/W    | 0              |

| 3:0  | OR_A   | 0000 0V to 0001 0V to 0010 0011 ±5 0100 ±10 0101 011x 10xx 1100 4mA to 1101 0mA to | A but Voltage Range 5V Voltage Range 10V Voltage Range Reserved V Voltage Range V Voltage Range Reserved Reserved Reserved Reserved 20mA Current Range 24mA Current Range Reserved | R/W    | 0              |

Table 4-7: DAC Configuration Register (0x168, 0x198, 0x1C8, 0x1F8)

Also see the DAC (Re-) Configuration chapter.

#### 4.2.2.2 DAC Correction Registers (0x170, 0x174, 0x178, 0x17C, 0x1A0, ...)

These registers are intended for performing a DAC correction.

If used, the DAC correction registers should be configured while the DAC is operating in Manual Mode.

Leaving the DAC Correction Registers unmodified at their Reset Value effectively disables DAC Correction.

These registers are available per DAC device. There is a register for each DAC channel.

To enable data correction for a D/A channel, the offset and gain correction values for the specific DAC device, DAC channel and Output Range must be read from the Correction Data Space at PCI Base Address Register 1 (BAR1) and written to the corresponding DAC Correction Register.

To disable data correction for a D/A channel, the corresponding DAC Correction Registers must be set to all 0.

These registers may be accessed with 32 bit or 16 bit transfer size.

| Bit   | Symbol | Description                           | Access | Reset<br>Value |

|-------|--------|---------------------------------------|--------|----------------|

| 31:16 | GAIN_A | Gain Correction Value D/A Channel A   | R/W    | 0x0000         |

| 15:0  | OFFS_A | Offset Correction Value D/A Channel A | R/W    | 0x0000         |

Table 4-8: DAC Correction Register A (0x170, 0x1A0, 0x1D0, 0x200)

| Bit   | Symbol | Description                           | Access | Reset<br>Value |

|-------|--------|---------------------------------------|--------|----------------|

| 31:16 | GAIN_B | Gain Correction Value D/A Channel B   | R/W    | 0x0000         |

| 15:0  | OFFS_B | Offset Correction Value D/A Channel B | R/W    | 0x0000         |

Table 4-9: DAC Correction Register B (0x174, 0x1A4, 0x1D4, 0x204)

| Bit   | Symbol | Description                           | Access | Reset<br>Value |

|-------|--------|---------------------------------------|--------|----------------|

| 31:16 | GAIN_C | Gain Correction Value D/A Channel C   | R/W    | 0x0000         |

| 15:0  | OFFS_C | Offset Correction Value D/A Channel C | R/W    | 0x0000         |

Table 4-10: DAC Correction Register C (0x178, 0x1A8, 0x1D8, 0x208)

| Bit   | Symbol | Description                           | Access | Reset<br>Value |

|-------|--------|---------------------------------------|--------|----------------|

| 31:16 | GAIN_D | Gain Correction Value D/A Channel D   | R/W    | 0x0000         |

| 15:0  | OFFS_D | Offset Correction Value D/A Channel D | R/W    | 0x0000         |

Table 4-11: DAC Correction Register D (0x17C, 0x1AC, 0x1DC, 0x20C)

Also see the DAC Data Correction chapter.

#### 4.2.2.3 DAC Data Registers (0x180, 0x184, 0x1B0, 0x1B4, ...)

These registers are available per DAC device.

These registers are intended to be used for DACs operating in manual mode (not for DACs operating in sequencer mode).

A write to a DAC data register logs an internal request for transferring the conversion data (via the DAC serial interface) to the corresponding DAC device and D/A channel as soon as possible. If not already set, the DAC Busy bit in the Global DAC Status Register is set and remains so, until the data transfer to the DAC device is done.

These registers may be accessed with 32 bit or 16 bit transfer size.

| Bit   | Symbol | Description                    | Access | Reset<br>Value |

|-------|--------|--------------------------------|--------|----------------|

| 31:16 | DATA_B | Digital Data for DAC Channel B | R/W    | 0x0000         |

| 15:0  | DATA_A | Digital Data for DAC Channel A | R/W    | 0x0000         |

Table 4-12: DAC Data Register A & B (0x180, 0x1B0, 0x1E0, 0x210)

| Bit   | Symbol | Description                    | Access | Reset<br>Value |

|-------|--------|--------------------------------|--------|----------------|

| 31:16 | DATA_D | Digital Data for DAC Channel D | R/W    | 0x0000         |

| 15:0  | DATA_C | Digital Data for DAC Channel C | R/W    | 0x0000         |

Table 4-13: DAC Data Register C & D (0x184, 0x1B4, 0x1E4, 0x214)

Also see the DAC Data Coding chapter.

Also see the D/A Manual Mode Conversions chapter.

#### 4.2.2.4 DAC Status Register(s) (0x188, 0x1B8, 0x1E8, 0x218)

This register is available per DAC device.

Each AD5755-1 DAC device provides an internal status register accessible via the DAC serial interface.

Setting the STAT\_REQ bit logs an internal request for reading the actual status from the corresponding DAC device (via the DAC serial interface) as soon as possible. If not already set, the DAC Busy bit in the Global DAC Status Register is set and remains so, until the status read transfer from the DAC device is done.

| Bit   | Symbol        | Description                                                                                                                                                                                                                                                                                                                                          | Access | Reset<br>Value |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31    | STAT_<br>REQ  | Status Read Request When set, clears the Status Valid bit and logs a request for updating the DAC Status Register with current status information from the DAC device. This bit clears immediately. This is the recommended DAC Status Read Mode for DACs operating in Manual Mode.                                                                  | R/S    | 0              |

| 30    | STAT_<br>VAL  | Status Valid 0: Stale Status Information 1: Updated Status Information The bit is set, when the DAC Status Register has been updated with actual status data from the DAC device. The bit is cleared upon logging a Status Read Request. The bit may also be cleared by writing a '1'.                                                               | R/C    | 0              |

| 29    | -             | Reserved                                                                                                                                                                                                                                                                                                                                             | -      | -              |