## The Embedded I/O Company

# **TPMC553**

## 32 / 16 Channels of 16 bit D/A

Version 1.0

### **User Manual**

Issue 1.0.3

December 2010

e-mail: info@tews.com www.tews.com

#### TPMC553-10

32 Channels of 16 bit D/A

#### TPMC553-11

16 Channels of 16 bit D/A

This document contains information, which is proprietary to TEWS TECHNOLOGIES GmbH. Any reproduction without written permission is forbidden.

TEWS TECHNOLOGIES GmbH has made any effort to ensure that this manual is accurate and complete. However TEWS TECHNOLOGIES GmbH reserves the right to change the product described in this document at any time without notice.

TEWS TECHNOLOGIES GmbH is not liable for any damage arising out of the application or use of the device described herein.

#### **Style Conventions**

Hexadecimal characters are specified with prefix 0x, i.e. 0x029E (that means hexadecimal value 029E).

For signals on hardware products, an ,Active Low' is represented by the signal name with # following, i.e. IP\_RESET#.

Access terms are described as:

W Write Only

R Read Only

R/W Read/Write

R/C Read/Clear

R/S Read/Set

©2008-2010 by TEWS TECHNOLOGIES GmbH

All trademarks mentioned are property of their respective owners.

| Issue | Description                                                                                           | Date           |

|-------|-------------------------------------------------------------------------------------------------------|----------------|

| 1.0   | Initial Issue                                                                                         | September 2008 |

| 1.1   | Revised DAC correction section                                                                        | October 2008   |

| 1.0.2 | New Notation for User Manual and Engineering Documentation                                            | March 2009     |

| 1.0.3 | (1) Front I/O Pin Assignment: Pins 67, 68 are not connected (2) DAC Correction Figures added/modified | December 2010  |

## **Table of Contents**

| 1 | PRODUCT DESCRIPTION                                            | 6  |

|---|----------------------------------------------------------------|----|

| 2 | TECHNICAL SPECIFICATION                                        | 7  |

| 3 | GENERAL NOTES ON THE TPMC553 QUAD-DACS                         | 8  |

| 4 | PCI9030 TARGET CHIP                                            | 10 |

|   | 4.1 PCI Configuration Registers (PCR)                          |    |

|   | 4.1.1 PCI9030 Header                                           |    |

|   | 4.2 Local Configuration Register (LCR)                         |    |

|   | 4.3 Configuration EEPROM                                       | 12 |

|   | 4.4 Local Software Reset                                       | 13 |

| 5 | LOCAL SPACE ADDRESSING                                         | 14 |

|   | 5.1 PCI9030 Local Space Configuration                          | 14 |

|   | 5.2 Register Space                                             | 14 |

|   | 5.2.1 Q-DAC X Configuration Register (X = 1-8) (Offset 0x00)   |    |

|   | 5.2.2 Q-DAC X Control Register (X = 1-8) (Offset 0x20)         | 18 |

|   | 5.2.3 Q-DAC X Status Register (X = 1-8) (Offset 0x40)          |    |

|   | 5.2.4 Q-DAC X Sequencer Timer Register (X = 1-8) (Offset 0x60) |    |

|   | 5.2.5 Clear Register (Offset 0x80)                             |    |

|   | 5.2.6 Load Register (M-Mode) (Offset 0x84)                     |    |

|   | 5.2.7 Global Control Register (Offset 0x88)                    |    |

|   | 5.2.9 Interrupt Status Register (Offset 0x90)                  |    |

|   | 5.2.10 Auto Status Timer Register (Offset 0x94)                |    |

|   | 5.3 DAC Data Space                                             |    |

|   | 5.4 DAC Calibration Data Space                                 |    |

| 6 | FUNCTIONAL DESCRIPTION                                         | 32 |

|   | 6.1 Q-DAC Configuration                                        | 32 |

|   | 6.2 Q-DAC Modes                                                |    |

|   | 6.2.1 I-Mode (Instant Mode)                                    |    |

|   | 6.2.2 M-Mode (Manual Mode)                                     |    |

|   | 6.2.3 T-Mode (Timer / Sequencer Mode)                          |    |

|   | 6.3 Q-DAC Status                                               | 36 |

|   | 6.3.1 Manual Status Read                                       |    |

|   | 6.3.2 Automatic Status Read                                    | 37 |

| 7 | PROGRAMMING HINTS                                              | 38 |

|   | 7.1 DAC Output Coding                                          | 38 |

|   | 7.2 DAC Data Correction                                        | 38 |

|   | 7.2.1 DAC Correction Formula                                   |    |

|   | 7.2.2 DAC Correction Values Background                         | 39 |

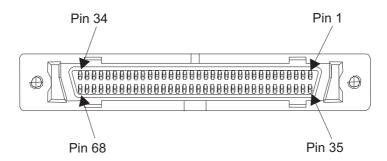

| 8 | PIN ASSIGNMENT – I/O CONNECTOR                                 | 44 |

|   | 8.1 Front I/O Connector                                        | 44 |

|   | 8.2 Pin Assignment                                             | 44 |

# **List of Figures**

| FIGURE 1-1: BLOCK DIAGRAM                               | 6              |

|---------------------------------------------------------|----------------|

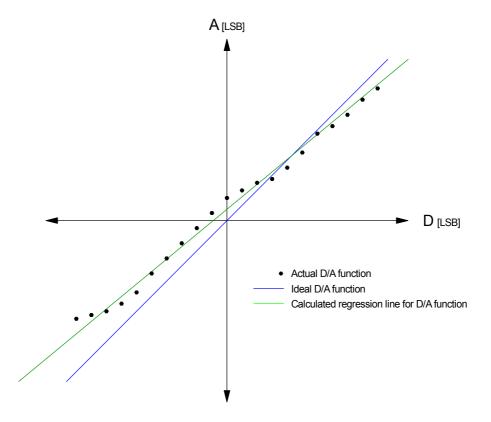

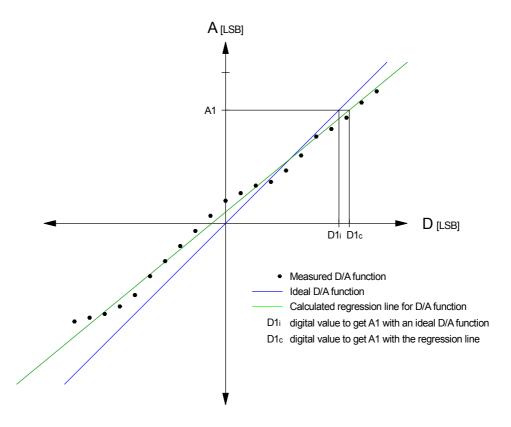

| FIGURE 7-1: REGRESSION LINE                             | 40             |

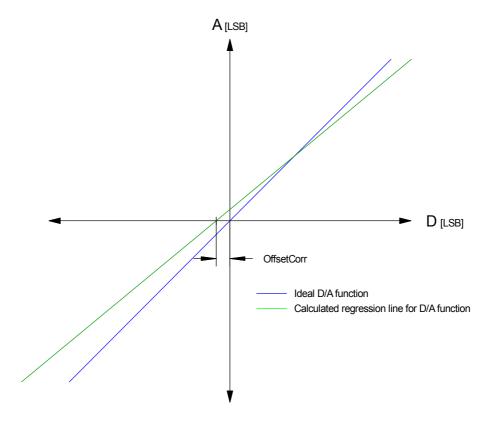

| FIGURE 7-2: OFFSET CORRECTION VALUE                     | 4′             |

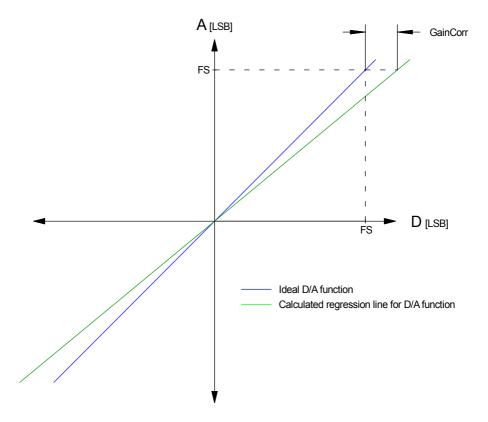

| FIGURE 7-3: GAIN CORRECTION VALUE                       | 42             |

| FIGURE 7-4: DAC DATA CORRECTION                         | 43             |

| FIGURE 8-2: I/O FRONT CONNECTOR VIEW                    | 44             |

| List of Tables                                          |                |

| TABLE 2-1: TECHNICAL SPECIFICATION                      |                |

| TABLE 3-1: D/A CHANNEL TO Q-DAC MAPPING                 |                |

| TABLE 4-1: PCI9030 HEADER                               | 10             |

| TABLE 4-2: PCI9030 LOCAL CONFIGURATION REGISTERS        |                |

| TABLE 4-3: CONFIGURATION EEPROM TPMC553-1X              | 12             |

| TABLE 5-1: PCI9030 LOCAL SPACE CONFIGURATION            | 14             |

| TABLE 5-2: REGISTER SPACE ADDRESS MAP                   | 15             |

| TABLE 5-3: Q-DAC CONFIGURATION REGISTER (OFFSET 0X00)   | 17             |

| TABLE 5-4: Q-DAC CONTROL REGISTER (OFFSET 0X20)         | 19             |

| TABLE 5-5: Q-DAC STATUS REGISTER (OFFSET 0X40)          | 20             |

| TABLE 5-6: Q-DAC SEQUENCER TIMER REGISTER (OFFSET 0X60) |                |

| TABLE 5-7: CLEAR REGISTER (OFFSET 0X80)                 | 2 <sup>2</sup> |

| TABLE 5-8: LOAD REGISTER (M-MODE) (OFFSET 0X84)         | 22             |

| TABLE 5-9: GLOBAL CONTROL REGISTER (OFFSET 0X88)        | 23             |

| TABLE 5-10: GLOBAL STATUS REGISTER (OFFSET 0X8C)        | 25             |

| TABLE 5-11: INTERRUPT STATUS REGISTER (OFFSET 0X90)     | 26             |

| TABLE 5-12: AUTO STATUS TIMER REGISTER (OFFSET 0X94)    | 27             |

| TABLE 5-13: DAC DATA SPACE ADDRESS MAP                  | 29             |

| TABLE 5-14: DAC CALIBRATION DATA SPACE ADDRESS MAP      | 3 <sup>2</sup> |

| TABLE 7-1: DAC OUTPUT CODING, BIPOLAR OUTPUT RANGE      | 38             |

| TABLE 7-2: DAC OUTPUT CODING, UNIPOLAR OUTPUT RANGE     | 38             |

| TABLE 8-1: I/O FRONT CONNECTOR TYPE                     | 44             |

TABLE 8-2: I/O PIN ASSIGNMENT .......45

## 1 Product Description

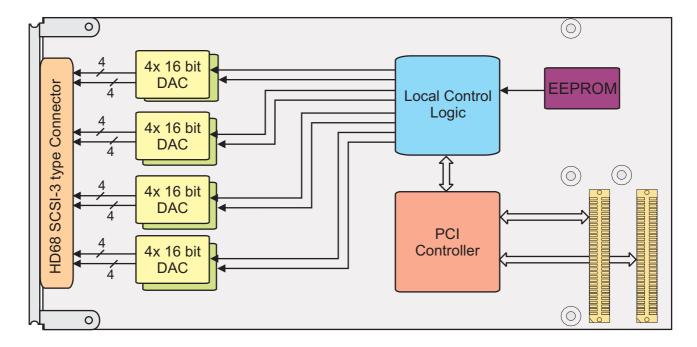

The TPMC553 is a standard single-wide 32 bit PMC module and provides 32/16 channels of 16 bit analog outputs. All signals are accessible through a HD68 SCSI-3 type front I/O connector.

The software selectable output voltage ranges are 0-5V, 0-10V, 0-10.8V,  $\pm$ 5V,  $\pm$ 10V or  $\pm$ 10.8V. The output voltage range can be individually set per channel. The conversion time is typ. 10  $\mu$ s and the DAC outputs are capable to drive a load of  $2k\Omega$ , with a capacitance up to 4000pF.

Beside of an individual channel update, the double buffered DACs allow simultaneous update of all channels. Additionally a sequencer on the TPMC553 allows to periodically updating enabled channels with a sequence timer range that extends from 10µs to 167s.

Each TPMC553 is factory calibrated. The calibration information is stored in an on board serial EEPROM unique to each PMC module.

Figure 1-1: Block Diagram

# 2 Technical Specification

| PMC Interface             |                                                                                                                                                                                                                |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Mechanical Interface      | PCI Mezzanine Card (PMC) Interface confirming to IEEE P1386/P1386.1                                                                                                                                            |  |  |  |  |  |

|                           | Single Size                                                                                                                                                                                                    |  |  |  |  |  |

| Electrical Interface      | PCI Rev. 2.2 compliant                                                                                                                                                                                         |  |  |  |  |  |

|                           | 33 MHz / 32 bit PCI                                                                                                                                                                                            |  |  |  |  |  |

|                           | 3.3V and 5V PCI Signaling Voltage                                                                                                                                                                              |  |  |  |  |  |

| On Board Devices          |                                                                                                                                                                                                                |  |  |  |  |  |

| PCI Target Chip           | PCI9030 (PLX Technology)                                                                                                                                                                                       |  |  |  |  |  |

| Quad-DAC                  | AD5754R (Analog Devices)                                                                                                                                                                                       |  |  |  |  |  |

| I/O Interface             |                                                                                                                                                                                                                |  |  |  |  |  |

| Number of D/A Channels    | TPMC553-10: 32 D/A channels<br>TPMC553-11: 16 D/A channels                                                                                                                                                     |  |  |  |  |  |

| D/A Resolution            | 16 bit                                                                                                                                                                                                         |  |  |  |  |  |

| D/A Output Voltage Range  | Selectable: 0V - +5V, 0V - +10V, 0V - +10.8V, ±5V, ±10V, ±10.8V                                                                                                                                                |  |  |  |  |  |

| D/A Channel Load          | Max 2kΩ   4000pF per D/A channel                                                                                                                                                                               |  |  |  |  |  |

| D/A Channel Settling Time | Max 10us                                                                                                                                                                                                       |  |  |  |  |  |

| D/A Protection            | 20mA current limit option, thermal shutdown option                                                                                                                                                             |  |  |  |  |  |

| D/A Calibration           | Calibration data for gain and offset correction                                                                                                                                                                |  |  |  |  |  |

| DAC INL/DNL Error         | ±16/±1 LSB                                                                                                                                                                                                     |  |  |  |  |  |

| I/O Connector             | Front I/O HD68 / SCSI-3 (AMP 5-787082-7 or compatible)                                                                                                                                                         |  |  |  |  |  |

| Physical Data             |                                                                                                                                                                                                                |  |  |  |  |  |

| Power Requirements        | 200mA typical @ 3.3V                                                                                                                                                                                           |  |  |  |  |  |

|                           | 600mA typical @ 5V (±10V output, 2kΩ load)                                                                                                                                                                     |  |  |  |  |  |

| Temperature Range         | Operating -40°C - +85°C                                                                                                                                                                                        |  |  |  |  |  |

|                           | Storage -40°C - +85°C                                                                                                                                                                                          |  |  |  |  |  |

| MTBF                      | TPMC553-10: 683000 h                                                                                                                                                                                           |  |  |  |  |  |

|                           | TPMC553-11: 689000 h                                                                                                                                                                                           |  |  |  |  |  |

|                           | MTBF values shown are based on calculation according to MIL-HDBK-217F and MIL-HDBK-217F Notice 2; Environment: G <sub>B</sub> 20°C.                                                                            |  |  |  |  |  |

|                           | The MTBF calculation is based on component FIT rates provided by the component suppliers. If FIT rates are not available, MIL-HDBK-217F and MIL-HDBK-217F Notice 2 formulas are used for FIT rate calculation. |  |  |  |  |  |

| Humidity                  | 5 – 95 % non-condensing                                                                                                                                                                                        |  |  |  |  |  |

| Weight                    | 79 g                                                                                                                                                                                                           |  |  |  |  |  |

Table 2-1: Technical Specification

## 3 General Notes on the TPMC553 Quad-DACs

The TPMC553 is using Quad-DAC (Q-DAC) devices. Each Q-DAC device provides four D/A channels, internally called A, B, C and D.

The TPMC553-10 provides 32 D/A channels (1 to 32), thus eight Q-DAC devices (1 to 8). The TPMC553-11 provides 16 D/A channels (1 to 16), thus four Q-DAC devices (1 to 4).

The Q-DAC device provides an internal data register for each of the four D/A channels.

To set a certain analog output voltage, the D/A channel data is written to a DAC Data Space, from where it is transferred to the appropriate Q-DAC internal D/A channel data register automatically as soon as possible. The Q-DAC analog outputs are then updated, depending on the Q-DAC operating mode used.

Each Q-DAC devices provides a single serial interface, so all transfers to the Q-DACs are in fact serial data transfers. A data transfer to a Q-DAC takes approx. 1.4us per D/A channel, data transfer for all four Q-DAC D/A channels takes approx. 5.6us. A Q-DAC status read takes approx. 3.4us.

The Q-DAC data transfer engines (parallel/serial) are independent of each other (e.g. data for D/A channels 1, 2, 3 & 4 is transferred one channel after the other since these channels are located in the same Q-DAC, while data for D/A channels 1, 5, 9, 13 could be transferred all at the same time since these channels are located in different Q-DACs.

| TPMC553 D/A Channel | Q-DAC | Q-DAC internal<br>D/A Channel |

|---------------------|-------|-------------------------------|

| 1                   |       | A                             |

| 2                   | 1     | В                             |

| 3                   | '     | С                             |

| 4                   |       | D                             |

| 5                   |       | A                             |

| 6                   | 2     | В                             |

| 7                   |       | С                             |

| 8                   |       | D                             |

| 9                   |       | A                             |

| 10                  | 3     | В                             |

| 11                  |       | С                             |

| 12                  |       | D                             |

| 13                  |       | A                             |

| 14                  | 4     | В                             |

| 15                  | _     | С                             |

| 16                  |       | D                             |

| 17                  |       | A                             |

| 18                  | 3     | В                             |

| 19                  |       | С                             |

| 20                  |       | D                             |

| 21                  |       | A                             |

| 22                  | 6     | В                             |

| 23                  |       | С                             |

| 24                  |       | D                             |

| TPMC553 D/A Channel | Q-DAC | Q-DAC internal<br>D/A Channel |

|---------------------|-------|-------------------------------|

| 25                  |       | А                             |

| 26                  | 7     | В                             |

| 27                  | ,     | С                             |

| 28                  |       | D                             |

| 29                  |       | А                             |

| 30                  | 8     | В                             |

| 31                  | O     | С                             |

| 32                  |       | D                             |

Table 3-1: D/A Channel to Q-DAC mapping

# 4 PCI9030 Target Chip

## 4.1 PCI Configuration Registers (PCR)

### 4.1.1 PCI9030 Header

| PCI CFG<br>Register | Write '0' to all u                   | PCI<br>writeable    | Initial Values<br>(Hex Values) |                    |          |             |

|---------------------|--------------------------------------|---------------------|--------------------------------|--------------------|----------|-------------|

| Address             | 31 24                                | 23 16               | 15 8                           | 7 0                |          |             |

| 0x00                | Devi                                 | ce ID               | Vend                           | dor ID             | N        | 0229 1498   |

| 0x04                | Sta                                  | itus                | Com                            | mand               | Υ        | 0280 0000   |

| 0x08                |                                      | Class Code          |                                | Revision ID        | N        | 118000 00   |

| 0x0C                | BIST                                 | Header Type         | PCI Latency<br>Timer           | Cache Line<br>Size | Y[7:0]   | 00 00 00 00 |

| 0x10                | PCI Base                             | Address 0 for ME    | M Mapped Config                | Registers          | Y        | FFFFFF80    |

| 0x14                | PCI Base                             | e Address 1 for I/C | Mapped Config.                 | Registers          | Y        | FFFFFF81    |

| 0x18                | PCI E                                | Base Address 2 for  | Local Address Sp               | ace 0              | Υ        | FFFFE00     |

| 0x1C                | PCI E                                | Base Address 3 for  | Local Address Sp               | ace 1              | Υ        | FFFFFC0     |

| 0x20                | PCI E                                | Base Address 4 for  | Local Address Sp               | ace 2              | Υ        | FFFFFC00    |

| 0x24                | PCI E                                | Base Address 5 for  | Local Address Sp               | ace 3              | Y        | 00000000    |

| 0x28                | PC                                   | l CardBus Informa   | ation Structure Poi            | nter               | N        | 00000000    |

| 0x2C                | Subsys                               | stem ID             | Subsysten                      | Nendor ID          | N        | s.b. 1498   |

| 0x30                | PCI                                  | Base Address for    | Local Expansion I              | ROM                | Υ        | 00000000    |

| 0x34                |                                      | Reserved            |                                | New Cap. Ptr.      | N        | 000000 40   |

| 0x38                |                                      | Rese                | erved                          |                    | N        | 00000000    |

| 0x3C                | Max_Lat                              | Min_Gnt             | Interrupt Pin                  | Interrupt Line     | Y[7:0]   | 00 00 01 00 |

| 0x40                | PM Cap. PM Nxt Cap. PM Cap. ID       |                     | N                              | 4801 48 01         |          |             |

| 0x44                | PM Data                              | PM CSR EXT          | PM                             | CSR                | Υ        | 00 00 0000  |

| 0x48                | Reserved                             | HS CSR              | HS Nxt Cap.                    | HS Cap. ID         | Y[23:16] | 00 00 4C 06 |

| 0x4C                | VPD Address VPD Nxt Cap. VPD Cap. ID |                     | Y[31:16]                       | 0000 00 03         |          |             |

| 0x50                |                                      | VPD                 | Data                           |                    | Υ        | 00000000    |

Table 4-1: PCI9030 Header

Subsystem-ID: TPMC553-10 (32 Channels of 16 bit D/A) = 0x000A

TPMC553-11 (16 Channels of 16 bit D/A) = 0x000B

## 4.2 Local Configuration Register (LCR)

After reset, the PCI9030 Local Configuration Registers are loaded from an on board serial configuration EEPROM.

The PCI base address for the PCI9030 Local Configuration Registers is PCI9030 PCI Base Address 0 (PCI Memory Space) (Offset 0x10 in the PCI9030 PCI Configuration Register Space) or PCI9030 PCI Base Address 1 (PCI I/O Space) (Offset 0x14 in the PCI9030 PCI Configuration Register Space).

Do not change hardware dependent bit settings in the PCI9030 Local Configuration Registers.

| Offset from PCI<br>Base Address | Register                                                               | Value      |

|---------------------------------|------------------------------------------------------------------------|------------|

| 0x00                            | Local Address Space 0 Range                                            | 0xFFFFE00  |

| 0x04                            | Local Address Space 1 Range                                            | 0xFFFFFC0  |

| 0x08                            | Local Address Space 2 Range                                            | 0xFFFFFC00 |

| 0x0C                            | Local Address Space 3 Range                                            | 0x00000000 |

| 0x10                            | Expansion ROM Range                                                    | 0x00000000 |

| 0x14                            | Local Address Space 0 Local Base Address (Remap)                       | 0x00000001 |

| 0x18                            | Local Address Space 1 Local Base Address (Remap)                       | 0x00010001 |

| 0x1C                            | Local Address Space 2 Local Base Address (Remap)                       | 0x00020001 |

| 0x20                            | Local Address Space 3 Local Base Address (Remap)                       | 0x00000000 |

| 0x24                            | Expansion ROM Local Base Address (Remap)                               | 0x00000000 |

| 0x28                            | Local Address Space 0 Bus Region Descriptor                            | 0xD180A0E0 |

| 0x2C                            | Local Address Space 1 Bus Region Descriptor                            | 0xD180A0E0 |

| 0x30                            | Local Address Space 2 Bus Region Descriptor                            | 0xD180A0E0 |

| 0x34                            | Local Address Space 3 Bus Region Descriptor                            | 0x00000000 |

| 0x38                            | Expansion ROM Bus Region Descriptor                                    | 0x00000000 |

| 0x3C                            | Chip Select 0 Base Address                                             | 0x00000101 |

| 0x40                            | Chip Select 1 Base Address                                             | 0x00010041 |

| 0x44                            | Chip Select 2 Base Address                                             | 0x00020401 |

| 0x48                            | Chip Select 3 Base Address                                             | 0x00000000 |

| 0x4C                            | Interrupt Control/Status                                               | 0x0041     |

| 0x4E                            | Serial EEPROM Write-Protected Address Boundary                         | 0x0030     |

| 0x50                            | PCI Target Response, Serial EEPROM Control, and Initialization Control | 0x00780000 |

| 0x54                            | General Purpose I/O Control                                            | 0x00392270 |

| 0x70                            | Hidden1 Register for Power Management Data Select                      | 0x00000000 |

| 0x74                            | Hidden 2 Register for Power Management Data Scale                      | 0x00000000 |

Table 4-2: PCI9030 Local Configuration Registers

## 4.3 Configuration EEPROM

After power-on or PCI reset, the PCI9030 loads initial configuration register data from an on board configuration EEPROM.

The configuration EEPROM contains the following configuration data:

• Address 0x00 to 0x27 : PCI9030 PCI Configuration Register Values

• Address 0x28 to 0x87 : PCI9030 Local Configuration Register Values

• Address 0x88 to 0xFF: Reserved

See the PCI9030 Manual for more information.

| Address | Offset |        |        |        |        |        |        |        |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|

|         | 0x00   | 0x02   | 0x04   | 0x06   | 80x0   | 0x0A   | 0x0C   | 0x0E   |

| 0x00    | 0x0229 | 0x1498 | 0x0280 | 0x0000 | 0x1180 | 0x0000 | s.b.   | 0x1498 |

| 0x10    | 0x0000 | 0x0040 | 0x0000 | 0x0100 | 0x4801 | 0x4801 | 0x0000 | 0x0000 |

| 0x20    | 0x0000 | 0x0006 | 0x0000 | 0x0003 | 0x0FFF | 0xFE00 | 0x0FFF | 0xFFC0 |

| 0x30    | 0x0FFF | 0xFC00 | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0x0001 |

| 0x40    | 0x0001 | 0x0001 | 0x0002 | 0x0001 | 0x0000 | 0x0000 | 0x0000 | 0x0000 |

| 0x50    | 0xD180 | 0xA0E0 | 0xD180 | 0xA0E0 | 0xD180 | 0xA0E0 | 0x0000 | 0x0000 |

| 0x60    | 0x0000 | 0x0000 | 0x0000 | 0x0101 | 0x0001 | 0x0041 | 0x0002 | 0x0401 |

| 0x70    | 0x0000 | 0x0000 | 0x0030 | 0x0041 | 0x0078 | 0x0000 | 0x0039 | 0x2270 |

| 0x80    | 0x0000 | 0x0000 | 0x0000 | 0x0000 | 0xFFFF | 0xFFFF | 0xFFFF | 0xFFFF |

| 0x90    | 0xFFFF |

| 0xA0    | 0xFFFF |

| 0xB0    | 0xFFFF |

| 0xC0    | 0xFFFF |

| 0xD0    | 0xFFFF |

| 0xE0    | 0xFFFF |

| 0xF0    | 0xFFFF |

Table 4-3: Configuration EEPROM TPMC553-1x

Subsystem-ID Value (Offset 0x0C): TPMC553-10 0x000A

TPMC553-11 0x000B

## **4.4 Local Software Reset**

The PCI9030 Local Reset Output LRESETo# is used to reset the on board local logic.

The PCI9030 local reset is active during PCI reset or if the PCI Adapter Software Reset bit is set in the PCI9030 local configuration register CNTRL (offset 0x50).

#### CNTRL[30] PCI Adapter Software Reset:

Value of '1' resets the PCI9030 and issues a reset to the Local Bus (LRESETo# asserted). The PCI9030 remains in this reset condition until the PCI Host clears this bit. The contents of the PCI9030 PCI and Local Configuration Registers are not reset. The PCI9030 PCI Interface is not reset.

# 5 Local Space Addressing

## 5.1 PCI9030 Local Space Configuration

The local on board addressable regions are accessed from the PCI side by using the PCI9030 local spaces.

| PCI9030<br>Local<br>Space | PCI9030 PCI Base Address (Offset in PCI Configuration Space) | PCI<br>Space<br>Mapping | Size<br>(Byte) | Port<br>Width<br>(Bit) | Endian<br>Mode | Description               |

|---------------------------|--------------------------------------------------------------|-------------------------|----------------|------------------------|----------------|---------------------------|

| 0                         | 2 (0x18)                                                     | MEM                     | 512            | 32                     | BIG            | Register Space            |

| 1                         | 3 (0x1C)                                                     | MEM                     | 64             | 32                     | BIG            | DAC Data Space            |

| 2                         | 4 (0x20)                                                     | MEM                     | 1K             | 32                     | BIG            | Calibration Data<br>Space |

| 3                         | 5 (0x24)                                                     | -                       | -              | -                      | -              | Not Used                  |

Table 5-1: PCI9030 Local Space Configuration

## **5.2 Register Space**

PCI Base Address: PCI9030 PCI Base Address 2 (Offset 0x18 in PCI Configuration Space).

| Offset to PCI<br>Base Address 2 | Description                    | Size<br>(Bit) |

|---------------------------------|--------------------------------|---------------|

| 0x000                           | Q-DAC 1 Configuration Register | 32            |

| 0x004                           | Q-DAC 2 Configuration Register | 32            |

| 0x008                           | Q-DAC 3 Configuration Register | 32            |

| 0x00C                           | Q-DAC 4 Configuration Register | 32            |

| 0x010                           | Q-DAC 5 Configuration Register | 32            |

| 0x014                           | Q-DAC 6 Configuration Register | 32            |

| 0x018                           | Q-DAC 7 Configuration Register | 32            |

| 0x01C                           | Q-DAC 8 Configuration Register | 32            |

| 0x020                           | Q-DAC 1 Control Register       | 32            |

| 0x024                           | Q-DAC 2 Control Register       | 32            |

| 0x028                           | Q-DAC 3 Control Register       | 32            |

| 0x02C                           | Q-DAC 4 Control Register       | 32            |

| 0x030                           | Q-DAC 5 Control Register       | 32            |

| 0x034                           | Q-DAC 6 Control Register       | 32            |

| 0x038                           | Q-DAC 7 Control Register       | 32            |

| 0x03C                           | Q-DAC 8 Control Register       | 32            |

| 0x040                           | Q-DAC 1 Status Register        | 32            |

| 0x044                           | Q-DAC 2 Status Register        | 32            |

| Offset to PCI<br>Base Address 2 | Description                      | Size<br>(Bit) |

|---------------------------------|----------------------------------|---------------|

| 0x048                           | Q-DAC 3 Status Register          | 32            |

| 0x04C                           | Q-DAC 4 Status Register          | 32            |

| 0x050                           | Q-DAC 5 Status Register          | 32            |

| 0x054                           | Q-DAC 6 Status Register          | 32            |

| 0x058                           | Q-DAC 7 Status Register          | 32            |

| 0x05C                           | Q-DAC 8 Status Register          | 32            |

| 0x060                           | Q-DAC 1 Sequencer Timer Register | 32            |

| 0x064                           | Q-DAC 2 Sequencer Timer Register | 32            |

| 0x068                           | Q-DAC 3 Sequencer Timer Register | 32            |

| 0x06C                           | Q-DAC 4 Sequencer Timer Register | 32            |

| 0x070                           | Q-DAC 5 Sequencer Timer Register | 32            |

| 0x074                           | Q-DAC 6 Sequencer Timer Register | 32            |

| 0x078                           | Q-DAC 7 Sequencer Timer Register | 32            |

| 0x07C                           | Q-DAC 8 Sequencer Timer Register | 32            |

| 0x080                           | Clear Register                   | 32            |

| 0x084                           | Load Register                    | 32            |

| 0x088                           | Global Control Register          | 32            |

| 0x08C                           | Global Status Register           | 32            |

| 0x090                           | Interrupt Status Register        | 32            |

| 0x094                           | Auto Status Timer Register       | 32            |

Table 5-2: Register Space Address Map

The Register Space requires using 32 bit transfer size.

Registers / Register bits for Q-DACs 5 - 8 are supported for 32 D/A channel TPMC553 options only.

### 5.2.1 Q-DAC X Configuration Register (X = 1-8) (Offset 0x00 ...)

There is a dedicated Q-DAC Configuration Register for each Q-DAC.

Each Q-DAC provides four D/A Channels, internally called A - D. Each Q-DAC also provides internal registers for device configuration.

If the Q-DAC busy bit in the Global Status Register is clear, a write to a Q-DAC Configuration Register starts the Q-DAC configuration (i.e. the Q-DAC configuration register setting is transferred to the Q-DAC internal configuration registers). Each Q-DAC configuration sequence does also include a read of the Q-DAC status (see Q-DAC Status Register).

Check the Q-DAC busy bit in the Global Status Register to determine when the Q-DAC configuration is done.

Each Q-DAC that is used must be configured first. A D/A Channel can only be used if it's PUA-bit is set.

Writes to a Q-DAC Configuration Register are ignored, when the Q-DAC busy bit is set in the Global Status Register.

| Bit   | Symbol     | Description                                                                                                                                                                                                                                                   | Access | Reset<br>Value |

|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:20 | -          | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                                                             | -      | -              |

| 19    | PUD        | D/A Channel D Power-Up<br>See PUA description.                                                                                                                                                                                                                | R/W    | 0              |

| 18    | PUC        | D/A Channel C Power-Up<br>See PUA description.                                                                                                                                                                                                                | R/W    | 0              |

| 17    | PUB        | D/A Channel B Power-Up See PUA description.                                                                                                                                                                                                                   | R/W    | 0              |

| 16    | PUA        | D/A Channel A Power-Up. When set, this bit places DAC A in normal operating mode. When cleared, this bit places DAC A in power-down mode (default).                                                                                                           | R/W    | 0              |

| 15    | TSD<br>ENA | TSD Enable Set to enable the Q-DAC thermal shutdown feature. Cleared to disable the thermal shutdown feature (default). The Q-DAC incorporates a thermal shutdown feature that automatically shuts down the device if the max device temperature is exceeded. | R/W    | 0              |

| 14    | CL<br>ENA  | Clamp Enable Set to enable the current limit clamp (default). The channel current is clamped at 20mA in case of over-current. Clear to disable the current-limit clamp. The channel powers down in case of over-current.                                      | R/W    | 1              |

| Bit  | Symbol     |                           | [                                                  | Description | 1                       |     | Access | Reset<br>Value |

|------|------------|---------------------------|----------------------------------------------------|-------------|-------------------------|-----|--------|----------------|

|      |            |                           |                                                    |             | ues in case the Q-D/    | AC  |        |                |

| 13   | CLR<br>SEL | CLR<br>SEL                | Unipo<br>Output R                                  |             | Bipolar<br>Output Range |     | R/W    | 0              |

|      |            | 0                         | 0V                                                 |             | 0V                      |     |        |                |

|      |            | 1                         | Mid-so                                             | ale         | Negative Full-sca       | le  |        |                |

| 12   | -          | Reserved<br>Set '0' for v | Reserved Set '0' for writes, undefined for reads.  |             |                         |     | -      | -              |

| 11:9 | ORD        |                           | D/A Channel D Output Range<br>See ORA description. |             |                         | R/W | 000    |                |

| 8:6  | ORC        |                           | D/A Channel C Output Range<br>See ORA description. |             |                         | R/W | 000    |                |

| 5:3  | ORB        | D/A Chann<br>See ORA o    | el B Output Radescription.                         | ange        |                         |     | R/W    | 000            |

|      |            | D/A Chann                 | el A Output R                                      | ange        |                         |     |        |                |

|      |            |                           | ORA                                                | Output '    | Voltage Range           |     |        |                |

|      |            |                           | 000                                                |             | +5V                     |     |        |                |

|      |            |                           | 001                                                |             | +10V                    |     |        |                |

| 2:0  | ORA        |                           | 010                                                |             | +10.8V                  |     | R/W    | 000            |

|      |            |                           | 011                                                |             | ±5V                     |     |        |                |

|      |            |                           | 100                                                |             | ±10V                    |     |        |                |

|      |            |                           | 101                                                |             | ±10.8V                  |     |        |                |

|      |            |                           | others                                             | r           | eserved                 |     |        |                |

|      |            |                           |                                                    |             |                         |     |        |                |

Table 5-3: Q-DAC Configuration Register (Offset 0x00 ...)

## 5.2.2 Q-DAC X Control Register (X = 1-8) (Offset 0x20 ...)

| Bit   | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Access | Reset<br>Value |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:10 | -      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -      | -              |

| 9     | RDSTA  | Read Q-DAC Status Register Only valid for I-Mode and M-Mode (ignored for other QDAC modes). When set, a request for reading the Q-DAC status is logged and the status valid bit in the Q-DAC Status Register is cleared. When the Q-DAC status read is done, the Q-DAC status register is updated and the status valid bit is set again. The actual Q-DAC status read may be delayed by ongoing processes. Bit clears immediately.                                                                                                                             | W      | 0              |

| 8     | GLM    | Enable Global Load Mode for this Q-DAC Used in M-Mode only. When set, this QDAC operates in global load mode. In global load mode, all four analog outputs of the Q-DAC are updated simultaneously along with the analog outputs of other Q-DACs set to global load mode when all available D/A channel data has been transferred to the Q-DACs. When clear, this QDAC operates in standalone mode. In standalone mode, all four analog outputs of the Q-DAC are updated simultaneously when all available D/A channel data has been transferred to the Q-DAC. | R/W    | 0              |

| 7     | ASR    | Automatic Status Read Could be used for I-Mode, M-Mode and T-Mode. Set to enable automatic status reads of the Q-DAC internal status register. Clear to disable automatic status reads. See Auto Status Timer Register for I-Mode and M-Mode. In T-Mode (if enabled) there is one automatic Q-DAC status read per sequence (approx. 10us after the previous Q-DAC update).                                                                                                                                                                                     | R/W    | 0              |

| 6     | -      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -      | -              |

| 5     | IRQSE  | Q-DAC Sequencer IRQ enable. Enables Q-DAC Sequencer interrupts when set. Disables Q-DAC Sequencer interrupts when clear. See Interrupt Status Register for details.                                                                                                                                                                                                                                                                                                                                                                                            | R/W    | 0              |

| 4     | IRQAL  | Q-DAC Alert IRQ enable. Enables Q-DAC Alert interrupts when set. Disables Q-DAC Alert interrupts when clear. See Interrupt Status Register for details.                                                                                                                                                                                                                                                                                                                                                                                                        | R/W    | 0              |

| 3     | IRQLD  | Q-DAC Load IRQ enable Enables Q-DAC Load interrupt when set. Disables Q-DAC Load interrupts when clear. Should be disabled for I-Mode and T-Mode. See Interrupt Status Register for details.                                                                                                                                                                                                                                                                                                                                                                   | R/W    | 0              |

| Bit | Symbol | Description |               |                                                                                                                                              | Access                                                                                                                                  | Reset<br>Value |                                                                                                |          |  |  |

|-----|--------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------|----------|--|--|

|     |        | Q-DAC Mo    | ode           |                                                                                                                                              |                                                                                                                                         |                |                                                                                                |          |  |  |

|     |        | MODE        | Q-DAC<br>Mode | Description                                                                                                                                  |                                                                                                                                         |                |                                                                                                |          |  |  |

|     |        |             |               |                                                                                                                                              | 000                                                                                                                                     | I-Mode         | Instant Mode Q-DAC analog outputs are updated immediately after each D/A Channel data transfer |          |  |  |

| 2:0 | MODE   | 001         | M-Mode        | Manual Mode Q-DAC analog outputs are updated simultaneously per software command. D/A Channel data has been transferred to the Q-DAC before. | R/W                                                                                                                                     | 0              |                                                                                                |          |  |  |

|     |        |             |               |                                                                                                                                              |                                                                                                                                         | 010            | -                                                                                              | Reserved |  |  |

|     |        |             | 011           | T-Mode                                                                                                                                       | Timer Mode An internal sequencer timer triggers the data transfer to the Q-DAC and the simultaneous update of the Q-DAC analog outputs. |                |                                                                                                |          |  |  |

|     |        | 1xx         | -             | Reserved                                                                                                                                     |                                                                                                                                         |                |                                                                                                |          |  |  |

|     |        |             |               |                                                                                                                                              |                                                                                                                                         |                |                                                                                                |          |  |  |

Table 5-4: Q-DAC Control Register (Offset 0x20 ...)

### 5.2.3 Q-DAC X Status Register (X = 1-8) (Offset 0x40 ...)

The Q-DACs device used provides an internal status register, which is reflected in the Q-DAC X Status Registers. The Q-DAC X Status Registers are only updated when a status register read is ordered by writing a '1' to the RDSTA bit or the when ASR option is active.

| Bit   | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Access | Reset<br>Value |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:11 | -      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -      | -              |

| 10    | SVAL   | Status is valid  This bit indicates that the other register bits are showing the result of a Q-DAC status read (no random data). It does not necessarily indicate that the other register bits are showing the most current Q-DAC status.  This bit is automatically set after the first Q-DAC status read (e.g. during Q-DAC configuration). The bit is cleared upon a Q-DAC status read request via the Q-DAC control register in I-Mode or M-Mode. The bit is then automatically set again, when the requested Q-DAC status read is done. | R      | 0              |

| 9     | TSD    | Thermal Shutdown Alert In the event of an over-temperature situation, this bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 8     | PUREF  | Reference Power-Up When set, this bit indicates that the Quad-DAC internal reference is powered-up. Since the TPMC553 Quad-DACs are operating with internal reference, this bit should always be set for any status read from the Quad-DAC.                                                                                                                                                                                                                                                                                                  | R      | 0              |

| 7     | PUD    | DAC D Power-Up<br>See PUA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 6     | PUC    | DAC C Power-Up See PUA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R      | 0              |

| 5     | PUB    | DAC B Power-Up<br>See PUA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 4     | PUA    | DAC A Power-Up '0' when powered down, '1' when powered up. If the Q-DAC is configured with CL ENA bit clear, DAC A will power down automatically on detection of an over-current, PUA will be cleared to reflect this.                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 3     | OCD    | DAC D Over-current Alert See OCA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R      | 0              |

| 2     | OCC    | DAC C Over-current Alert<br>See OCA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R      | 0              |

| 1     | OCB    | DAC B Over-current Alert See OCA description.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R      | 0              |

| 0     | OCA    | DAC A Over-current Alert In the event of an over-current situation on DAC A, this bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                | R      | 0              |

Table 5-5: Q-DAC Status Register (Offset 0x40 ...)

### 5.2.4 Q-DAC X Sequencer Timer Register (X = 1-8) (Offset 0x60 ...)

| Bit   | Symbol | Description                                                                                                                                                                                  | Access | Reset<br>Value |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:24 | -      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                            | -      | -              |

| 23:0  | STPV   | Sequencer Timer Preload Value Controls the time between consecutive Q-DAC analog output updates in T-Mode. Actual time between consecutive Q-DAC analog output updates is (STPV + 1) x 10us. | R/W    | 0              |

Table 5-6: Q-DAC Sequencer Timer Register (Offset 0x60 ...)

### 5.2.5 Clear Register (Offset 0x80)

The Clear Register can be used to clear the 4 channels of a specific Q-DAC or to perform a global clear.

| Bit  | Symbol | Description                                                                                   | Access | Reset<br>Value |

|------|--------|-----------------------------------------------------------------------------------------------|--------|----------------|

| 31:8 | -      | Reserved Set '0' for writes, undefined for reads.                                             | -      | -              |

| 7    | CLR8   |                                                                                               | R/W    | 0              |

| 6    | CLR7   |                                                                                               | R/W    | 0              |

| 5    | CLR6   | There is one clear control bit for each Q-DAC.  When set, the Q-DAC clear signal is asserted. | R/W    | 0              |

| 4    | CLR5   | Could be used to set all four Q-DAC channels (internal D/A                                    | R/W    | 0              |

| 3    | CLR4   | Channel registers and analog outputs) to a value specified                                    | R/W    | 0              |

| 2    | CLR3   | by the Q-DACs CLR SEL setting (see Q-DAC Configuration Register).                             | R/W    | 0              |

| 1    | CLR2   |                                                                                               | R/W    | 0              |

| 0    | CLR1   |                                                                                               | R/W    | 0              |

Table 5-7: Clear Register (Offset 0x80)

Do not change the output voltage range while the Q-DAC clear signal is active, as this might put the analog outputs to a value other than 0V.

### 5.2.6 Load Register (M-Mode) (Offset 0x84)

The Load Register is used to load (=update) the four analog outputs of a specific Q-DAC in M-Mode.

| Bit  | Symbol | Description                                                                                                                                                                                                             | Access | Reset<br>Value |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:8 | -      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                       | -      | 1              |

| 7    | LOAD8  | Q-DAC Analog Output Update Request.                                                                                                                                                                                     | R/W    | 0              |

| 6    | LOAD7  | There is one load control/status bit for each Q-DAC.                                                                                                                                                                    | R/W    | 0              |

| 5    | LOAD6  | Only valid for M-Mode (ignored for other Q-DAC modes).                                                                                                                                                                  | R/W    | 0              |

| 4    | LOAD5  | When set, a request is logged to update the Q-DAC analog outputs. When the request has been logged, the Q-DAC                                                                                                           | R/W    | 0              |

| 3    | LOAD4  | analog outputs are updated when all available D/A Channel                                                                                                                                                               | R/W    | 0              |

| 2    | LOAD3  | data for this Q-DAC has been transferred to the Q-DAC internal data registers.                                                                                                                                          | R/W    | 0              |

| 1    | LOAD2  | If the Q-DAC is configured for Global-M-Mode, the update of                                                                                                                                                             | R/W    | 0              |

| 0    | LOAD1  | the Q-DAC analog outputs is delayed until all Q-DACs in Global-M-Mode are ready for updating their analog outputs simultaneously.  The bit is automatically cleared when the Q-DAC analog outputs are actually updated. | R/W    | 0              |

Table 5-8: Load Register (M-Mode) (Offset 0x84)

In M-Mode, after setting a LOAD-bit, software shall check that this bit is clear, before new DAC data for this Q-DAC is written to the DAC data space (since, once written to the DAC data space, the data is transferred to the Q-DAC as soon as possible and may interfere with an ongoing update of the analog outputs).

## 5.2.7 Global Control Register (Offset 0x88)

| Bit  | Symbol | Description                                                                                                                                                                                                         | Access | Reset<br>Value |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31:9 | ı      | Reserved Set '0' for writes, undefined for reads.                                                                                                                                                                   | ı      | ı              |

| 8    | MIE    | Master Interrupt Enable '0': Interrupts are disabled '1': Interrupts are enabled There are also dedicated enable/disable bits for the various interrupt sources. See Q-DAC Control Register.                        | R/W    | 0              |

| 7    | SEQST8 | Q-DAC Sequencer Start/Stop                                                                                                                                                                                          | R/W    | 0              |

| 6    | SEQST7 | There is one Sequencer Start/Stop bit for each Q-DAC.                                                                                                                                                               | R/W    | 0              |

| 5    | SEQST6 | 0 : Stop Sequencer                                                                                                                                                                                                  | R/W    | 0              |

| 4    | SEQST5 | 1 : Start Sequencer When the sequencer is running, the Q-DAC busy bit in the                                                                                                                                        | R/W    | 0              |

| 3    | SEQST4 | global status register is permanently set.                                                                                                                                                                          | R/W    | 0              |

| 2    | SEQST3 | When the sequencer is stopped, any Q-DAC data transfer in                                                                                                                                                           | R/W    | 0              |

| 1    | SEQST2 | progress will terminate normally. Check the Q-DAC busy bit in the Global Status Register to determine when the                                                                                                      | R/W    | 0              |

| 0    | SEQST1 | sequencer is actually stopped.  For a simultaneous update of the analog outputs of multiple Q-DACs in T-Mode, set the Q-DAC timer registers to the same value and start the sequencers using a single write access. | R/W    | 0              |

Table 5-9: Global Control Register (Offset 0x88)

Prior a sequencer start, the following steps are required:

- 1. Setup the Q-DAC Timer

- 2. Set the Q-DAC Mode to T-Mode

- 3. Write the Q-DAC data for the first sequence to the DAC data space.

## 5.2.8 Global Status Register (Offset 0x8C)

| Bit | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                               | Access | Reset<br>Value |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|

| 31  | SDU8   |                                                                                                                                                                                                                                                                                                                                                                                           | R/C    | 0              |

| 30  | SDR8   | Q-DAC 8 status bits.                                                                                                                                                                                                                                                                                                                                                                      | R/C    | 0              |

| 29  | SET8   | (Refer to the Q-DAC 1 status bits for description).                                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 28  | BUSY8  |                                                                                                                                                                                                                                                                                                                                                                                           | R      | 0              |

| 27  | SDU7   |                                                                                                                                                                                                                                                                                                                                                                                           | R/C    | 0              |

| 26  | SDR7   | Q-DAC 7 status bits.                                                                                                                                                                                                                                                                                                                                                                      | R/C    | 0              |

| 25  | SET7   | (Refer to the Q-DAC 1 status bits for description).                                                                                                                                                                                                                                                                                                                                       | R      | 0              |

| 24  | BUS7   |                                                                                                                                                                                                                                                                                                                                                                                           | R      | 0              |

| 23  | SDU6   |                                                                                                                                                                                                                                                                                                                                                                                           | R/C    | 0              |

| 22  | SDR6   | Q-DAC 6 status bits.                                                                                                                                                                                                                                                                                                                                                                      | R/C    | 0              |