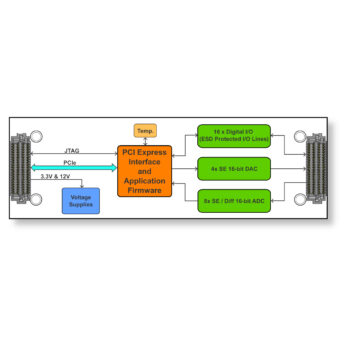

The TQMC701 is a VITA 93.0 compatible single-width QMC providing 8 channels of simultaneous sampling single ended or true differential bipolar analog inputs, 4 channels of simultaneous update analog voltage output and 16 ESD-protected 5 V tolerant TTL digital I/O lines.

The 16 bit analog input channels support per channel software configurable input modes and voltage ranges. Each channel can be operated in bipolar single-ended, unipolar single-ended and bipolar differential mode. In the single-ended modes it offers software selectable input voltage ranges of 0-5 V, 0-10 V, 0-12.5 V, ±2.5 V, ±5 V, ±6.25 V, ±10 V and ±12.5 V. In differential mode the input voltage ranges are selectable between ±5 V, ±10 V, ±12.5 V and ±20 V. Sampling rate for all channels active is up to 1 Msps.

The 16 bit analog output channels support per channel software configurable output voltage ranges of 0-5 V, 0-10 V, 0-10.8 V, ±5 V, ±10 V or ±10.8 V. The conversion time is typ. 10 μs and the DAC outputs are capable to drive a load of 2 kΩ, with a capacitance of up to 4000 pF.

All 16 digital I/O lines are ESD-protected and 5 V-tolerant. Every I/O line is individually programmable as input or output if not used for external synchronization. TTL I/O lines can be set to high, low, or tristate.

Every TQMC701 is factory calibrated. The calibration information is stored in a user-accessible on-board serial EEPROM individual to every module. The correction data values may be used to perform a hardware correction for A/D channels per input range and D/A channels per output range during functional operation.

In addition, there is a temperature sensor on every module to allow supervisory and data temperature coherence evaluation.

The TQMC701 provides different operation modes to perform manual and automatic A/D and D/A conversions.

For automatic conversions, dedicated A/D and D/A sequencer units are available. These include on-board data buffer and DMA controller for A/D data transfer, D/A data fetch and conversion rate generators.

Sequencers optionally provide a Frame Mode for repetitive frames of A/D and D/A conversions upon an internal or external trigger signal event.

Conversion clock (conversion rate) and frame trigger signals may be generated on-board for internal use. Optionally these can be provided via the I/O connector if the card is operating as a master card in a Multi-Board configuration (externally synchronization). The conversion clock (conversion rate) and frame trigger signals may also be sourced externally to be used internally.