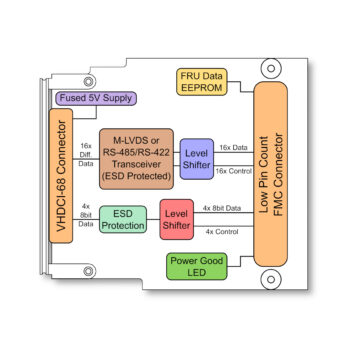

The TFMC685 is an FMC (FPGA Mezzanine Card) Mezzanine Module complying with the ANSI/VITA 57.1 standard that offers the possibility to add a 16bit M-LVDS (Multipoint Low Voltage Differential Signaling) I/O Interface or a 16bit RS-485/RS-422 I/O Interface to FMC Carrier Cards. In addition to one of these two Differential I/O standards, the TFMC685 provides four 8bit wide 5 V input tolerant 3.3 V Digital I/O Interfaces and a 5 V Supply pin (100mA) protected by a fuse.

The Low Pin Count FMC Connector provides 16 independent control signals which configure the direction of each Differential Transceiver and four independent control signals which configure the direction of each 8bit wide Digital I/O Gate.

The 16 data lines for M-LVDS or RS-485/RS-422 are routed as single-ended traces from the FMC Connector to the Differential Transceivers where they are converted into 16 differential pairs. The 32 data lines for Digital I/O are level shifted to be 5V tolerant at the front panel connector.

The TFMC685-10R meets the TIA/EIA-899 standard (Type-2 Receivers) and the TFMC685-20R meets the TIA/EIA-485 and the TIA/EIA-422 standard.

The 16 bits of Differential I/O, the 32 bits of Digital I/O and the 5 V Supply are connected to a female VHDCI-68 Connector in the front panel.

All of the 16 M-LVDS Transceivers on the TFMC685-10R support signaling rates up to 200 Mbit/s which means that a 100 MHz clock can be transmitted or in other words that 200M of voltage transitions per second can be performed. The TFMC685-10R has an on-board 100Ω termination on all 16 M-LVDS Interfaces.

All RS-485/RS-422 Transceivers on the TFMC685-20R support signaling rates up to 50 Mbit/s. The TFMC685-20R has an on-board 120Ω termination on all 16 RS-485/RS-422 Interfaces.

All signals connecting the Transceivers with the FMC Carrier are powered by an adjustable voltage generated by the Carrier. Because of voltage translation devices on the TFMC685 this voltage can range from 1.2 V to 3.6 V which allows the Carrier’s FPGA I/O cells to be configured for various different I/O standards.

The signaling standard reference voltage at pin H1 of the FMC Connector, which is powered by the TFMC685, provides half of the adjustable voltage generated by the carrier for I/O standards requiring a reference voltage.

A power good LED indicates whether the FMC Carrier has signaled that all voltages it provides to the TFMC685 are within limits.

The TFMC685 is equipped with an I2C EEPROM which acts as an IPMI resource requesting the value of the adjustable voltage, for example.

The module meets the requirements to operate in extended temperature range from -40 °C to +85 °C.