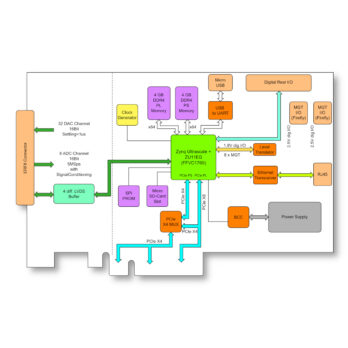

The TPCE646 is an X8 PCIe–compatible module featuring a user-configurable AMD Zynq UltraScale+™ MPSoC. It provides 32 DAC output channels based on dual 16 bit AD5547 DACs, each designed as a single-ended bipolar ±10 V analog output. The module also includes 8 ADC input channels using dual 16 bit LTC2323-16 ADCs, supporting up to 5 Msps per channel with a ±10 V input range (±20 Vpp differential).

Additionally, the TPCE646 offers four differential LVDS I/O lanes on the front I/O interface. For customer-specific I/O expansion or inter-board communication, 64 MPSoC I/Os are available on a rear connector (configurable as 64 LVCMOS18 or 32 differential LVDS), along with 8 PL multi-gigabit transceivers via two Samtec Firefly quad interfaces.

The Zynq UltraScale+ MPSoC is connected to 4 GB of 64 bit DDR4 SDRAM for both the PL and PS memory interfaces. Communication interfaces include rear I/O Ethernet, USB-to-UART via an FTDI device, and a PCIe X4 interface multiplexed with the X8 PCIe connector.

Configuration is supported via dual QSPI flash devices (in-system programmable), with optional use of AMD Tandem Configuration for PCIe compliance. A microSD card slot is available as an alternative configuration source, and JTAG provides in-circuit PL and PS debugging. Application development is supported using AMD Vivado™ and Vitis™ design tools (licenses required).