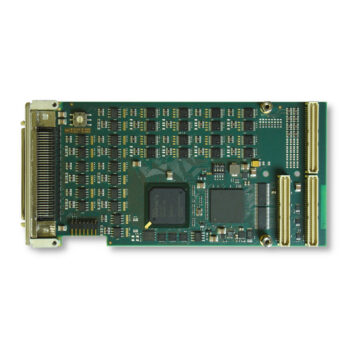

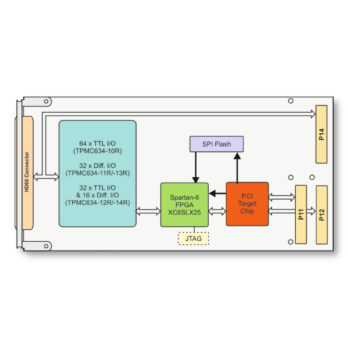

The TPMC634 is a standard single-width PMC module providing a user configurable Xilinx XC6SLX25 Spartan-6 FPGA.

The TPMC634-10R provides 64 ESD-protected TTL lines using TTL compatible buffers. The TPMC634-11R provides 32 differential I/O lines using ESD-protected EIA-422 / EIA-485 compatible line transceivers. The TPMC634-12R provides a mix of 32 TTL and 16 differential RS422/485 I/O lines. The TPMC634-13R provides 32 differential I/O lines using M-LVDS line transceivers. The TPMC634-14R provides a mix of 32 TTL and 16 differential M-LVDS I/O lines.

All I/O lines are individually programmable as input or output. The receivers are always enabled. This allows reading the state of each I/O line at any time (monitoring I/O lines configured as outputs).

Each TTL I/O line has an on-board pull resistor to a common/shared reference. The pull resistor reference is configurable by an on-board rotary switch to 3.3V, 5V or GND. The differential I/O lines have on-board termination resistors.

The User FPGA is auto-configurable by an on-board serial SPI Flash. Both the User FPGA and the SPI flash for User FPGA configuration are in-system-programmable via the PCI bus. An on-board JTAG header provides access to the user FPGA JTAG port.

PCI configuration space parameters are configurable by an on-board serial EEPROM.

| Mechanical Interface |

PCI Mezzanine Card (PMC) Interface confirming to IEEE P1386/P1386.1; Single Size |

| Electrical Interface |

PCI Rev. 3.0 compatible; 33 MHz / 32 bit PCI; Minimum PCI Clock Frequency is 8 MHz; 3.3V and 5V PCI Signaling Voltage |

| PCI Target Chip (FPGA) |

Lattice MachXO2 LCMXO2-4000HE-5BG320I |

| User Programmable FPGA |

Xilinx Spartan-6 XC6SLX25-2FGG484I |

| EEPROM |

M93C56WMN6 (or compatible) |

| SPI Flash |

Winbond W25Q32FVZPIG (W25Q32BV compatible) |

| I/O Channels |

TPMC634-10R: 64 TTL I/O

TPMC634-11R: 32 RS422/485 Differential I/O

TPMC634-12R: 32 TTL I/O and 16 RS422/485 Differential I/O

TPMC634-13R: 32 M-LVDS Differential I/O

TPMC634-14R: 32 TTL I/O and 16 M-LVDS Differential I/O |

| I/O Transceiver |

TPMC634-10R: 74LVT126 (or compatible)

TPMC634-11R: MAX3078E (or compatible)

TPMC634-12R: 74LVT126 & MAX3078E (or compatible)

TPMC634-13R: SN65MLVD206 (or compatible)

TPMC634-14R: 74LVT126 & SN65MLVD206 (or compatible) |

| I/O Connectors |

Front I/O HD68 SCSI-3 Type Connector

PMC P14 I/O (64 pin Mezzanine Connector) |

| Power Requirements 1) |

The +3.3V and ±12V from the PMC connector are not used.

On-board I/O termination resistor load included, User FPGA example application running, without any external I/O load:

150 mA to 620 mA typical @ +5V DC

Approximate values with external load on all I/O channels:

0.6 A to 1.0 A @ +5V DC |

| Temperature Range |

Operating: -40°C to +85°C

Storage: -40°C to +85°C |

| MTBF 1) |

423000 h to 440000 h |

| Humidity |

5 – 95% non-condensing |

| Weight |

84 g (all variants) |

1) depends on variant, for further details see User Manual