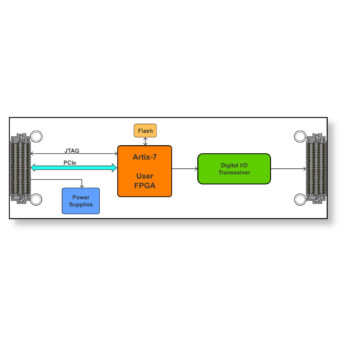

The TQMC600 is a VITA 93.0 compatible single-width QMC offering a user programmable AMD Artix™ 7 XC7A50T.

Depending on the order option, the TQMC600 offers 32 ESD-protected 5V-tolerant TTL lines or 16 differential I/O lines using ESD-protected EIA-422 / EIA-485 compatible line transceivers or Multipoint-LVDS transceivers.

All I/O lines are individually programmable as input or output. TTL I/O lines can be set to high, low, or tristate. Differential I/O lines are terminated, EIA-422 / EIA-485 lines with 120 Ω, M-LVDS lines with 100 Ω.

The User FPGA is configured by a SPI flash. An in-circuit debugging option is available via the QMC’s JTAG interface for read back and real-time debugging of the FPGA design (using the AMD Vivado™ ILA).

User applications for the TQMC600 can be developed using the AMD design stools, which can be downloaded free of charge from www.amd.com.

TEWS offers a well-documented Board Reference Design (BRD) that illustrates how to make use of the TQMC600 main functionalities. It implements a PCIe interface including register mapping and basic I/O. It comes as a Vivado Design Suite project with source code and as a ready-to-download bit stream.