FPGA DEVELOPMENT

FPGA Design and Integration Services

TEWS Technologies offers FPGA Design and Integration services for all the user programmable standard FPGA modules for XMC, PMC, CompactPCI, and mPCIe. This is especially helpful if the customer development group does not have the resources or capabilities to perform the FPGA development in a timely manner.

Our team of world class firmware experts develop all code for the TEWS’ FPGA products in house. The designs cover the entire spectrum of simple controller designs to highly integrated FPGA’s such as the AMD Zynq® UltraScale+™.

The engineering team specializes in designing highly optimized FPGA designs and has extensive experience in minimizing FPGA gate usage. Working with standard cores often leads to unnecessarily high space requirements and slower designs. Having the FPGA custom-designed according to the customer’s needs avoids overhead and delays, resulting in reduced costs for the customer.

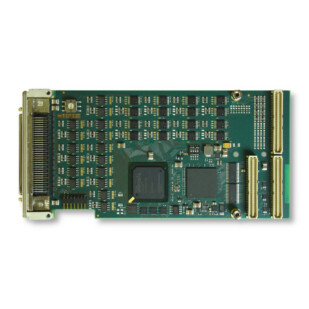

The standard blank FPGA boards offer multiple I/O choices for digital, analog, and communications physical interfaces. These TEWS’ products are the hardware base used to implement custom FPGA designs.

Premier Level AMD Embedded Partner

Since 2017, TEWS Technologies has been a member of the AMD Embedded Partner Program. As part of this partnership, our FPGA experts undergo annual certifications to ensure that our FPGA designs remain on the leading edge of the latest technology. In 2025, AMD invited TEWS Technologies to join the highest tier of the AMD Embedded Partner Program, the Premier level.